数字IC后端培训教程之数字后端项目典型项目案例解析

数字IC后端低功耗设计实现案例分享(3个power domain,2个voltage domain)

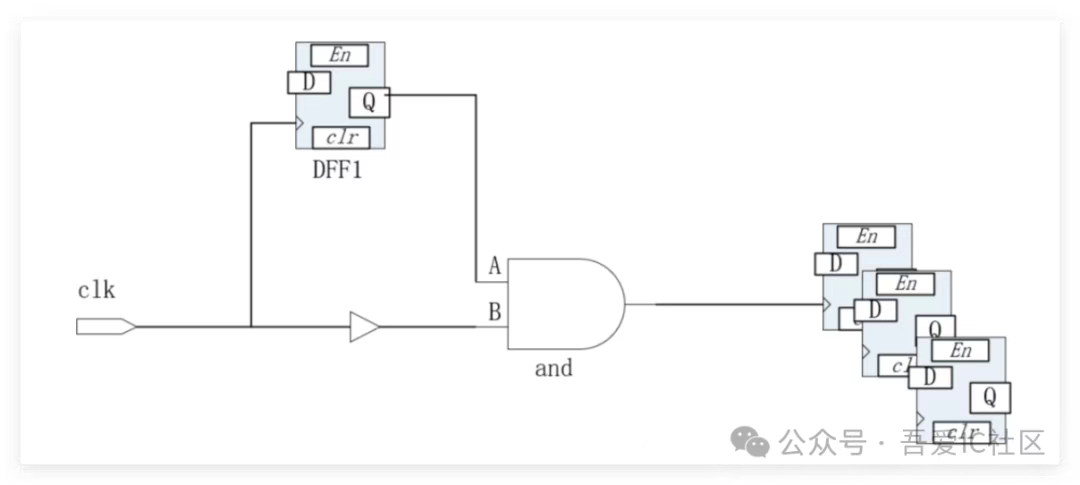

Q1: 电路如下图,clk是一个很慢的时钟test_clk(属于DFT的),DFF1与and 形成一个clock gating check。跑pr 发现,时钟树综合CTS阶段(Clock Tree Syntheis)会给and的B pin 和DFF1的CK pin插如很多cdb cell 用来balance ,我实在想不出来有什么好balance的,因为时钟很慢,setup 是没有问题的。

测试1:and 的B pin 设置ignore。结果:and 不插cdb,时钟latency做短了,但是DFF1的CK 换上插很多cdb。这可以满足我目前的需求了。

测试2:DFF1的CK pin 设置ignore,我怀疑是DFF1的latency 比较长,于是被迫造成and 被拉长。

结果:DFF1的CK pin确实不插cdb了,但是and 的B 还是插了很多cdb,完全想不明白与谁balance。

问题:innovus 长clock tree 时候,把and 不当做sink 点,不会balance的啊?sink 点应该是DFF和icg啊,为什么这里and的B 插入那么多cdb做balance啊?

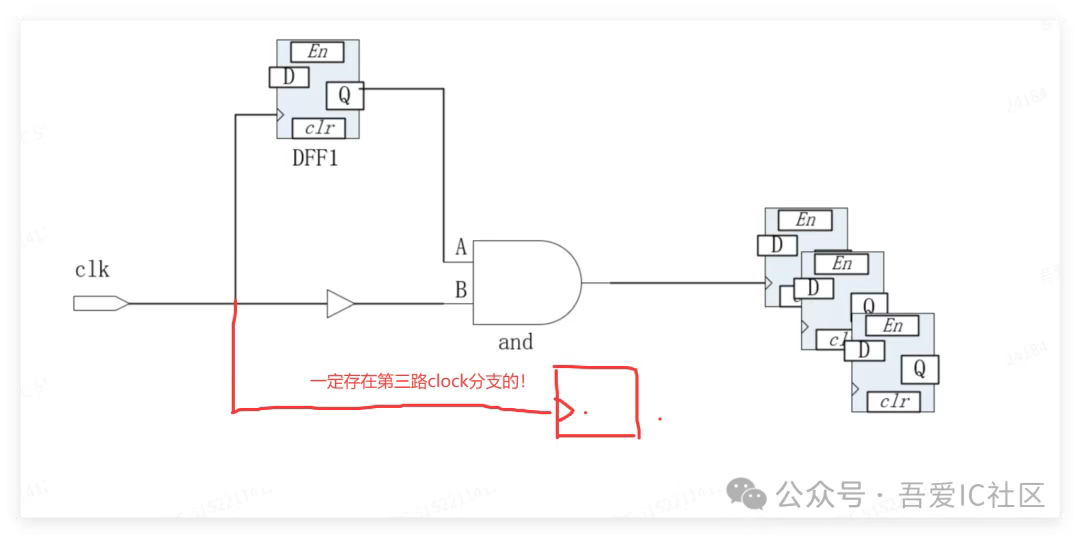

从你的两种测试结果上看,这个clk一定还有第三路clock分支,如我画出来的。其实都是被这路clock path balance的。

1)AND与门B pin设置ignore pin,仅仅是与门的B到Y这段timing arc断了,但是A pin还是会穿过与门再到后面寄存器的。

2)DFF1这颗寄存器的输出端如果没有定义任何时钟,默认情况工具做tree会自动生成clock_gen这样的skew group。如果不想自己生成这样的skew group,可以设置如下变量为false。

这个变量设置成false后,clk长时钟树只能长到DFF1的CLK pin。但这样处理后,and输出到后面寄存器CLK的这段tree就漏做了!

set_ccopt_property extract_clock_generator_skew_groups false

所以建议先把时钟结构画完整,否则是不太有利于后续的时钟树质量分析。

复杂时钟设计时钟树综合(clock tree synthesis)常见20个典型案例

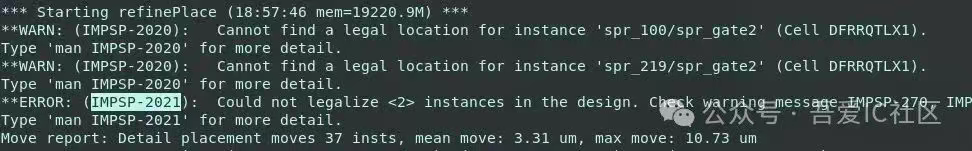

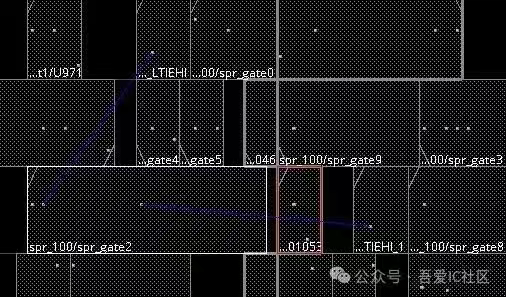

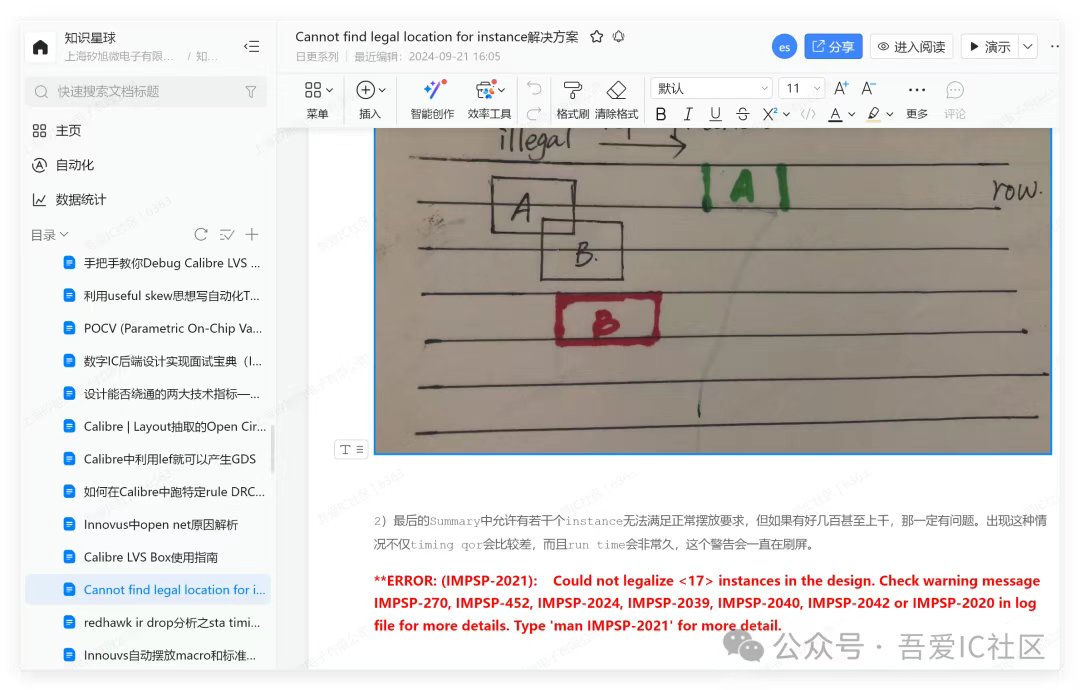

Q2: 请教一个问题,工具提示我找不到legal location 给这两个spare cell,但是select出来的结果又显示这里位置非常合理 row 正确、没有放反、没有overlap。请问还可能是什么原因呢?

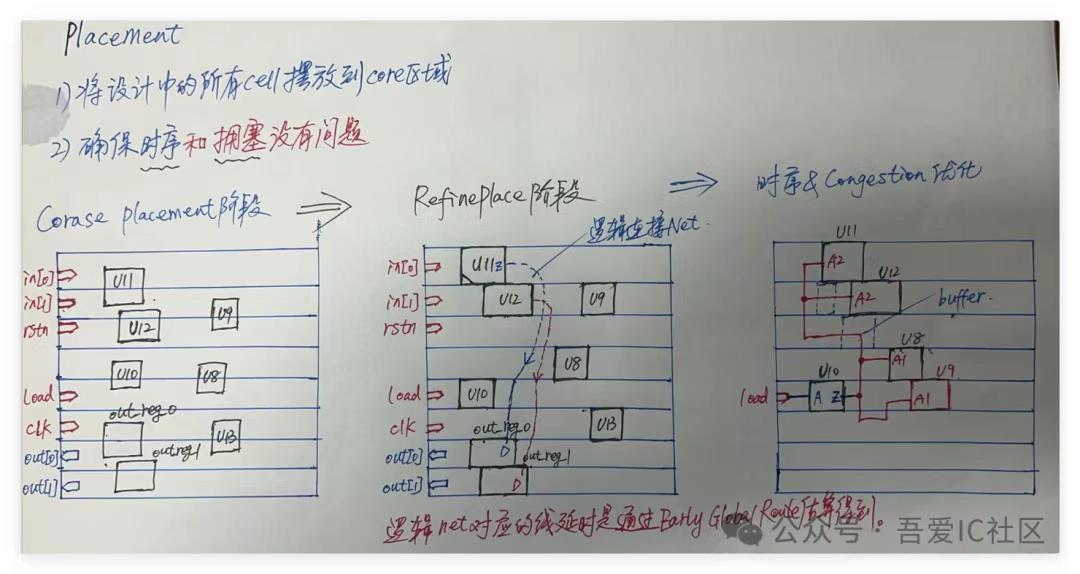

报这个警告仅仅告诉你corase placement后这颗cell在做refinePlace摆放到row时发现在以当前这个点为中心点,半径为128row高度的范围内都没找到合适的位置,即corase placement和refinePlace之间的一致性不太好。但工具仍然会在超出128row高度距离外给这颗cell找到一个位置摆放它的,摆放好后这颗cell肯定也是legal的,不会有overlap啥的。

数字IC后端实现时钟树综合系列教程 | Clock Tree,Clock Skew Group之间的区别和联系

另外建议在PR Flow和Timing ECO阶段把spare cell fixed住,不要随意参与refinePlace过程。

Q3:星主,请问一下,我跑完pr之后,reg2out的最长路径上插了将近20个buf和inv,这条路径逻辑只有四层,pr后密度60%,没有拥塞问题,路径长度1500左右,并且没有绕线,这种情况要如何去优化减少reg2out跑pr插入过多的单元?谢谢。

reg2out这个group path的effort设置成low,并且把output delay调整到比较合适的值,使得setup violation不要太大。

你这个路径上插了20个buffer,我猜测不是工具为了修max transition加入的,因为1500um的距离最多也就是插个几颗就够了。所以这里大部分buffer可能是hold buffer。

你看看这些buffer的名字是否带有PHC的关键词? 这条接口相关的timing path一定要找设计确认是否属于同步接口?只有同步接口才需要优化时序。

由于Innovus默认会开启useful skew flow,所以对于接口相关的路径切记不要开启useful skew,否则很容易有大量的hold violation。

Q4:我的模块与交接的一个模块,有高速接口检查,现在是发现我送给那个模块的时钟树做长了,请问这些路径我怎么单拎出来做短呢?

根据这些告诉接口去抓对应的寄存器,然后做tree的时候设置一个正值insertion delay。当然对于频率要求高的,我们还得把这些寄存器摆放到这个接口io port附近。

咱们训练营项目分享的这个案例跟你的情况类似。我们解决的方法就是把controller摆放至靠近phy,并且把模块内部controller这部分的clock tree尽量做短。

Q5: 老师,我在挪cell的时候不小心把IP的位置动了,然后发现IP的宽度和之前不一样了,这里会是什么原因呢?

这是一个非常典型的EDA工具bug,容易出现在Innovus 2018,2019版本中。

小编在7年前就遇到过这个bug,当时花了很多时间来debug解决掉的。

做过咱们社区IC后端训练营项目的同学都知道,我们在将PrimeTime DMSA返回来的timing eco脚本读入innovus前,会开启batchMode,这个模式可以批量处理脚本命令(ecoAddRepeater和ecoChangeCell)。

如果不开启这个batchMode,EDA工具每执行一条命令就需要做一次refinePlace,做一次RC抽取,报告一次时序!

setEcoMode -batchMode true -updateTiming false -refinePlace false

而且我们直播课也强调过这个batchMode模式仅局限于执行插buffer,换cell驱动的场景,其他情况必须把这个batchMode关闭即设置成false,否则就容易出现这个同学遇到的问题。

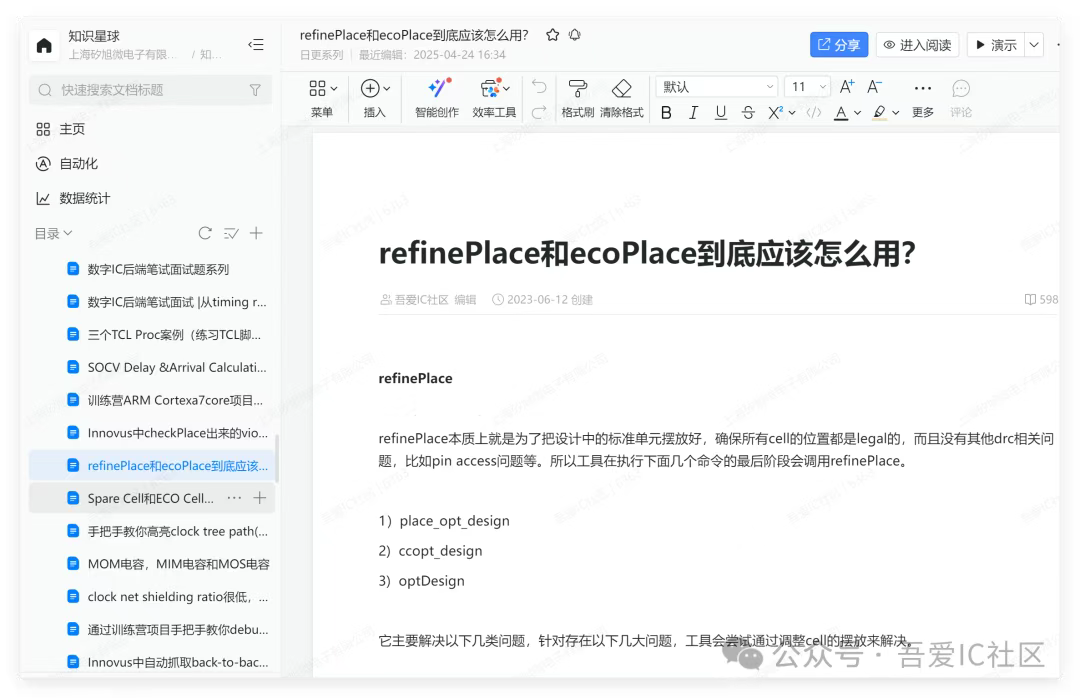

下图所示为做Timing ECO之前的子模块和顶层的部分示意图。此时子模块/IP的大小还是正常的,边上也包围着2um左右的placement halo,halo边上也加好了endcap cell(Boundary cell)。

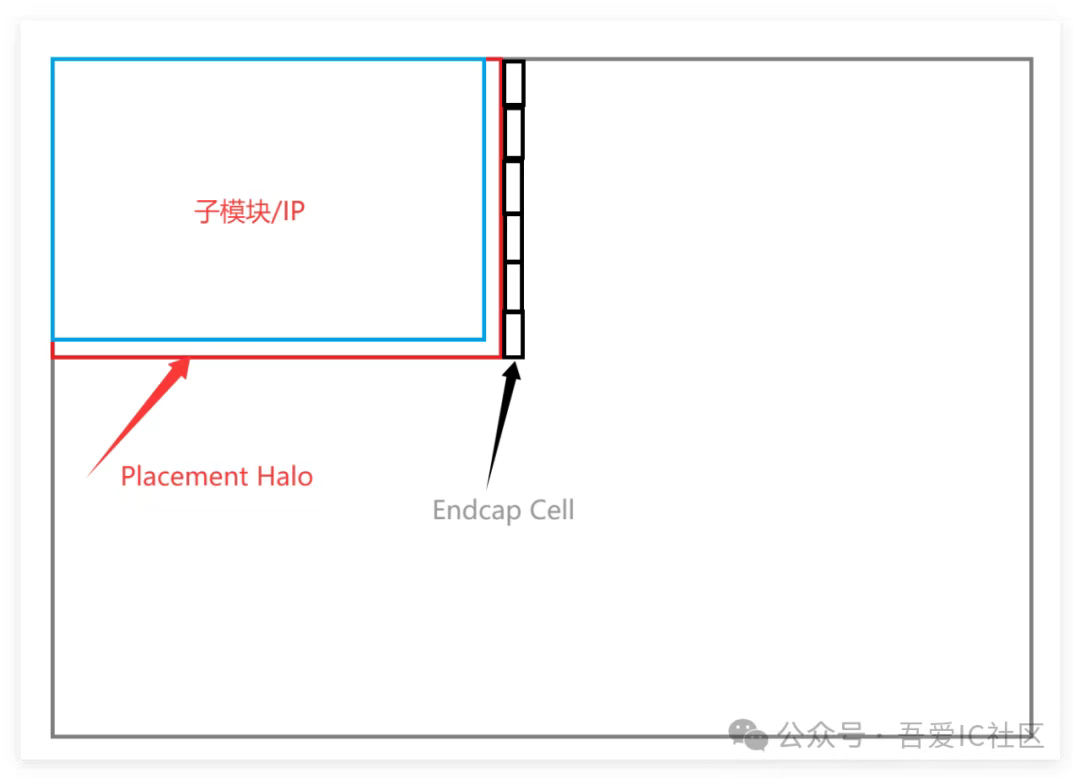

但是当这位同学做完Timing ECO后发现子模块/IP已经和现有的标准单元,endcap cell overlap了!第一次遇到这种情况肯定就不淡定了,不知道的还真以为自己挪过这个子模块/IP了。

而且牛逼的地方是当你想把这个子模块/IP调整恢复到原来位置的时候,发现回不去了,怎么调整都无法回到过去了。原因是EDA工具已经把这个子模块/IP的lef改了!

因此,batchMode开启要慎重。执行ecoAddRepeater和ecoChangeCell后必须执行下面的命令。

setEcoMode -reset

Q6:请教星主和各位前辈,现在我有一个多power domain的设计。TOP下有模块A,A的子模块为B,B的子模块为C,C中包含一些memory。对于这种设计来说,在floorplan的时候,PD之间有没有比较建议的规划方式?

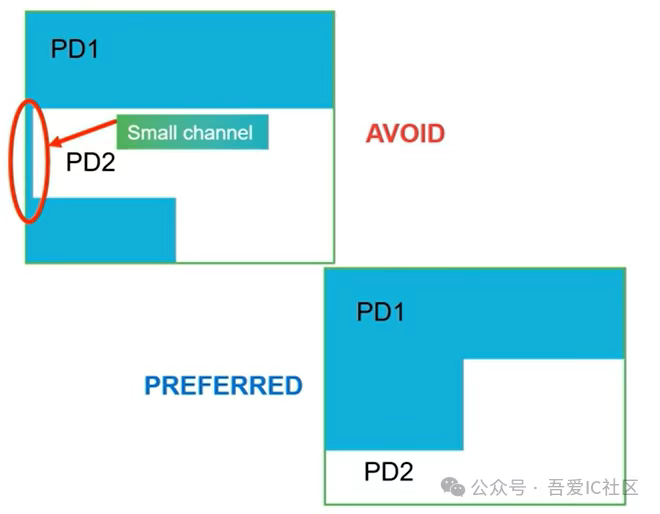

Case1: Power Domain形状尽量规则

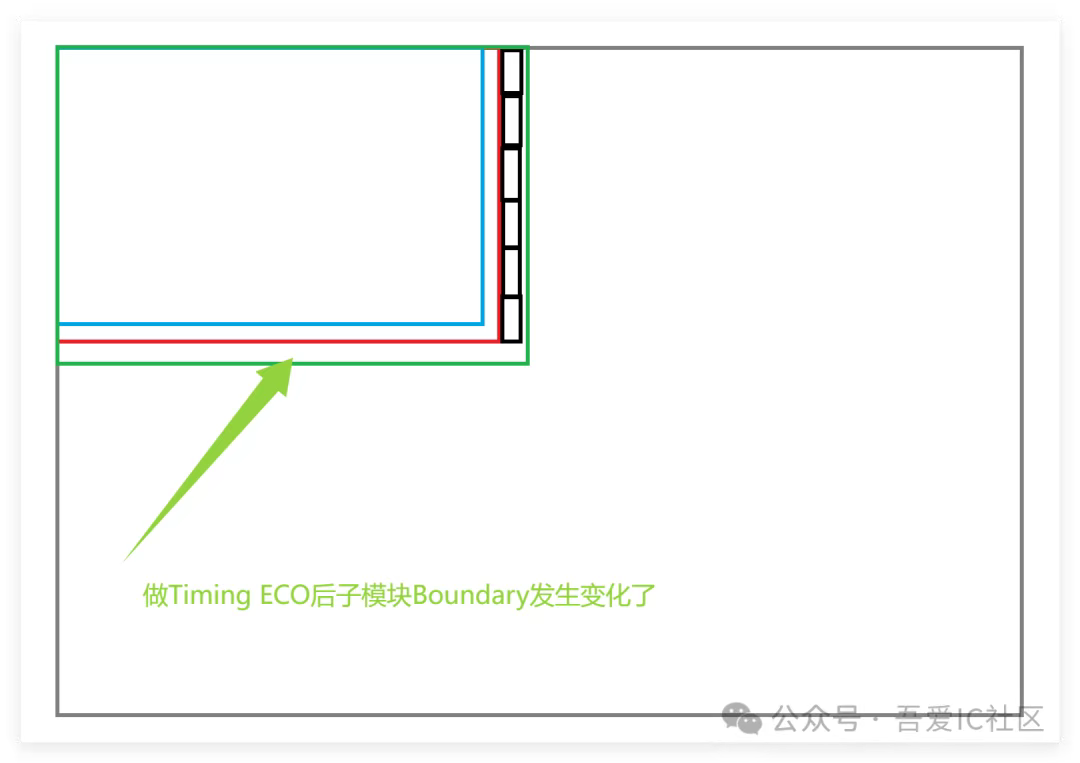

通常情况power domain的形状(子模块单独harden模块)要尽量规则,特别是timing和routing都不太好做的设计。下图左侧存在大量拐角及窄channel都是一个不好floorplan的表现。右侧所示的模块切分相对更好,但这种L型的形状在模块直角转弯处也非常容易有timing和routing问题。

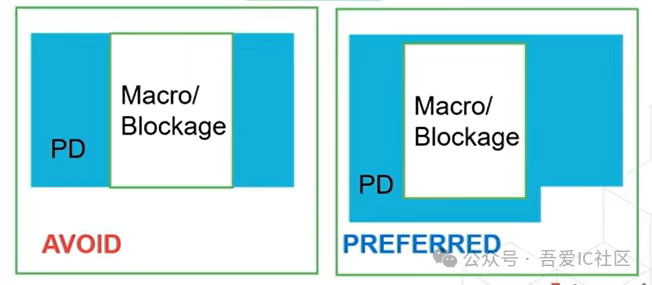

Case2: 避免Macro或Blockage放置在Power Domain中间区域

这个就是我们一直提倡的摆放Macro的方法或原则——Macro尽量摆放在模块或Power Domain的边界处。所以在做模块或Power Domain切分时需要考虑好内部Macro的情况,特别是那种宽度或高度个别大的Macro。

Case3: 避免thin channel的PD

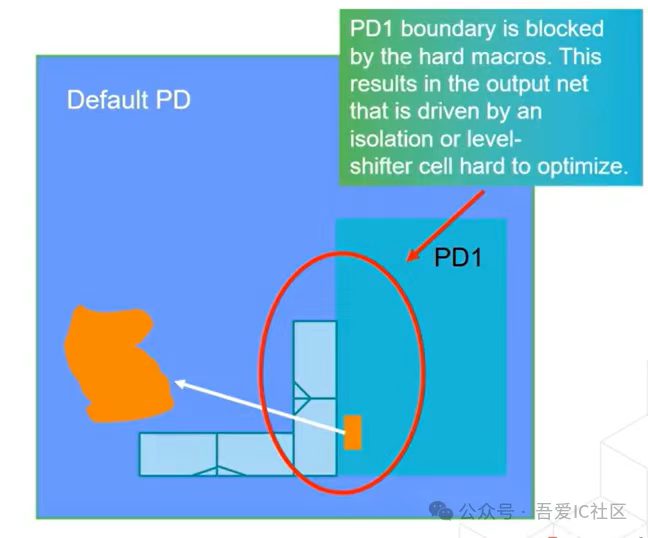

Case4: Power Domain边界处尽量不要摆放Default PD的Memory

当PD1接口信号要往左下角出来和Default PD进行交互时,PD1边界处的Macro会挡住标准单元的摆放和阻挡接口信号线的routing。

而且我们知道PD1接口出来的信号还需要插isolation cell,如果这类isolation cell被摆放至图中的黄色区域,肯定会有max transition violation。不巧的是这类信号对应的net还必须设置dont touch。

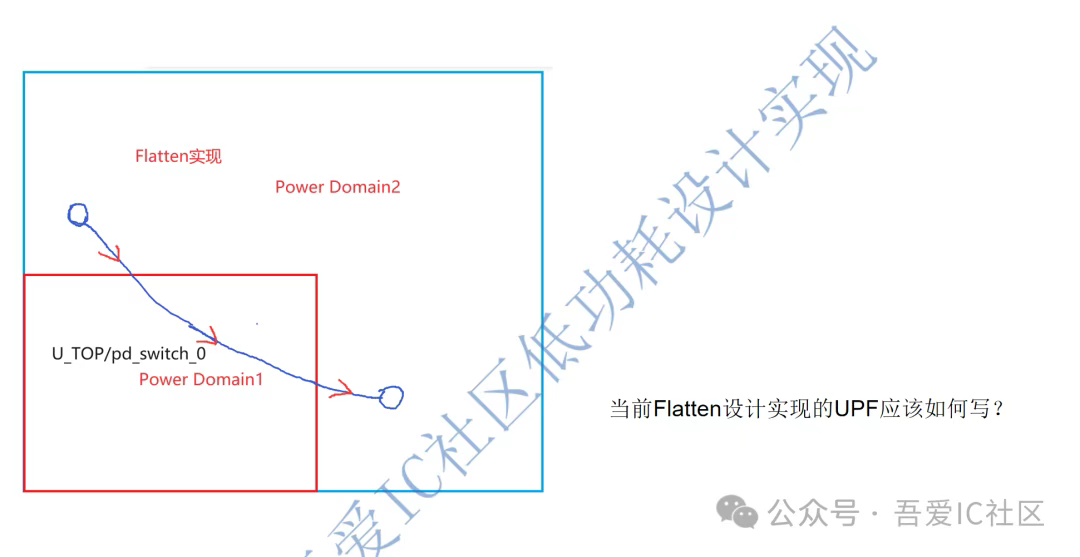

【思考题】下图所示一个低功耗设计实现案例。我们在PR实现时应该如何避免这类timing path在PD1中插buffer? 如何避免工具把这类相关net的routing跨在PD1上?