Zynq开发实践(fpga高频使用的两个场景)

【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

本身fpga是介于纯软件和asic之间的元器件。如果是纯软件,那我们要做的,就是纯上层开发。只要相关驱动已经实现,那么我们对设备的处理,就是打开、关闭、读、写、控制这五个部分。至于底层是怎么实现的,我们完全不用管。还有一种就是asic,这类就是芯片开发的范畴,虽然fpga和asic一样,都是用verilog开发,但是两者的思路是完全不一样的。前者类似于搭积木,后面则是从0到1造房子。

说了这么多,我们可以了解下,从一个嵌入式软件工程师的角度看,fpga可以帮助我们做什么。其实主要的就两部分,一个是扩展接口,一个就是算法加速或者替代。

1、扩展接口

不管是mcu也好,soc也好,外设的接口数量都是一定的。比如说uart多少个,iic多少个,spi多少个,sdio多少个等等。这样在一些特殊的场合,比如我们希望串口多一点,或者是spi多一点,基本上就没有什么办法了。要么就是选用高一级的soc,要么就是使用多颗soc来凑一个电路。两种方式虽然也可以解决问题,但是显得有点浪费资源。

但是用zynq,或者是分列式元器件,则没有这方面的困扰。原则上,只要是fpga ip支持的外设接口,要多少有多少,只要fpga的pin脚够、内部的lut表够。所以,从扩展外设接口这个角度来说,fpga还是非常合格的。

2、算法加速或替代

还有,使用fpga的目的是为了算法加速,而不是开发新的算法。这是需要注意的。也就是说,针对某一个问题,现在已经有一个算法可以解决这个问题,但是这个问题是用软件实现的,而不是硬件实现的。很多时候,虽然用软件也可以解决问题,但是效率比较低,或者软件做的时候,需要做很多无用的轮询、查找、判断的工作,这一点就不是很方便。但是,相关的工作如果用硬件实现,就会显得非常的方便。

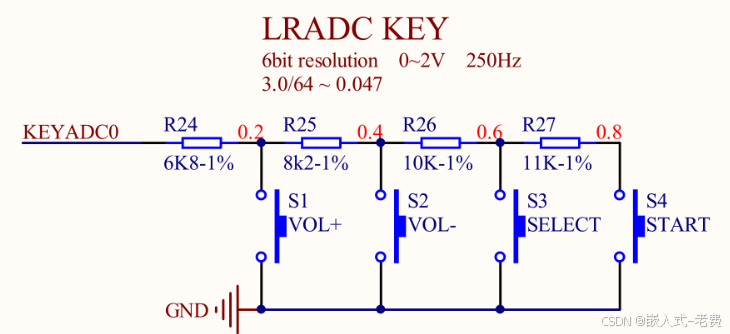

我们举一个例子来进行说明。很多soc的封装,如果不是bga,只靠qfn,其实引脚是很少的。要么是88个,要么是128个。这么多的引脚,需要的功能那么多,那么势必很多pin是复用的。针对这种情况,如果gpio比较多,我们总是希望是不是可以通过其他方式,不要占用那么多引脚就可以实现gpio输入输出,这样不会影响其他功能开发,所以大家想到了adc的方法。

从原理方面说,用adc实现按键输入是没有问题的。不同的按键按下去的时候,就会产生不同的电压。借助于这些电压,就可以判断出当前是哪个按键按下去了。但是怎么判断却是一件很麻烦的事情。

如果是软件来说,那么势必要起一个thread,这个thread的频率不能太低,不然很容易漏掉输入事件。其次,查询的时候,需要对输入数值进行滤波处理,软件来处理就是延时+均值处理。最后,获取到对应的数据之后,要及时进行上报和进行状态恢复,不要影响下一次触发。

从逻辑上说,虽然软件也能做,但是比较费cpu。相同的逻辑其实硬件也可以实现。因为fpga在后台可以一直查询,状态机切换也是很简单的事情,如果soc本身支持类似的逻辑处理,那么作为用户而言,只需要简单配置下参数就可以使用这个功能,

adc0 {adc-key-controller;channel = <0>;number_keys = <7>;vol_max = <1350>;vol_threshold = <1270>;key_vol_thre = <0 90110 290310 490510 690710 890910 10901110 1265>;}; 这也就告诉我们,很多算法不是软件不可以做,只是软件做的时候效率低,没有办法满足实时要求,或者性价比极低。这种情况下,还不如用verilog配合fpga实现来的简单和快捷。逻辑上面,其实硬件和软件差异并不是很大。