ZYNQ UART中断

一、ZYNQ UART简介

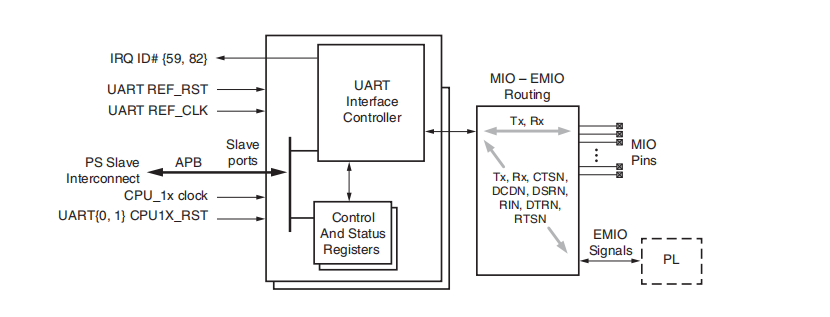

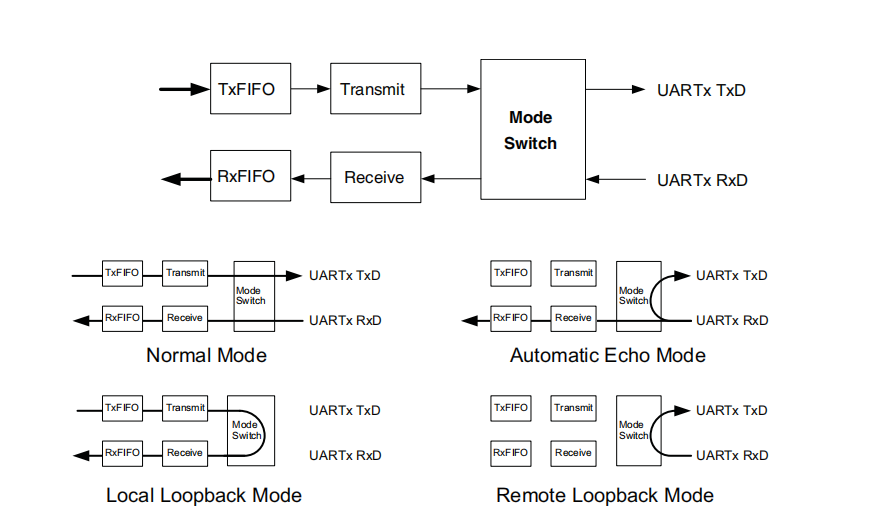

1、系统框图。

UART控制器是一个全双工异步接收和发送器,支持宽可编程波特率和I/O信号格式的范围。控制器可以容纳自动奇偶校验生成和多主检测模式。 在ZYNQ中UART操作由配置寄存器和模式寄存器控制。fifo的状态,通过状态、中断状态和调制解调器读取调制解调器信号和其他控制器功能状态寄存器。

如上图是UART控制器的系统架构。可以发现UART有两个中断号。这是因为,我们PS侧有两个串口。在前面章节对PS ZYNQ IP进行配置时发现有两个串口,UART0,UART1。这里的两个中断号分别对应两个UART。然后就是时钟,复位的配置。然后就是APB接口操控做为从机的UART的状态寄存器和控制寄存器。然后通过连接EMIO或者MIO GPIO 读取和写数据。

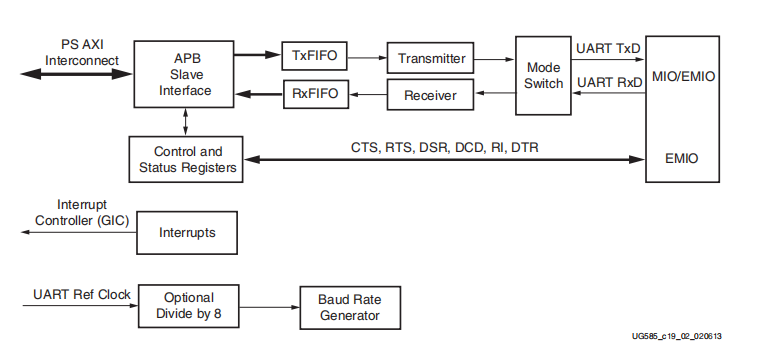

如上图是UART模块的框图。我们发现PS外部接口其实也是AXI,AXI接口对APB封装了,这样可以保持一致性,因为ZYNQ基本上都是通过AXI接口来进行数据交互的。然后连接的有两个FIFO。因此,我们就只要操作两个FIFO就行,而不用向FPGA那么麻烦去配置时钟,计算波特率对应的时钟周期等等。这里只需要间接的对FIFO进行控制,比如数据流、空、满信号等。

2、波特率

波特率相信大家已经非常熟悉了。FPGA里面也写过很多次了,这里就不过多介绍FPFA verilog代码实现的原理。这里主要是对ZYNQ PS侧操作UART波特率的介绍。

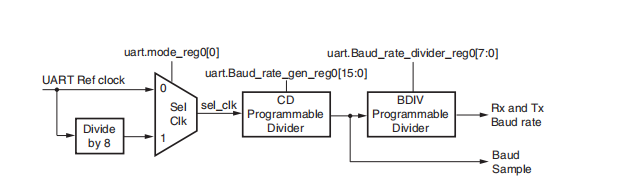

由此图可以发现,对UART控制器输入一个参考时钟,然后由一个对参考时钟的8分频时钟。通过操作寄存器操作我们的选择器选择时钟。再然后对选择的时钟通过波特率分频寄存器生成我们的波特率采样时钟和波特率。采样时钟,顾名思义是对数据采样的时钟,通过对数据采样取2中间值。对采样时钟分频寄存器配置就可以得到我们每一次的UART数据传输的采样次数。

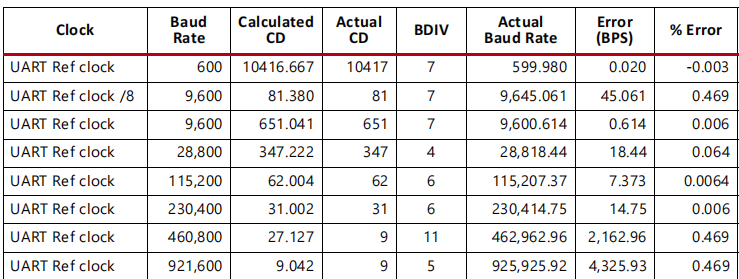

如图可以看出无论多少波特率都是有误差的,而且误差是线性的。

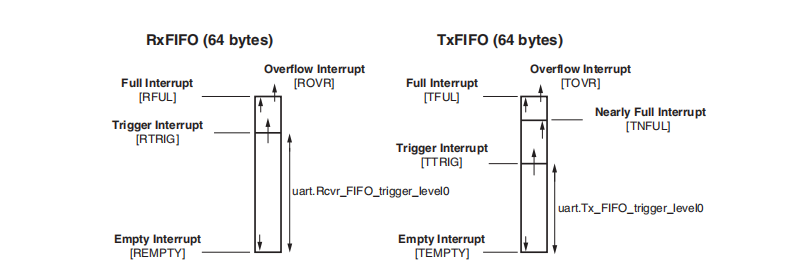

3、fifo

发送FIFO (TxFIFO)存储从APB接口写入的数据,直到它被处理器删除传输模块并加载到它的移位寄存器中。TxFIFO的最大数据宽度是8位。数据通过写入TxFIFO寄存器加载到TxFIFO中。当数据被加载到TxFIFO时,TxFIFO空标志被清除并保持在Low状态直到TxFIFO中的最后一个字被移除并加载到发送器移位寄存器中。这意味着在需要下一个数据之前,主机软件还有一个完整的串行字时间,允许它对设置的空标志作出反应,并在TxFIFO中写入另一个字而不会丢失传输时间。TxFIFO完全中断状态(full interrupt status, TFULL)表示TxFIFO已完全满并阻止任何中进一步的数据从被加载到TxFIFO。如果另一个APB写TxFIFO被执行,一个触发溢出,写数据不加载到TxFIFO。发送FIFO快满了标志(TNFULL)表示FIFO中没有足够的空闲空间再写一程序大小,由模式寄存器的WSIZE位控制。TxFIFO近满标志(TNFULL)表示TxFIFO中只有字节空闲。可以在TxFIFO填充级别上设置阈值触发器(trig)。发射机触发寄存器可以用来设置这个值,这样当TxFIFO填充级别达到这个值时就会设置触发器。RxFIFO同理,就不过多解释了。

4、模式切换

正常模式:正常模式用于标准UART操作。

自动回声模式:Echo模式接收RxD上的数据,模式切换将数据路由到接收器和设备TxD销。来自发射器的数据不能从控制器发送出去。

本地环回模式:本地环回模式不连接RxD或TxD引脚。相反,传输的数据是转回接收器。

远端环回模式:远程环回模式将RxD信号连接到TxD信号。在此模式下,控制器不能在TxD上发送任何东西,控制器也不能在RxD上接收任何东西。

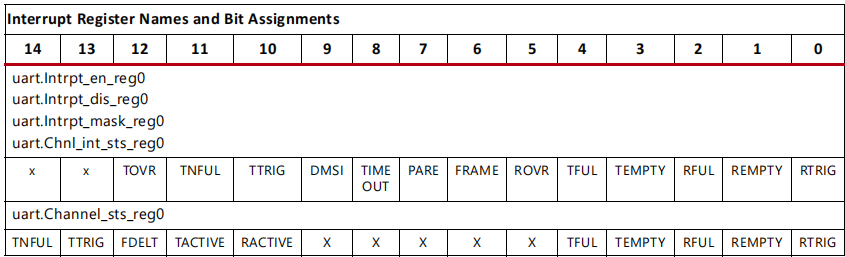

5、寄存器和中断

Intrpt_mask_reg0是一个只读的中断掩码/启用寄存器,用于掩码单个raw Chnl_int_sts_reg0寄存器中的中断:•如果掩码位= 0,中断被掩码。•如果掩码位= 1,中断被启用。这个掩码由只写的Intrpt_en_reg0和Intrpt_dis_reg0寄存器控制。每一个相关的使能/禁用中断位应该设置为互斥的(例如,要启用中断,将1写入Intrpt_en_reg0[x],将0写入Intrpt_dis_reg0[x])。其他的根据表格对比。

如上图可以看见我们可以配置三种中断类型,通过fifo信号的状态。一种是当FIFO为空时可以产生一个中断,满中断同理。还有个阈值中断,这个中断可以根据fifo里面的数据数量设置中断。

6、如何编程。

这里比较多,就不介绍了,其实也就是通过库函数操作寄存器而已。感兴趣的可以自己翻手册。

二、程序设计示例。

这里放到下一篇博客来讲。