[IMX][UBoot] 16.Linux 内核移植

目录

1.修改 Makefile

2.新增配置文件

3.新增设备树文件

4.新建编译脚本

5.修改 CPU 频率

6.EMMC 适配

7.网络驱动适配

1.修改 Makefile

修改顶层 Makefile 中的架构信息 ARCH 和交叉编译器 CROSS_COMPILE,修改后不需要在执行 make 时手动指定这两个变量的值:

# Makefile

# ARCH ?= $(SUBARCH)

# CROSS_COMPILE ?= $(CONFIG_CROSS_COMPILE:"%"=%)

ARCH ?= arm

CROSS_COMPILE ?= arm-linux-gnueabihf-2.新增配置文件

复制 arch/arm/configs 目录中的 imx_v7_mfg_defconfig 配置文件,重命名为 imx_alientek_emmc_defconfig

屏蔽其中的 CONFIG_ARCH_MULTI_V6 配置项 (禁用 ARMv6 的相关配置):

// arch/arm/configs/imx_alientek_emmc_defconfig

# CONFIG_BLK_DEV_BSG is not set

# CONFIG_ARCH_MULTI_V6=y

CONFIG_ARCH_MXC=y

# CONFIG_MACH_MX31ADS is not set执行以下命令编译配置文件,生成 .config 配置文件:

make imx_alientek_emmc_defconfig3.新增设备树文件

基于 EVK 开发板的设备树 imx6ull-14x14-evk.dts 进行修改,复制该设备树并命名为 imx6ull-alientek-emmc.dts

将 imx6ull-alientek-emmc.dts 中的 usdhc2 节点 (EMMC) 替换为 arch/arm/boot/dts/imx6ull-14x14-evk-emmc.dts 中的 usdhc2 节点:

// arch/arm/boot/dts/imx6ull-alientek-emmc.dts

&usdhc2 {pinctrl-names = "default", "state_100mhz", "state_200mhz";pinctrl-0 = <&pinctrl_usdhc2_8bit>;pinctrl-1 = <&pinctrl_usdhc2_8bit_100mhz>;pinctrl-2 = <&pinctrl_usdhc2_8bit_200mhz>;bus-width = <8>;non-removable;status = "okay";

};在 arch/arm/boot/dts/Makefile 中新增正点原子开发板的设备树编译配置项:

# arch/arm/boot/dts/Makefile

dtb-$(CONFIG_SOC_IMX6ULL) += \...imx6ull-alientek-emmc.dtb4.新建编译脚本

新建编译脚本 build.sh:

#!/bin/bash

make ARCH=arm CROSS_COMPILE=arm-linux-gnueabihf- distclean

make ARCH=arm CROSS_COMPILE=arm-linux-gnueabihf- imx_alientek_emmc_defconfig

make ARCH=arm CROSS_COMPILE=arm-linux-gnueabihf- -j8为该脚本赋予可执行权限:

chmod +x build.sh运行脚本进行编译:

./build.sh5.修改 CPU 频率

/sys/bus/cpu/devices/cpu0/cpufreq 目录中保存了 CPU 频率相关的文件,这些文件的含义如下:

-

cpuinfo_cur_freq:当前 CPU 的工作频率,从 CPU 寄存器读取的工作频率;

-

cpuinfo_max_freq:处理器所能运行的最高工作频率 (单位 KHz);

-

cpuinfo_min_freq:处理器所能运行的最低工作频率 (单位 KHz);

-

cpuinfo_transition_latency:处理器切换频率所需时间 (单位 ns);

-

scaling_available_frequencies:处理器支持的频率列表 (单位 KHz);

-

scaling_available_governors:内核支持的所有 governor 调频类型;

-

scaling_cur_freq:保存 cpufreq 模块缓存的当前 CPU 频率,不会对 CPU 硬件寄存器进行检查;

-

scaling_driver:保存当前 CPU 所使用的调频驱动;

-

scaling_governor:governor 调频策略,Linux 支持以下调频策略:

-

Performance:最高性能,直接使用最高频率,不考虑耗电;

-

Interactive:一开始使用最高频率,然后根据 CPU 负载慢慢降低;

-

Powersave:省电模式,通常以最低频率运行,系统性能会受影响,一般不使用;

-

Userspace:可以在用户空间手动调节频率;

-

Ondemand:定时检查负载,并根据负载调节频率,低负载时降低 CPU 频率,高负载时提高 CPU 频率;

-

-

scaling_max_freq:governor 调频可设置的最高频率;

-

cpuinfo_min_freq:governor 调频可设置的最低频率;

/sys/devices/system/cpu/cpu0/cpufreq/stats 目录中包含 CPU 运行频率的统计情况,例如 CPU 在各个频率下的运行时间及变频次数,使用以下命令查看 CPU 当前频率:

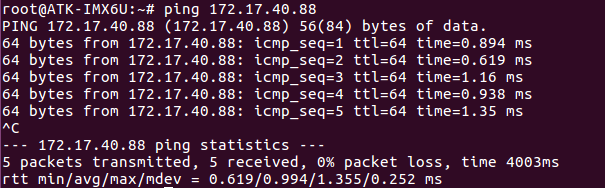

cat cpuinfo_cur_freq从中可以看出当前 CPU 的工作频率为 792MHz:

![]()

通过 scaling_available_frequencies 文件查看 CPU 支持的工作频率:

![]()

可以看出当前 CPU 支持的工作频率为:198MHz、396MHz、528MHz 和 792MHz

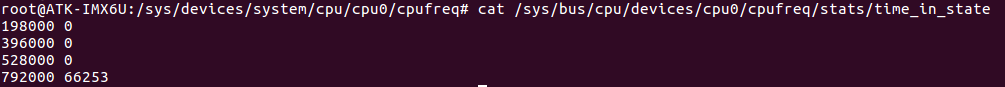

通过查看 /stats 目录下的 time_in_state 文件,可以获取 CPU 在各频率下的工作时间,命令如下:

cat /sys/bus/cpu/devices/cpu0/cpufreq/stats/time_in_state

通过修改 imx_alientek_emmc_defconfig 配置文件,设置 CPU 的调频策略:

// arch/arm/configs/imx_alientek_emmc_defconfig

CONFIG_CPU_FREQ_GOV_POWERSAVE=y

CONFIG_CPU_FREQ_GOV_USERSPACE=y

CONFIG_CPU_FREQ_GOV_ONDEMAND=y

CONFIG_CPU_FREQ_GOV_CONSERVATIVE=y在其中添加 CONFIG_CPU_FREQ_DEFAULT_GOV_ONDEMAND=y 设置默认的调频策略为 ONDEMAND:

// arch/arm/configs/imx_alientek_emmc_defconfig

CONFIG_CPU_FREQ_DEFAULT_GOV_ONDEMAND=y

CONFIG_CPU_FREQ_GOV_POWERSAVE=y

CONFIG_CPU_FREQ_GOV_USERSPACE=y

CONFIG_CPU_FREQ_GOV_ONDEMAND=y

CONFIG_CPU_FREQ_GOV_CONSERVATIVE=y6.EMMC 适配

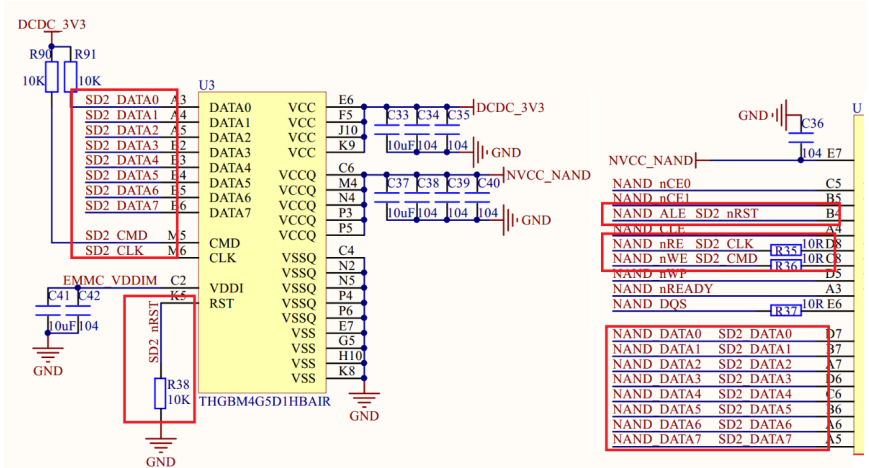

正点原子 IMX6ULL 开发板的 EMMC 支持 8-bit 总线位宽,EVK 开发板默认使用 4-bit 的位宽,需要修改 EMMC 对应的 usdhc2 节点,硬件原理图如下所示:

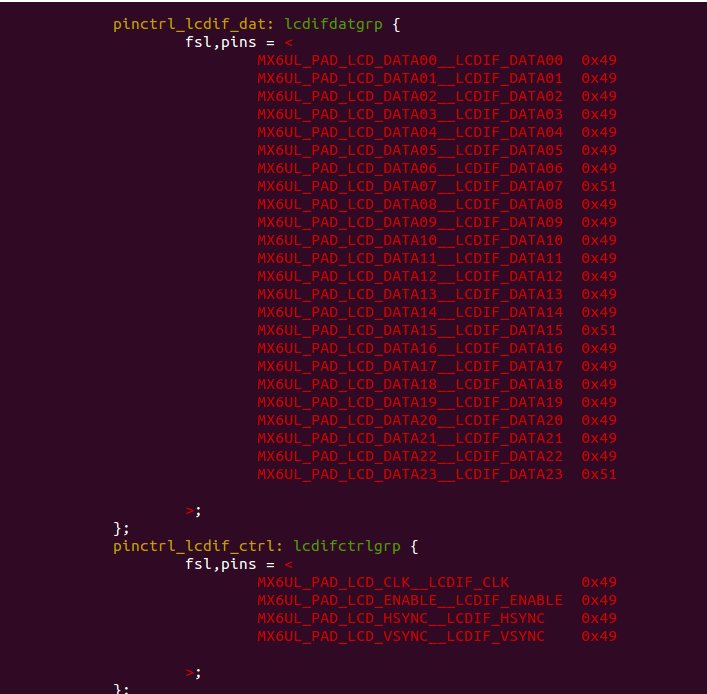

设备树中 EMMC 模块的引脚定义如下:

// arch/arm/boot/dts/imx6ull-alientek-emmc.dtspinctrl_usdhc2_8bit: usdhc2grp_8bit {fsl,pins = <MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x10069MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x17059MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x17059MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x17059MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x17059MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x17059MX6UL_PAD_NAND_DATA04__USDHC2_DATA4 0x17059MX6UL_PAD_NAND_DATA05__USDHC2_DATA5 0x17059MX6UL_PAD_NAND_DATA06__USDHC2_DATA6 0x17059MX6UL_PAD_NAND_DATA07__USDHC2_DATA7 0x17059>;};pinctrl_usdhc2_8bit_100mhz: usdhc2grp_8bit_100mhz {fsl,pins = <MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x100b9MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x170b9MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x170b9MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x170b9MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x170b9MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x170b9MX6UL_PAD_NAND_DATA04__USDHC2_DATA4 0x170b9MX6UL_PAD_NAND_DATA05__USDHC2_DATA5 0x170b9MX6UL_PAD_NAND_DATA06__USDHC2_DATA6 0x170b9MX6UL_PAD_NAND_DATA07__USDHC2_DATA7 0x170b9>;};pinctrl_usdhc2_8bit_200mhz: usdhc2grp_8bit_200mhz {fsl,pins = <MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x100f9MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x170f9MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x170f9MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x170f9MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x170f9MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x170f9MX6UL_PAD_NAND_DATA04__USDHC2_DATA4 0x170f9MX6UL_PAD_NAND_DATA05__USDHC2_DATA5 0x170f9MX6UL_PAD_NAND_DATA06__USDHC2_DATA6 0x170f9MX6UL_PAD_NAND_DATA07__USDHC2_DATA7 0x170f9>;};一共定义了三组引脚,分别为默认引脚配置、100MHz 引脚配置、200MHz 引脚配置,引脚相关的配置项由 drivers/pinctrl/freescale/pinctrl-imx.c 文件中的 imx_pinctrl_parse_groups() 函数负责解析

在设备树中修改 EMMC 对应的节点信息:

-

pinctrl-names 为每组引脚的名称:default、state_100mhz、state_200mhz;

-

pinctrl-x (x = 0~2) 为对应的三组引脚;

-

bus-width 为总线位宽 (8-bit);

-

non-removable 表示该节点的引脚不支持热插拔;

-

no-1-8-v 表示不要使用 1.8V 的电压驱动 EMMC (驱动电压应该为 3.3V);

-

status 表示引脚状态,okay 表示使能;

// arch/arm/boot/dts/imx6ull-alientek-emmc.dts

&usdhc2 {pinctrl-names = "default", "state_100mhz", "state_200mhz";pinctrl-0 = <&pinctrl_usdhc2_8bit>;pinctrl-1 = <&pinctrl_usdhc2_8bit_100mhz>;pinctrl-2 = <&pinctrl_usdhc2_8bit_200mhz>;bus-width = <8>;non-removable;no-1-8-v;status = "okay";

};配置完成后将 EMMC 的总线位宽设置为 8-bit,并设置了对应的引脚,同时新增禁止 1.8V 驱动的配置项

7.网络驱动适配

EVK 开发板的 PHY 芯片为 KSZ8081,正点原子开发板的 PHY 芯片为 LAN8720A,需要修改相关引脚

ENET1 的复位引脚 ENET1_RST 与 SoC 的 SNVS_TAMPER7 引脚连接

ENET2 的复位引脚 ENET2_RST 与 SoC 的 SNVS_TAMPER8 引脚连接

EVK 开发板将这两个引脚用于 SPI4,因此需要在对应的节点中将其删除,解除引脚占用:

// arch/arm/boot/dts/imx6ull-alientek-emmc.dtspinctrl_spi4: spi4grp {fsl,pins = <......MX6ULL_PAD_SNVS_TAMPER7__GPIO5_IO07 0x70a1MX6ULL_PAD_SNVS_TAMPER8__GPIO5_IO08 0x80000000>;};在 SPI4 的节点中将引脚引用删除:

// arch/arm/boot/dts/imx6ull-alientek-emmc.dtsspi4 {...pinctrl-assert-gpios = <&gpio5 8 GPIO_ACTIVE_LOW>;...cs-gpios = <&gpio5 7 0>;...};在 iomuxc_snvs 节点中添加复位引脚:

// arch/arm/boot/dts/imx6ull-alientek-emmc.dts

&iomuxc_snvs {...pinctrl_enet1_reset: enet1resetgrp {fsl,pins = <MX6ULL_PAD_SNVS_TAMPER7__GPIO5_IO07 0x10B0>;};pinctrl_enet2_reset: enet2resetgrp {fsl,pins = <MX6ULL_PAD_SNVS_TAMPER8__GPIO5_IO08 0x10B0>;};修改时钟引脚,将时钟引脚的配置值由 0x4001b031 修改为 0x4001b009:

// arch/arm/boot/dts/imx6ull-alientek-emmc.dtspinctrl_enet1: enet1grp {fsl,pins = <...MX6UL_PAD_ENET1_TX_CLK__ENET1_REF_CLK1 0x4001b009>;};pinctrl_enet2: enet2grp {fsl,pins = <...MX6UL_PAD_ENET2_TX_CLK__ENET2_REF_CLK2 0x4001b009>;};修改 FEC1 和 FEC2 节点的 pinctrl-0 属性,添加复位引脚,低电平有效,复位时长 200ms:

// arch/arm/boot/dts/imx6ull-alientek-emmc.dts

&fec1 {...pinctrl-0 = <&pinctrl_enet1&pinctrl_enet1_reset>;...phy-reset-gpios = <&gpio5 7 GPIO_ACTIVE_LOW>;phy-reset-duration = <200>;

};&fec2 {...pinctrl-0 = <&pinctrl_enet2&pinctrl_enet2_reset>;...phy-reset-gpios = <&gpio5 8 GPIO_ACTIVE_LOW>;phy-reset-duration = <200>;ENET1 的 LAN8720A 地址为 0x0,ENET2 的 LAN8720A 地址为 0x1,在设备树中修改:

// arch/arm/boot/dts/imx6ull-alientek-emmc.dts

&fec2 {...mdio {...ethphy0: ethernet-phy@0 {...smsc,disable-energy-detect;reg = <0>;};ethphy1: ethernet-phy@1 {...smsc,disable-energy-detect;reg = <1>;};属性 smsc,disable-energy-detect 表示 PHY 芯片属于 SMSC,Linux 会根据该属性查找对应的驱动

drivers/net/ethernet/freescale/fec_main.c 中修改 fec_probe() 函数,添加引脚复位操作:

// drivers/net/ethernet/freescale/fec_main.c

static int

fec_probe(struct platform_device *pdev)

{...void __iomem *IMX6U_ENET1_TX_CLK;void __iomem *IMX6U_ENET2_TX_CLK;IMX6U_ENET1_TX_CLK = ioremap(0X020E00DC, 4);writel(0X14, IMX6U_ENET1_TX_CLK);IMX6U_ENET2_TX_CLK = ioremap(0X020E00FC, 4);writel(0X14, IMX6U_ENET2_TX_CLK);在配置文件 arch/arm/configs/imx_alientek_emmc_defconfig 中添加 SMSC PHY 使能配置项,同时注释 AT803 PHY 的配置项:

// arch/arm/configs/imx_alientek_emmc_defconfig

CONFIG_SMSC_PHY=y# CONFIG_AT803X_PHY=y在 drivers/net/phy/smsc.c 中新增复位操作:

// drivers/net/phy/smsc.c

#include <linux/of_gpio.h>

#include <linux/io.h>

...

static int smsc_phy_reset(struct phy_device *phydev)

{int err, phy_reset;int msec = 1;struct device_node *np;int timeout = 50000;if(phydev->addr == 0) /* FEC1 */ {np = of_find_node_by_path("/soc/aips-bus@02100000/ethernet@02188000");if(np == NULL) {return -EINVAL;}}if(phydev->addr == 1) /* FEC2 */ {np = of_find_node_by_path("/soc/aips-bus@02000000/ethernet@020b4000");if(np == NULL) {return -EINVAL;}}err = of_property_read_u32(np, "phy-reset-duration", &msec);/* A sane reset duration should not be longer than 1s */if (!err && msec > 1000)msec = 1;phy_reset = of_get_named_gpio(np, "phy-reset-gpios", 0);if (!gpio_is_valid(phy_reset))return;gpio_direction_output(phy_reset, 0);gpio_set_value(phy_reset, 0);msleep(msec);gpio_set_value(phy_reset, 1);int rc = phy_read(phydev, MII_LAN83C185_SPECIAL_MODES);if (rc < 0)return rc;/* If the SMSC PHY is in power down mode, then set it* in all capable mode before using it.*/if ((rc & MII_LAN83C185_MODE_MASK) == MII_LAN83C185_MODE_POWERDOWN) {/* set "all capable" mode and reset the phy */rc |= MII_LAN83C185_MODE_ALL;phy_write(phydev, MII_LAN83C185_SPECIAL_MODES, rc);}phy_write(phydev, MII_BMCR, BMCR_RESET);/* wait end of reset (max 500 ms) */do {udelay(10);if (timeout-- == 0)return -1;rc = phy_read(phydev, MII_BMCR);} while (rc & BMCR_RESET);return 0;

}网络配置完成后终端显示如下信息:

fec 20b4000.ethernet eth0: Link is Up - 100Mbps/Full - flow control rx/tx

IPv6: ADDRCONF(NETDEV_CHANGE): eth0: link becomes ready

fec 20b4000.ethernet eth0: Link is Down

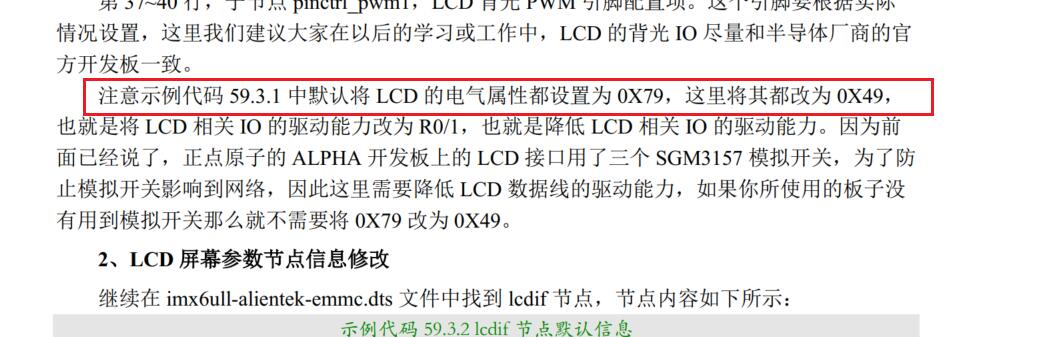

IPv6: ADDRCONF(NETDEV_UP): eth0: link is not ready 这是因为网口引脚和屏幕引脚存在复用,屏幕上有三个电阻用于识别屏幕,导致引脚驱动能力不足,需要修改设备树中屏幕相关引脚的驱动能力,相关文章链接:http://www.openedv.com/forum.php?mod=viewthread&tid=322548

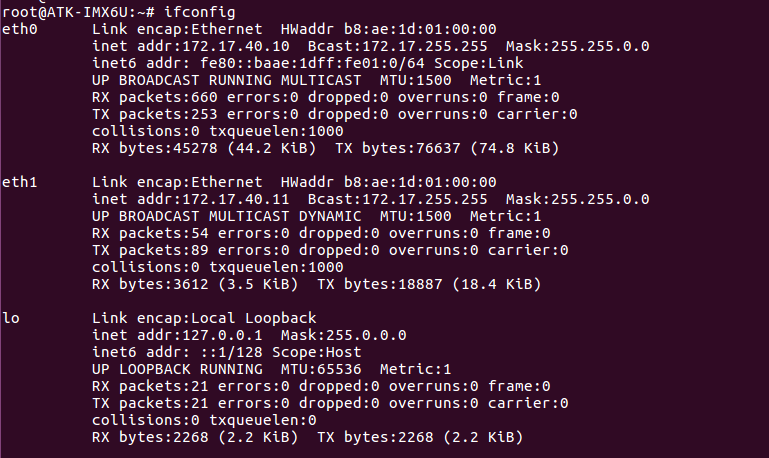

修改完成后查看网口是否存在:

修改网口的 IP 地址:

ifconfig eth0 172.17.40.88ping 虚拟机检查是否可以通信: