【IC_Design】跨时钟域的寄存器更新后锁存

目录

- 设计逻辑框图

- 场景概述

- 总结

- 电路使用注意事项***

- 波形图

- 代码

设计逻辑框图

场景概述

最典型的应用场景就是——在一个时钟域(比如 CPU/总线域)更新了一个多位配置字,需要把它安全地送到另一个时钟域(比如时钟发生器、串口、视频/以太网 MAC 等域)并原子性地应用。下面举几个具体例子说明:

UART 波特率预分频器(baud‐rate prescaler)

- 场景:CPU 通过 APB/APB3 总线写入一个 8~16bit 的波特率分频值 Prescale,UART 收发逻辑在它自己的时钟域里工作。

问题:写寄存器和串口时钟域不同步,直接并行送入会出现中间态,导致波特率跑飞或抖动。 - 解决:用上面这套逻辑

CPU 域计算 clk_div_load = |(new_prescale ^ cur_prescale)

同步到 UART 时钟域,生成一拍脉冲 clk_chg_done

UART 时钟域在 clk_chg_done 那一拍将 cur_prescale <= new_prescale - 效果:保证 Prescaler 在一个确定时刻“原子”更新,无抖动。

动态时钟发生器/PLL 分频器重配置

- 场景:FPGA 内的时钟管理单元(MMCM/PLL)允许在运行时修改输出分频比或相位偏移,控制逻辑在系统主时钟域。

- 问题:PLL 配置寄存器在专用域,修改要安全地“拍入”到 PLL 核心电路时钟域。

- 方案:正好套用上述跨域更新逻辑,避免在分频器内部出现瞬态分频比或相位错误。

异步 FIFO 的读/写指针同步

- 场景:在高-速串行收发或多通道数据流里,读指针在读时钟域更新,写指针在写时钟域更新。需要把它们互相传递来判断“空/满”状态。

- 经典做法:Gray code + 双级同步器,但 Gray code 只是单个位走变;如果是多位二进制指针,也可以先做“位翻转检测”(XOR+OR)、单比特同步+上升沿脉冲,让目标域在脉冲来时整并新的写地址。

动态电压/频率调度(DVFS)寄存器

- CPU 或电源管理 IC 在一个域写入目标频率、分频或电压等级字段,而真正的调度逻辑在另一个“电源管理时钟”域。

同样需要一整套安全的跨时钟域更新流程。

总结

这套逻辑最大的特点是:

- 对多位并行配置字用 X ^ Y + “或归约” 检测任何位变化;

- 再用两级(或 N 级)同步链 + 上升沿检测,生成单时钟脉冲;

- 由脉冲驱动目标域寄存器原子更新。

它既能避免位间瞬态,又能自动清除“load”标志,常见于各类需要运行时动态重配置、跨时钟域的控制/配置场景。

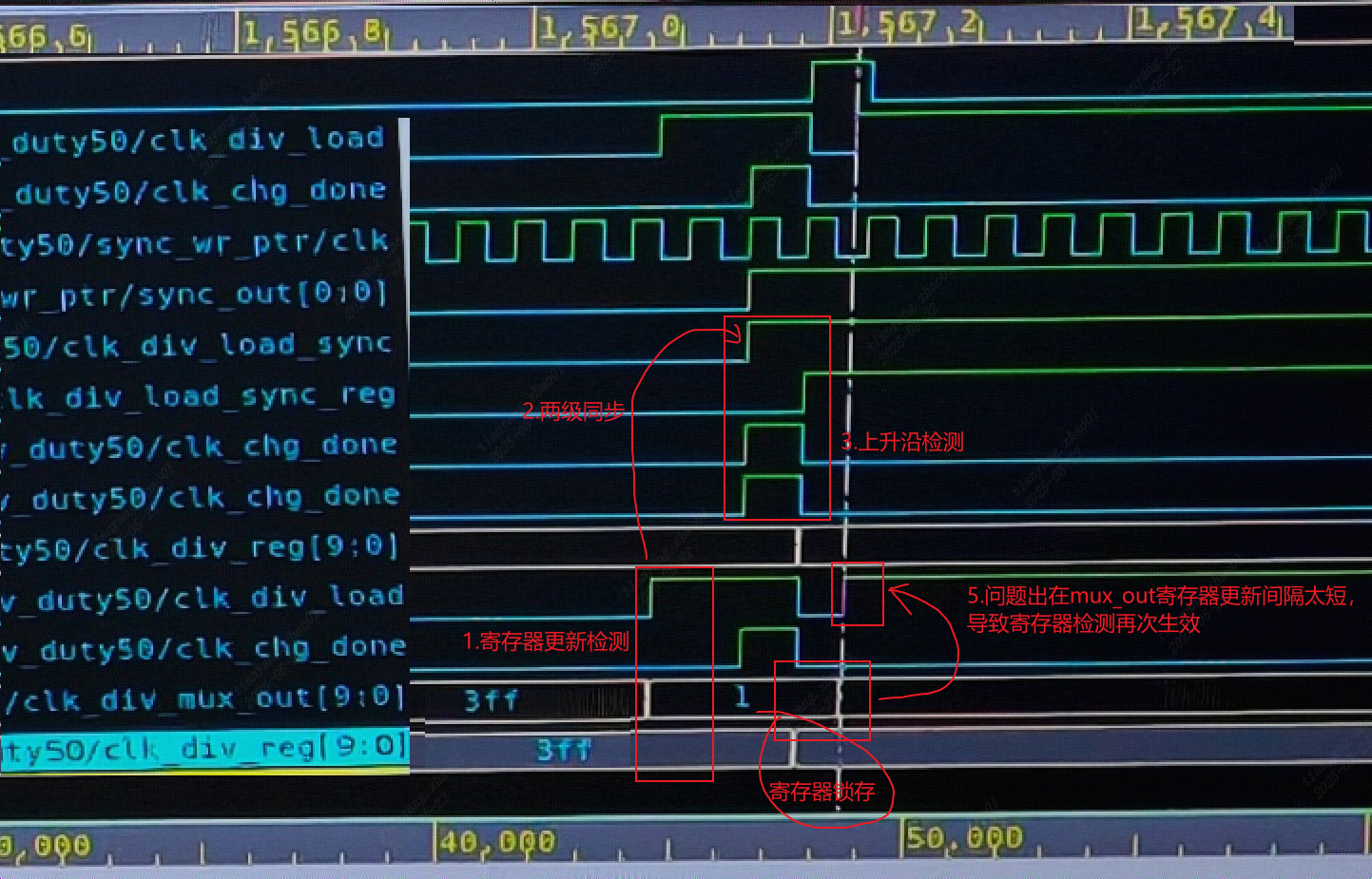

电路使用注意事项***

但需要注意的是,这个电路整个的执行流程需要消耗5~6(不包含)个时钟周期,即要求clk_div_reg输入寄存器不能变化太快。

- 如果clk_div_reg输入寄存器在寄存器完成锁存后3个时钟周期内,再次变化值会引起(clk_chg_load)强迫拉高,而此时语句clk_chg_done = (~clk_div_load_sync_reg) & clk_div_load_sync;尚未完成上一次电路的同步(还在清“1→0”的过程中)

- 所以此时clk_div_load_sync_reg=1、clk_div_load_sync=1同时clk_div_load=1,此时下一个clk_chg_done永远不会出现,继而不会完成下一次的寄存器更新。

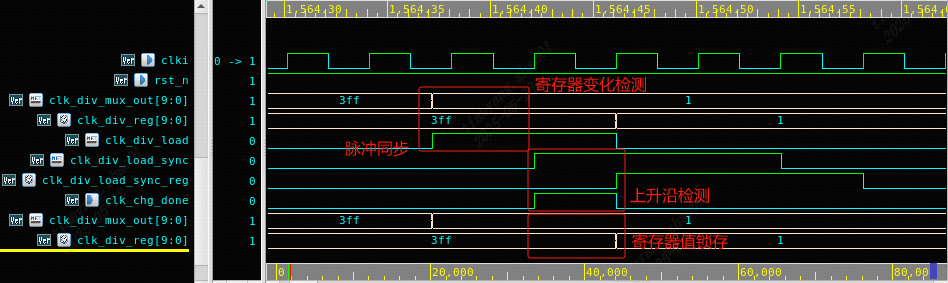

波形图

代码

//-----------------------------------------

//PLL 分频器值配置为例

//-----------------------------------------

module safe_divider_update #(parameter DIV_WIDTH = 8,

)(input wire clk, // 时钟input wire rst_x, // 异步低有效复位input wire [DIV_WIDTH-1:0] clk_div_mux_out, // 新分频比output reg [DIV_WIDTH-1:0] clk_div_reg // 生效分频比

);//-----------------------------------------

// 1. 分频值变化检测 → 异步单周期脉冲 clk_div_load

//-----------------------------------------

wire clk_div_load;

assign clk_div_load = |(clk_div_mux_out ^ clk_div_reg);//-----------------------------------------

// 2. 脉冲同步 & 滤除 → 同步后的单周期脉冲 clk_div_load_sync

// 两级寄存器同步,基本去毛刺/短脉冲逻辑可在此扩展

//-----------------------------------------

reg sync_ff1;

reg sync_ff2;

wire clk_div_load_sync;always @(posedge clk or negedge rst_x) beginif (!rst_x) beginsync_ff1 <= 1'b0;sync_ff2 <= 1'b0;end else beginsync_ff1 <= clk_div_load;sync_ff2 <= sync_ff1;end

endassign clk_div_load_sync = sync_ff2;//-----------------------------------------

// 3. 上升沿检测 → 生成加载完成信号 clk_chg_done

//-----------------------------------------

reg clk_div_load_sync_reg;

wire clk_chg_done;always @(posedge clk or negedge rst_x) beginif (!rst_x)clk_div_load_sync_reg <= 1'b0;elseclk_div_load_sync_reg <= clk_div_load_sync;

endassign clk_chg_done = (~clk_div_load_sync_reg) & clk_div_load_sync;//-----------------------------------------

// 4. 分频比锁存

// 在 clk_chg_done 上升沿时更新;复位时设为全1

//-----------------------------------------

always @(posedge clk or negedge rst_x) beginif (!rst_x)clk_div_reg <= {DIV_WIDTH{1'b1}};else if (clk_chg_done)clk_div_reg <= clk_div_mux_out;

endendmodule