Linux GPIO子系统中开漏模式软件仿真机制的深度分析

文章目录

- **Linux GPIO子系统中开漏模式软件仿真机制的深度分析**

- **第一章:引言**

- **第二章:GPIO输出模式的物理原理**

- **2.1 推挽输出模式 (Push-Pull Output)**

- **2.2 开漏输出模式 (Open-Drain Output)**

- **第三章:软件仿真逻辑的实现与分析**

- **3.1 源码呈现**

- **3.2 逻辑路径分析**

- **3.2.1 硬件支持路径**

- **3.2.2 软件仿真路径**

- **第四章:软件状态维护的关键机制**

- **4.1 物理状态与逻辑状态的分离**

- **4.2 `FLAG_IS_OUT` 的作用**

- **第五章:结论**

https://github.com/wdfk-prog/linux-study

Linux GPIO子系统中开漏模式软件仿真机制的深度分析

第一章:引言

通用输入/输出(GPIO)是嵌入式系统中控制器与外部设备进行交互的基础接口。在操作系统内核层,GPIO子系统负责提供一个统一的、抽象的接口,以管理和操作不同硬件平台上的GPIO引脚。这些操作包括设置引脚方向(输入/输出)、读取引脚电平以及配置引脚的电气特性,如驱动模式。

驱动模式中,推挽(Push-Pull)、开漏(Open-Drain)和开源(Open-Source)是三种基本类型。并非所有硬件GPIO控制器都原生支持所有这些模式。当硬件功能受限时,软件层必须介入,通过模拟(emulation)的方式来实现所需的功能。

本文旨在对Linux内核GPIO子系统中,当硬件不支持开漏模式时,所采用的软件仿真机制进行深入的、分步骤的技术分析。分析将围绕一段核心的C语言源码展开,详尽阐释其内部的执行流程、逻辑判断以及状态维护机制。

第二章:GPIO输出模式的物理原理

为了理解软件仿真的必要性和实现方式,必须首先明确相关GPIO输出模式的底层物理电路原理。

2.1 推挽输出模式 (Push-Pull Output)

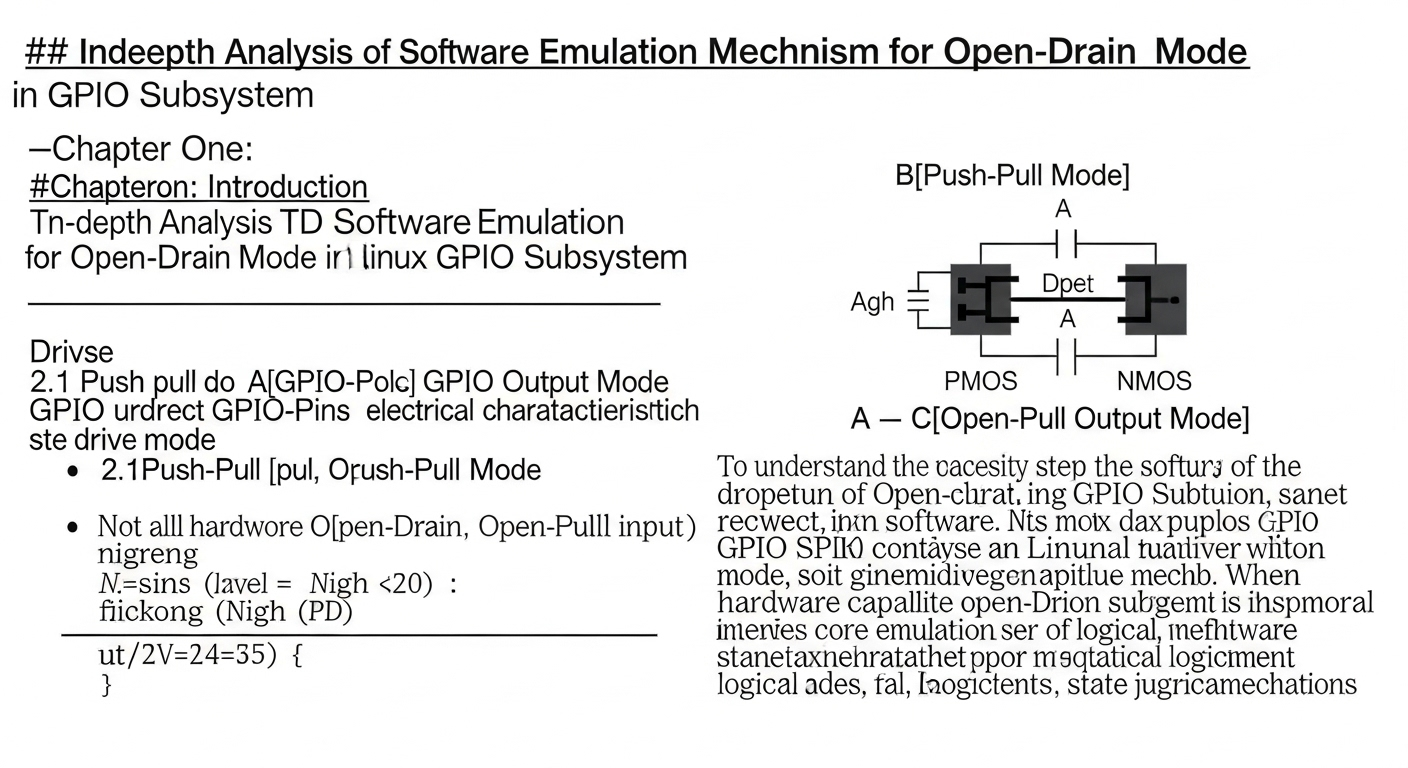

推挽输出模式是标准且最常见的GPIO输出配置。其内部电路由两个互补的晶体管(通常是PMOS和NMOS)构成,形成一个“推挽”结构。一个晶体管连接到高电平电源(VCC),另一个连接到地(GND)。

- 输出高电平(逻辑’1’): 连接VCC的晶体管导通,连接GND的晶体管截止。此时,引脚被内部电路主动驱动至高电平。

- 输出低电平(逻辑’0’): 连接VCC的晶体管截止,连接GND的晶体管导通。此时,引脚被内部电路主动驱动至低电平。

该模式的特点是驱动能力强,可以快速地上升和下降,能主动输出确定的高低两种电平。

2.2 开漏输出模式 (Open-Drain Output)

开漏输出模式的内部电路结构相对简单,通常只包含一个连接到地的晶体管(NMOS)。

- 输出低电平(逻辑’0’): 内部连接GND的晶体管导通,将引脚电平主动拉低至GND。

- 输出高电平(逻辑’1’): 内部连接GND的晶体管截止。此时,引脚在内部处于不连接任何电源的状态,即高阻态(High-Impedance)。要实现高电平,必须在GPIO引脚外部连接一个上拉电阻(Pull-up Resistor)到VCC。当内部晶体管截止时,该外部电阻会将线路电平拉高至VCC。

该模式允许多个开漏引脚连接到同一条总线上,实现“线与”(Wired-AND)逻辑。任何一个引脚输出低电平,都会将整条总线拉低。

第三章:软件仿真逻辑的实现与分析

当硬件GPIO控制器不具备原生的开漏配置能力时,GPIO子系统必须利用一个标准的推挽引脚来模拟开漏行为。以下源码展示了这一过程的完整实现。

3.1 源码呈现

/** 处理开漏(Open Drain)模式:*/if (test_bit(FLAG_OPEN_DRAIN, &flags)) {/* 首先, 尝试让硬件直接支持开漏模式. */ret = gpio_set_config(desc, PIN_CONFIG_DRIVE_OPEN_DRAIN);if (!ret)goto set_output_value; /* 硬件支持, 直接去设置值. *//** 硬件不支持, 进行软件仿真:* 仿真开漏时, 如果要输出高电平(value=1), 我们不能主动驱动线路,* 而是应该将其设置为输入模式(高阻态), 依靠外部上拉电阻.*/if (value)goto set_output_flag;} else if (test_bit(FLAG_OPEN_SOURCE, &flags)) { /* 开源模式处理, 逻辑与开漏相反. */ret = gpio_set_config(desc, PIN_CONFIG_DRIVE_OPEN_SOURCE);if (!ret)goto set_output_value;/* 仿真开源时, 输出低电平(value=0)需要设置为输入模式. */if (!value)goto set_output_flag;} else {/* 标准的推挽(Push-Pull)模式, 这是一个建议性设置. */gpio_set_config(desc, PIN_CONFIG_DRIVE_PUSH_PULL);}

3.2 逻辑路径分析

代码的执行流程基于一系列条件判断,主要分为硬件支持路径和软件仿真路径。

3.2.1 硬件支持路径

这是首选的最优路径。

- 检查开漏标志: 代码首先通过

test_bit(FLAG_OPEN_DRAIN, &flags)检查该GPIO描述符是否被请求配置为开漏模式。 - 尝试硬件配置: 如果是开漏请求,代码调用

gpio_set_config(desc, PIN_CONFIG_DRIVE_OPEN_DRAIN),尝试请求底层的硬件驱动将引脚配置为原生的开漏模式。 - 判断配置结果:

gpio_set_config的返回值ret用于判断配置是否成功。如果ret为0,表示硬件驱动成功完成了配置。 - 跳转执行: 此时,代码执行

goto set_output_value,跳转到后续的标准输出值设置流程,因为硬件已处于正确的开漏模式。

3.2.2 软件仿真路径

当 gpio_set_config 返回非零值时,表示硬件不支持开漏模式,软件仿真逻辑被激活。

- 仿真条件判断: 仿真逻辑的核心在于根据期望输出的电平(

value)来模拟开漏行为。 - 模拟输出高电平(‘1’):

- 目标: 实现高阻态,依赖外部上拉电阻。

- 判断:

if (value)条件成立(即value为1)。 - 操作: 执行

goto set_output_flag。此跳转的目标代码块会将GPIO引脚的方向配置为输入模式。一个处于输入模式的推挽引脚,其物理特性即为高阻态,这与开漏输出’1’时的状态完全一致。

- 模拟输出低电平(‘0’):

- 目标: 主动将线路拉低至GND。

- 判断:

if (value)条件不成立(即value为0)。 - 操作: 代码将跳过

if语句块,继续向下执行。最终,流程会到达set_output_value:标签处(未在代码片段中完全展示,但属于该函数的后续部分),在那里,引脚将被配置为输出模式,并被驱动为低电平。这与开漏输出’0’的行为完全一致。

第四章:软件状态维护的关键机制

在软件仿真路径中,将引脚物理方向设置为输入来模拟高电平输出,这引入了一个新的问题:GPIO子系统的软件层可能会将此引脚的逻辑状态误认为输入,从而导致后续的输出操作失败。以下代码段解决了这个状态一致性问题。

4.1 物理状态与逻辑状态的分离

当通过 gpiod_direction_input() 这样的函数将引脚设置为输入模式时,GPIO子系统内部的状态标志通常会记录该引脚为输入引脚。如果此时用户再次调用 gpiod_set_value(desc, 0) 意图将其拉低,GPIO子系统会检查其状态,发现它是一个输入引脚,并可能因此拒绝该操作,返回错误。这就是物理状态(输入)和逻辑意图(仍然是输出)之间的矛盾。

4.2 FLAG_IS_OUT 的作用

为了解决上述问题,代码采用了一种精巧的状态维护技巧。在 set_output_flag: 标签后的代码块中执行了两个关键操作。

set_output_flag:ret = gpiod_direction_input_nonotify(desc);if (ret)return ret;/** 当我们通过不主动驱动线路(将模式设置为输入)来仿真* 开漏/开源功能时, 我们仍然需要设置IS_OUT标志,* 否则我们将无法再设置线路的值.*/set_bit(FLAG_IS_OUT, &desc->flags);return 0;

- 设置物理方向:

gpiod_direction_input_nonotify(desc)指令将引脚的物理方向设置为输入,以实现高阻态。 - 维护逻辑状态:

set_bit(FLAG_IS_OUT, &desc->flags)是整个机制的核心。这条语句强制在GPIO描述符的标志位中设置FLAG_IS_OUT。它向GPIO子系统的软件层明确声明:尽管此引脚的物理方向当前是输入,但其逻辑上仍然是一个输出引脚。

通过这个操作,物理状态和逻辑状态被有效分离。当用户下次调用 gpiod_set_value(desc, 0) 时,GPIO子系统检查 FLAG_IS_OUT 标志,发现它已被设置,因此允许该次写操作。随后,程序再次进入本文分析的仿真逻辑,此时因为 value 为0,引脚会被重新配置为输出模式并拉低,从而完成一个完整的开漏高低电平切换周期。

第五章:结论

Linux GPIO子系统通过一套缜密的软件逻辑,成功地在不具备原生开漏功能的硬件上仿真了开漏输出模式。该机制的实现可以总结为以下几个关键步骤:

- 优先硬件: 系统首先尝试使用硬件的原生开漏功能,这是最高效的路径。

- 软件回退: 当硬件不支持时,启用软件仿真机制。

- 双模切换: 仿真机制利用了标准推挽引脚的特性。通过将其配置为“输出低电平”来模拟开漏的“拉低”行为;通过将其配置为“输入模式”(高阻态)来模拟开漏的“释放”行为。

- 状态维护: 最关键的一步是,在将引脚配置为输入模式以模拟高电平时,通过强制设定

FLAG_IS_OUT软件标志,维持了该引脚在GPIO子系统中的“逻辑输出”身份,确保了后续输出操作的合法性。

这种物理状态与逻辑状态相分离的处理方式,是操作系统内核中为弥补硬件差异性、向上层提供统一接口的典型范例,体现了软件设计的灵活性与严谨性。