基于FPGA的视频接口之千兆网口(七GigE)

区别

有细心的朋友可能看到,博主写了两篇关于GigE的文章,分别是当前的七以及关于网口的第六篇GigE纯逻辑文章,这两者有什么区别呢?

其区别在于上一篇文章是使用纯逻辑搭建的对于GVCP(控制协议部分)只是提到了查询应答,而其他的功能并没有说明,而本文则是利用ZYNQ7010位核心通过该芯片独特的PL和PS来完成GigE的视频协议和控制协议。

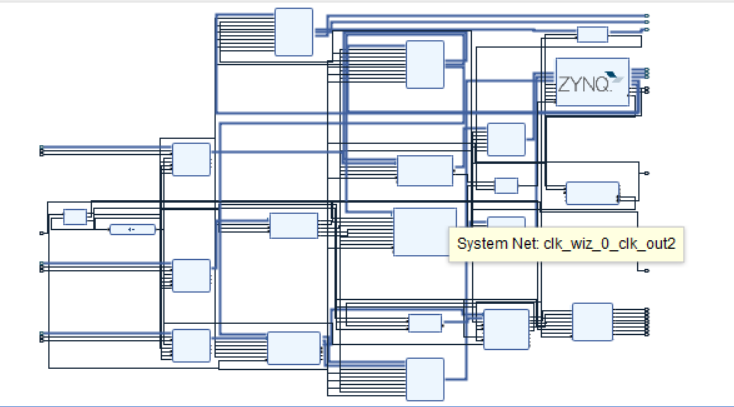

FPGA构成图

框图看着很复杂,其实很简单,首先通过IP将PL端视频信号,转换为AXI4信号,然后通过IP:VDMA将视频信号导入到DDR里面。同时让ARM核能够正常的访问DDR即可。剩下的IP要么是配套要么与这个主干线功能无关。

PL端设计

本项目设计是采用GMSL相机,相机分辨率为1280x720@30的分辨率格式为YUV422,为了方便显示博主已经将其转换为RGB888格式