高速采集卡FPGA设计方案及代码

目录

简介

设计指标

FPGA架构设计

时钟树

复位树

数据流

上位机通信方案

通信协议

详细模块设计方案

系统时钟

系统复位

系统参数

模拟前端配置

触发

Ø 外触发

Ø 通道触发

ADC算法

DMA控制

远程升级方案

测试方案

简介

款高速数字化仪,采用高速大容量数据缓存和高速数据交换技术,适用于高速、瞬态信号的精确捕获,可用于构建多通道、高精度、同步采集系统。高速采集卡是一类用于实现高采样率、高精度信号捕获的专业硬件,广泛应用于雷达、机器视觉、自动驾驶、医疗成像等领域。根据技术特性和应用场景,可划分为高速数据采集卡和高速图像采集卡两大类型。

设计指标

本产品作为一款PCIe采集卡,主要实现的功能为双通道模拟信号采集和示波。模拟信号采集通常使用高速ADC转换,由于采样率高、数据量大,因此需要使用Jesd204b通信协议,并将ADC数据存储在DDR中。对于示波功能,是将ADC采集的数据传送到CPU端进行UI显示,针对当前需求的带宽吞吐量,采用PCIe4.0 x8模式进行传输。基于以上需求,因此FPGA使用Xilinx公司UltraScale系列,型号:Xcku040

FPGA架构设计

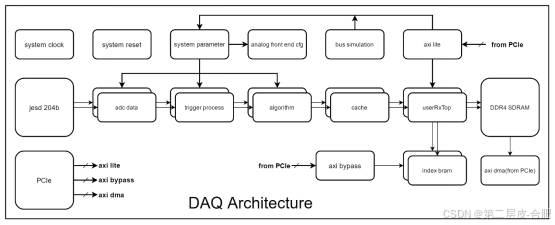

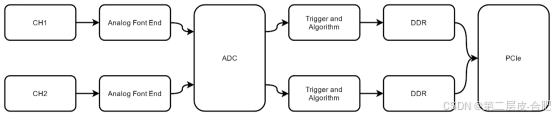

固件实现架构如图所示,双通道模拟信号经过各自前端电路后,进入ADC中,ADC通过Jesd204B协议总线上传至FPGA。FPGA内部实现了模拟前端控制、触发处理、算法处理、数据的储存和转发以及其他控制。

时钟树

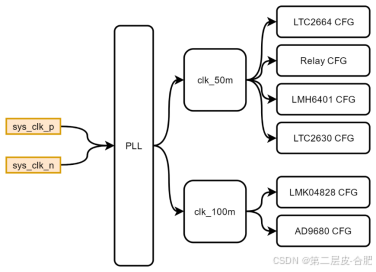

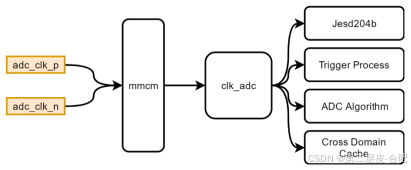

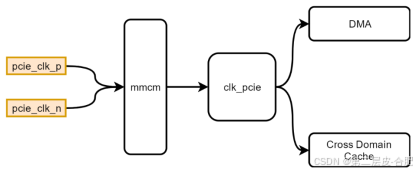

固件中系统时钟树主要分为3部分:

1) 系统时钟树

2) ADC时钟树

3) PCIe时钟树

复位树

固件中复位树主要分为3部分:

1) 系统复位

2) ADC复位

3) PCIe复位

每个时钟均有单独的复位信号,其复位树基本和时钟树一致。每个复位均采用异步复位,同步释放准则。

数据流

固件整体数据流如下所示:

上位机通信方案

FPGA与上位机通过PCIe总线连接,FPGA端使用XDMA ip实现对外总线接口。该总线接口框图如下所示:

该ip中共有三条总线,其中:

l axi lite:上位机通过该接口实现FPGA内部参数设置和回读。

l axi bypass:用于上位机索引表查询

l axi dma:用于上位机数据读取。

注:以上三条总线均属于业内标准总线,协议请参考

通信协议

Ø 寄存器配置协议

寄存器是通过axi lite接口配置,即常规的寄存器读写,没有额外的协议封装。

Ø 索引表协议

索引表用于表述当前固件数据写状态,CPU通过bypass接口读取索引表,判读是否有新数据。索引表是一个4096深度的BRAM,数据位宽为128bit,索引表数据格式如下所示:

| No. | Bits | Function | Note |

| 1 | [127:96] | rx_cnt | 接收到的字节数 |

| 2 | [95:94] | chnum | 通道编号 通道1:0 通道2:1 |

| 3 | [94:65] | ddr_wr_addr | ddr写入地址,地址每次累加0x400000 |

| 4 | [64:32] | block_cnt | 写一次索引表,该值加1 |

| 5 | [31:0] | Rsv | 全0 |

| 6 | [1:0] | chnum | 通道编号 通道1:0 通道2:1 |

详细模块设计方案

系统时钟

系统时钟模块主要是产生50MHz和100MHz的工作时钟,用于配置前端模拟电路。其时钟树参考系统时钟树章节。

系统复位

固件中不同的模块可能存在不同的工作时钟,这些时钟在相位和频率上基本各有不同,因此在设计中需要考虑不同时钟域下的复位。复位信号分为同步复位和异步复位,不同的复位方式存在各自的优缺点。

为了克服同步复位和异步复位各自的缺点,本设计采用异步复位,同步释放的准则。异步复位,同步释放就是指在复位信号到来的时候不受时钟信号的同步,而是在复位信号释放的时候受到时钟信号的同步,既可以解决亚稳态,又可以减少逻辑资源。

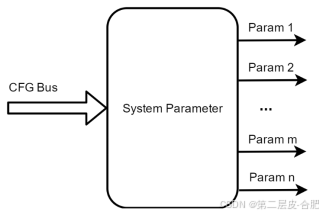

系统参数

系统参数模块的输入是一个系统配置总线,该总线来源于PCIe的AXI-Lite总线,输出是不同的配置参数和有效标志。每个参数都有对应的寄存器,详细请参考DAQ寄存器手册。

模拟前端配置

模拟前端配置主要是配置继电器、DAC、VGA等一些参数,该部分的详细配置方法请参考各自芯片手册。

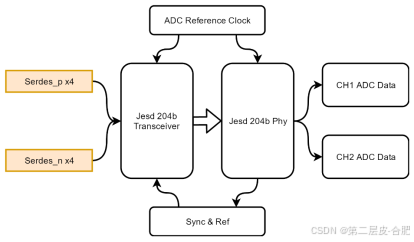

JESD204B总线控制

JESD204B总线作为高速数据转换器首选数字接口,与传统LVDS接口相比,该接口在传输带宽上有很大的优势。本固件中使用Jesd204b接口作为ADC数据接口,内部控制如下所示:

图中Sync和Ref模块用于产生同步和参考信号,该信号连接至ADC器件。ADC Reference Clock是与ADC Core时钟同源的参考时钟,250MHz。

触发

触发处理是产品一个核心功能。触发主要分为外触发、通道触发、软触发3种,下面将对每个触发一一介绍。

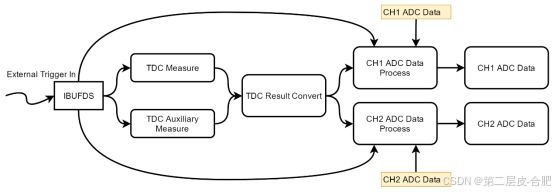

Ø 外触发

外触发即使用外部触发方式进行数据采样。外触发模块主要分为:TDC测量、TDC辅助测量、TDC测量结果转换、ADC触发处理。设计框图如下所示:

下面介绍每个单独模块的功能:

IBUFDS模块:外部触发输入是一个差分信号,经过IBUFDS后转成单端信号。

TDC Measure:由于外部触发输入是一个异步信号,因此会与采样时钟存在抖动问题,使用TDC测量模块,可以测出外部触发沿与测量时钟沿之间的抖动关系,以便后续进行数据补偿。

TDC Auxiliary Measure:该模块是一个辅助测量模块,主要是解决TDC Measure测量存在的问题。

TDC Result Convert:该模块是将两个TDC测量结果进行转换,方便后续采样点数补偿。

ADC Data Process:该模块产生数据触发有效信号,并对TDC测量结果进行采样点补偿。

Ø 通道触发

通道触发是类似电平触发的概念,即主控端设置一个触发电平值,当采样信号的电平值大于(上升沿触发模式)或小于(下降沿触发模式)设置的触发电平值时,触发新的采样。由于被采样信号频率的不同,触发点位置的电平值会存在抖动,针对该问题,采用差值算法进行差值处理,该部分的实现方案尚在理论探讨中。

Ø 软触发

由软件下发的一个触发指令,再内部产生一个触发信号

ADC算法

ADC算法主要实现3种算法:累加算法、NSA+,NSA-。

Ø 累加算法

累加算法顾名思义将每个trigger对应点累加,达到累加次数后,再上传至CPU。累加算法点数为0~100Ksa,即100*1024个点;累加次数为0~65536。

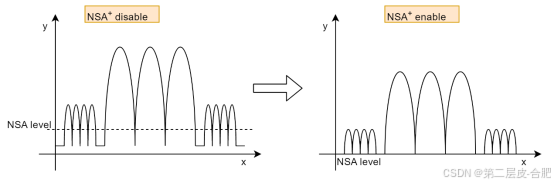

Ø NSA+

NSA(Nosie Suppression Algorithm)中文含义噪声抑制算法,如下所示:

当NSA+算法打开时,CPU将设置噪声抑制基线,对于ADC采集到的信号做如下处理,记输入信号为S, NSA+ Level为NSL,输出为R:

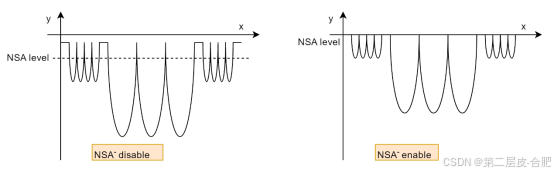

Ø NSA-

NSA-和NSA+类似,只是针对的输入信号不同,处理的方式不同。如下所示:

当NSA-算法打开时,CPU将设置噪声抑制基线,对于ADC采集到的信号做如下处理,记输入信号为S, NSA- Level为NSL,输出为R:

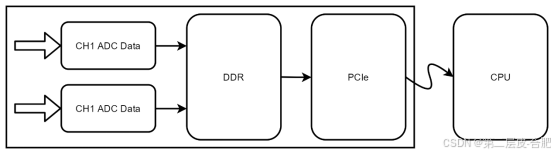

DMA控制

DMA控制主要完成ADC数据的存储和发送,如下所示。

当ADC有数据时,会启动DDR写操作,将数据写入DDR中;写入的同时会记录写入的地址和长度,CPU采用查询模式查询索引表,进行数据的判读是否有新数据;当有新数据时,使用DMA操作读取数据。

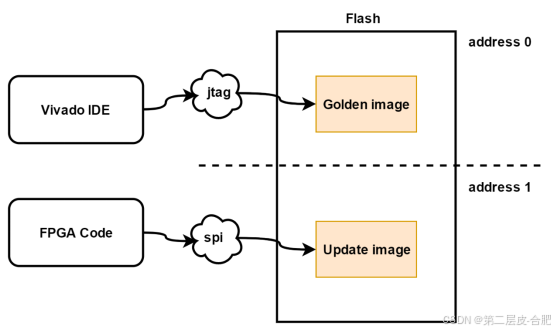

远程升级方案

远程升级方案采用双镜像方案,实现方案如下所示(仅作为示意图):

图中Golden image为出厂时固化镜像文件,Update image为用户远程更新镜像文件。

FPGA上电启动时,首先会加载Golden image,在加载过程中,判断该image中某个标志位,该标志位存在时,即跳转加载Update image;当不存在时,会继续加载Golden image。当Update image不存在或者出错时,FPGA会自动跳转至Golden image继续加载。

比特流加密方案(FPGA)

该点需求暂时不是必要,因此暂未实现,后续再补充方案。

固件风险点分析

根据现有的方案分析,固件存在风险点主要是以下几个方面:

1) 外触发抖动,TDC沿临界测量结果不稳定,导致TDC补偿存在问题。

2) 由于累加算法和跨时钟域需要大量BRAM,因此FPGA内部Block RAM可能存在资源紧张情况。

3) 通道触发插值算法实现,该部分尚未调研和实现,可能是一个风险点。

测试方案

描述固件的功能及性能测试方案,包括(通信连接、寄存器读写、数据流稳定性、板载硬件外设如时钟芯片、DDR等速率测试)

源代码

可以私信进行沟通