PCIe— Legacy PCI

Legacy Model

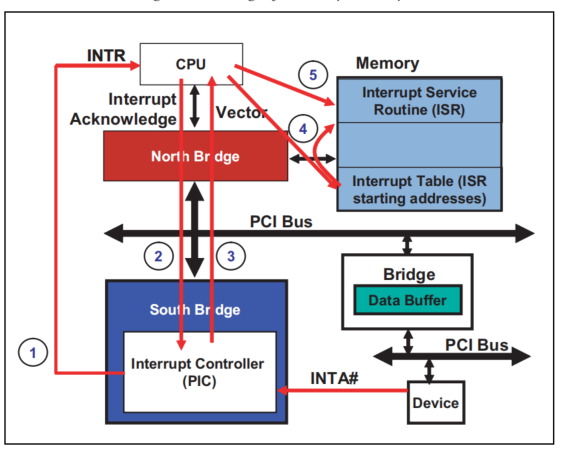

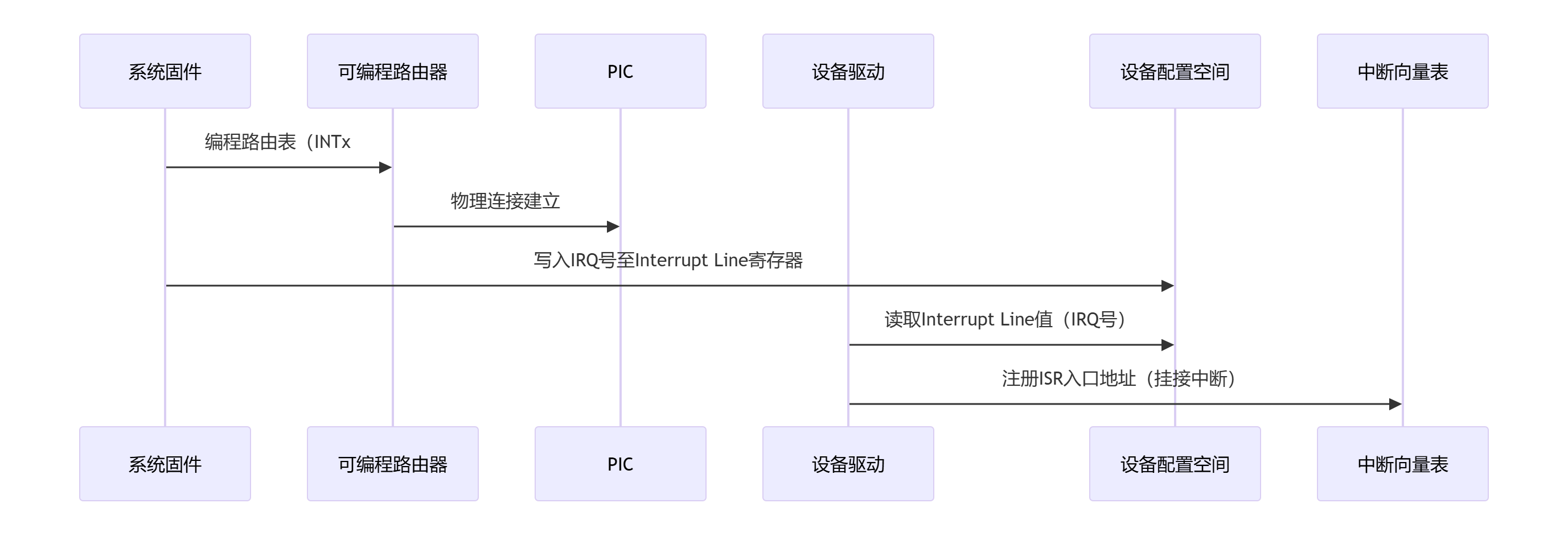

传统中断交付模型(Legacy Interrupt Delivery)核心流程

1. 设备触发中断(Device Asserts Interrupt Pin)

- 物理信号:PCI设备通过电平触发方式拉低INTx#引脚(如INTA#)。

- 共享线路:多个设备共享同一条中断线(Wire-OR连接),如图中PCI Bus上的

INTA#信号。 - 关键问题:

- 电平保持:设备需维持低电平直至中断被处理,否则中断丢失。

- 冲突延迟:共享线路需等待所有设备释放信号才能结束中断。

2. 中断控制器响应(PIC Processes Request)

- 南桥(South Bridge)接收

INTA#信号,转发至中断控制器(PIC)。 - PIC检测到有效IRQ输入后,拉高INTR信号通知CPU(步骤②)。

- 8259 PIC特性:

- 15级IRQ输入,固定优先级(IRQ0最高,IRQ7最低)。

- 边沿/电平触发模式可配置(传统PCI强制为电平触发)。

3. CPU中断应答(CPU Issues Interrupt Acknowledge)

- 处理器总线操作:

- CPU检测到INTR有效后,通过北桥(North Bridge)发送Interrupt Acknowledge命令(步骤③)。

- 该命令本质是特殊总线周期(x86为

INTA总线周期)。

- 关键约束:

- 中断应答期间CPU暂停执行,直至获取中断向量。

4. 中断向量获取(PIC Returns Interrupt Vector)

- 向量生成:

- PIC将当前最高优先级IRQ转换为8位中断向量号(步骤④)。

- 向量号由BIOS/OS预先编程(如IRQ0=0x08, IRQ1=0x09)。

- 硬件交互:

- 向量号通过数据总线返回给CPU(图中

Vector路径)。

- 向量号通过数据总线返回给CPU(图中

5. 中断服务例程执行(ISR Execution)

- 中断表查询:

- CPU以向量号为索引,从中断描述符表(IDT) 读取ISR入口地址(步骤④)。

- x86实模式:中断表为IVT(基址0x0000);保护模式:IDT基址由IDTR寄存器指定。

- ISR处理流程:

- 保存CPU上下文(寄存器压栈)。

- 执行设备服务逻辑(如读取状态寄存器)。

- 清除中断源:向设备发送EOI(End of Interrupt)命令。

- 恢复上下文并返回(

IRET指令)。

传统模型的技术缺陷与PCIe改进

1. 主要瓶颈

| 问题 | 根源 | 后果 |

|---|---|---|

| 共享冲突 | 多设备共享INTx#线路 | 延迟不可控,优先级反转 |

| 电平保持依赖 | ISR必须手动清除设备中断 | 竞争条件导致中断丢失 |

| 中断风暴风险 | 故障设备持续拉低INTx# | 系统死锁 |

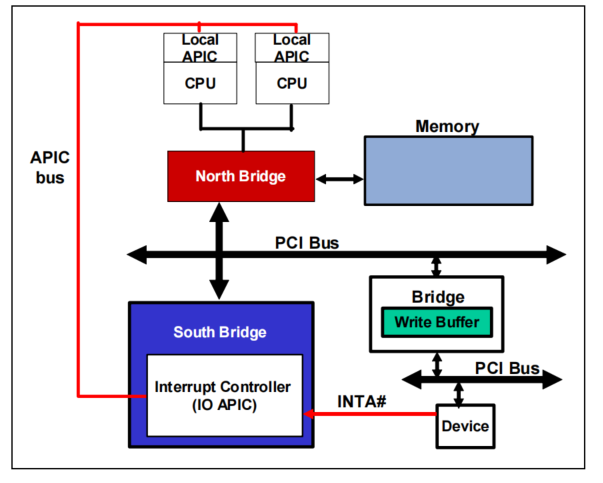

| 多核扩展性差 | PIC不支持多CPU中断分发 | SMP系统性能瓶颈 |

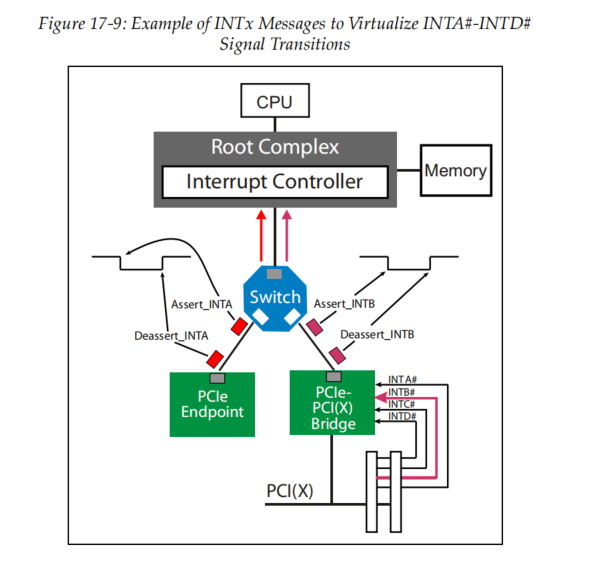

2. PCIe的兼容性改造

- 虚拟INTx消息:

- 用

Assert_INTx/Deassert_INTx消息包模拟电平变化。 - 消息路由:设备 → RC(Root Complex) → IO APIC(替代PIC)。

- 用

- 桥接转换:

- PCIe-to-PCI桥将物理INTx#信号转换为虚拟INTx消息(见图中Bridge角色)。

与传统模型相关的关键硬件

| 组件 | 作用 |

|---|---|

| 8259 PIC | 将IRQ转换为向量号,管理15级中断优先级 |

| 南桥(South Bridge) | 集成中断控制器,连接低速设备(如PCI总线) |

| 北桥(North Bridge) | 处理CPU与高速组件(内存/显卡)通信,转发中断应答命令 |

| 中断描述符表(IDT) | 存储中断向量与ISR入口地址的映射关系(x86架构核心数据结构) |

Changes to Support Multiple Processors

Legacy PCI Interrupt Delivery

PCI设备想使用中断的画,有两种选择。 他们可以使用:

(1)INTx#可共享的低电平有效信号,在原始规范中定义。

Device INTx# Pins

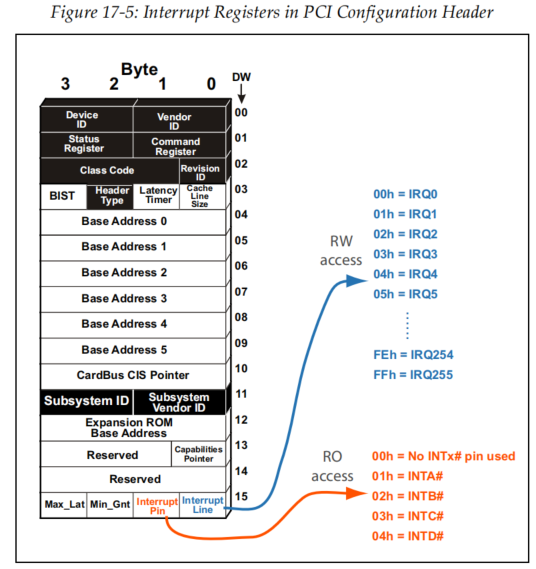

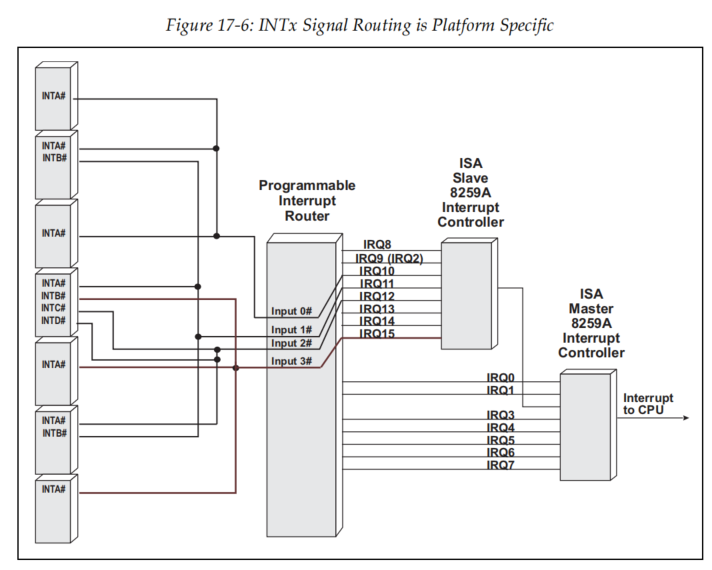

PCI设备最多支持4个INTx#信号(INTA#~INTD#)。因PCI设备可含8个功能(Function),每个功能仅能驱动一个中断引脚。PCI开发时,典型系统采用含15输入的8259 PIC,但许多IRQ已被系统占用(如定时器、键盘),部分预留给ISA卡。故规范仅支持4个中断引脚。然而PCI总线上设备常超4个,单设备内功能也可能超4个需中断,因此PCI中断被设计为电平敏感且可共享——这些信号可通过线或(wire-ORed)连接。当中断触发时,ISR需遍历共享同引脚的所有功能以确认中断源

Determining INTx# Pin Support

图17-5所示的中断线寄存器(Interrupt Line Register)提供驱动所需的下一条信息:该引脚连接至PIC(可编程中断控制器)的输入引脚。系统软件为PIC的每个输入引脚(IRQ)编程分配唯一的中断向量号。当最高优先级中断触发时,PIC向处理器报告该向量号,处理器据此索引中断向量表,获取并执行对应设备的中断服务程序(ISR)。

设计人员从器件分配INTx#引脚的路由方式。 它们可以通过多种方式进行路由, 但最终每个INTx#引脚都连接到中断控制器的一个输入端。 第803页的图17 - 6 举例说明了通过可编程路由器将多个PCI设备中断连接到中断控制器的情况。 连接到可编程路由器给定输入端的所有信号将被定向到中断控制器的特定输入端。 其中断被路由到公共中断控制器输入的功能都将具有由平台软件(通常为固件)分配给它们的相同的中断线编号。 在本例中,IRQ 15有三个PCI INTx#输入,来 自连接到它的不同设备。因此,使用这些INTx#线的功能将共享IRQ 15,因此在查询时,所有function都将使控制器发送相同的向量。 该向量将不同功能的三个ISR链接在一起

Associating the INTx# Line to an IRQ Number

根据系统需求,路由器被编程将其四个输入连接到PIC(可编程中断控制器)的四个可用输入。完成后,每个功能(Function)关联的INTx#引脚路由路径即确定,系统软件将中断线编号(IRQ号)写入每个功能的Interrupt Line寄存器。该值最终被设备驱动读取,从而知晓其中断在中断向量表中的位置——驱动将ISR(中断服务程序)入口地址写入此位置,此过程称为挂接中断(hooking the interrupt)。当该功能触发中断时,CPU将接收与Interrupt Line寄存器指定的IRQ对应的向量号,并据此索引中断向量表,获取该功能设备驱动关联的ISR入口地址。

NTx#信号线为低电平有效的漏极开路(Open-Drain)信号,系统为每条线提供上拉电阻。连接至同一PCI中断请求信号线的多个设备可同时置位(Assert)该信号而不会造成损坏。

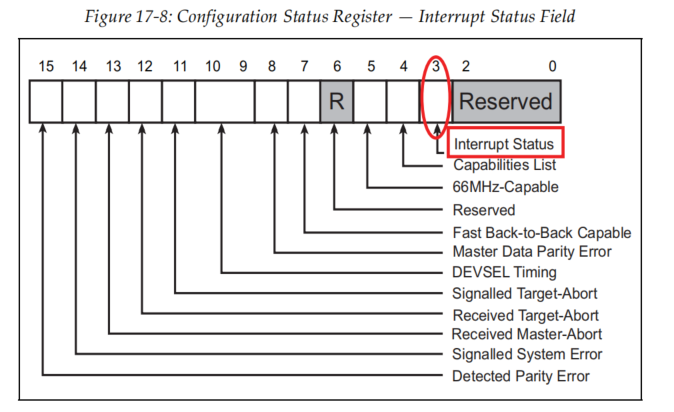

当功能(Function)触发中断时,其配置头状态寄存器(Status Register)中的中断状态位(Interrupt Status Bit) 将被置位。系统软件可通过读取该位判断当前是否有中断挂起。

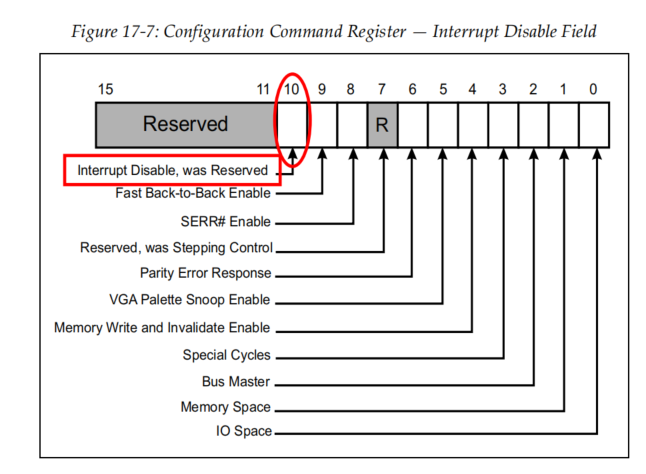

PCI 2.3规范在配置头命令寄存器(Command Register)中新增中断禁用位(Interrupt Disable Bit,Bit 10)。复位时该位为0(允许INTx#信号生成),但软件可置1以禁用INTx#。需注意:此位对MSI(消息信号中断)无效。MSI通过其专属能力结构(MSI Capability Structure)中的命令寄存器启用,且启用MSI会自动禁用INTx引脚或其模拟机制。

以下是针对PCI规范中中断状态位(Interrupt Status Bit) 的技术解析,结合配置空间寄存器机制及中断触发逻辑进行说明:

🔧 一、中断状态位(Interrupt Status Bit)的核心机制

1. 功能定义与行为规则

- 位置与属性:

- 位于PCI配置空间状态寄存器(Status Register) 的Bit 3(只读)。

- 当设备有中断挂起(Pending)时,硬件自动置位此位,软件无法直接写入。

- 触发条件:

- 设备内部中断事件(如DMA完成、错误状态)发生时,硬件将

Interrupt Status = 1。

- 设备内部中断事件(如DMA完成、错误状态)发生时,硬件将

- 与INTx#信号的关联:

- 若命令寄存器(Command Register) 的中断禁用位(Interrupt Disable, Bit 10)为0(即INTx中断启用):

Interrupt Status = 1会立即触发INTx#信号(拉低电平或发送Assert_INTx消息)。

- 若中断禁用位为1(INTx中断禁用):

Interrupt Status仍会记录中断状态,但不会触发INTx#信号,中断被静默。这种设计允许驱动在禁用中断时仍能通过轮询状态位处理紧急事件(如硬件错误)。

- 若命令寄存器(Command Register) 的中断禁用位(Interrupt Disable, Bit 10)为0(即INTx中断启用):

2. 与中断禁用位的独立性

| 寄存器/位 | 作用范围 | 是否影响状态位 |

|---|---|---|

| Status Bit 3 | 仅记录INTx中断状态 | ❌ 不受任何控制 |

| Command Bit 10 | 控制INTx信号触发 | ✅ 决定是否传递中断 |

🔄 二、与MSI/MSI-X中断的互斥性

1. MSI启用时的自动切换

| 行为 | INTx模型 | MSI模型 |

|---|---|---|

| 中断触发方式 | 依赖状态位+INTx#信号 | 内存写消息(TLP包) |

| 状态位影响 | ✅ 有效 | ❌ 无效(状态位无意义) |

| 启用MSI的副作用 | 硬件自动禁用INTx信号 | 独占中断通道 |

Virtual INTx Signaling

- PCIe转PCI/PCI-X桥接器:多数PCI设备使用INTx#引脚(因MSI对它们为可选功能)。由于PCIe不支持边带中断信号(sideband signaling),需改用带内消息(inband messages) 传递中断请求。中断控制器解析该消息并向CPU提交中断请求(含预编程的向量号)。

- 引导设备(Boot Devices):PC系统在引导阶段常用传统中断模型,因MSI通常需OS级初始化。引导至少需三个子系统:输出设备(如显卡)、输入设备(如键盘)、操作系统加载设备(如硬盘)。参与系统初始化的PCIe设备称为“引导设备”,它们在OS及驱动加载前使用传统中断支持,之后建议切换至MSI。

Virtual INTx Wire Delivery

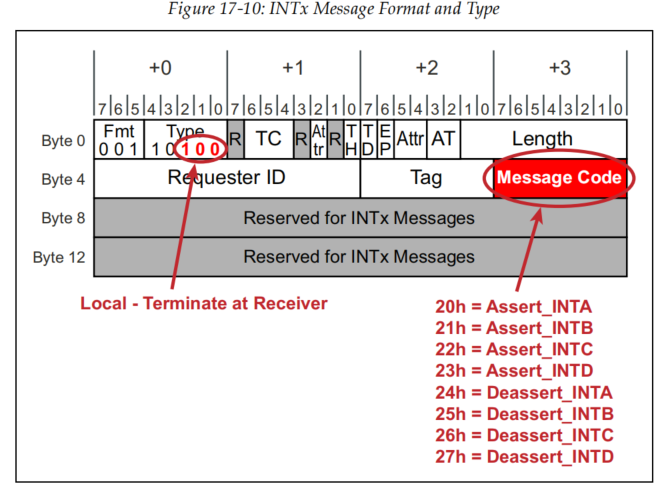

INTx Message Format

Mapping and Collapsing INTx Messages

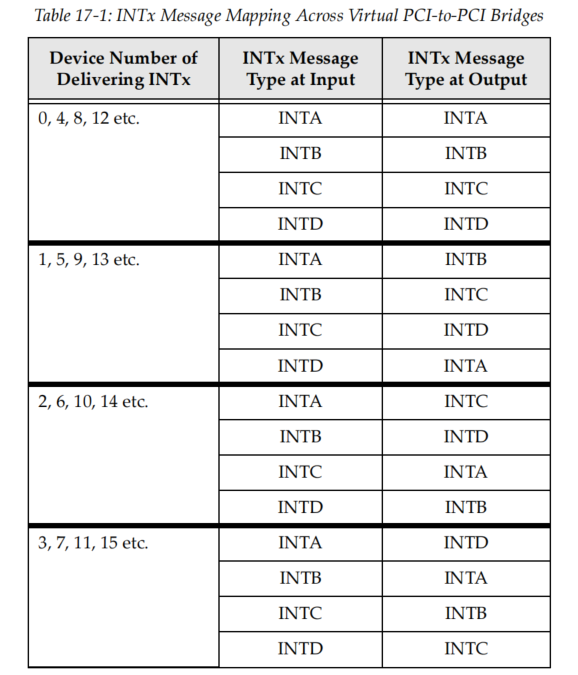

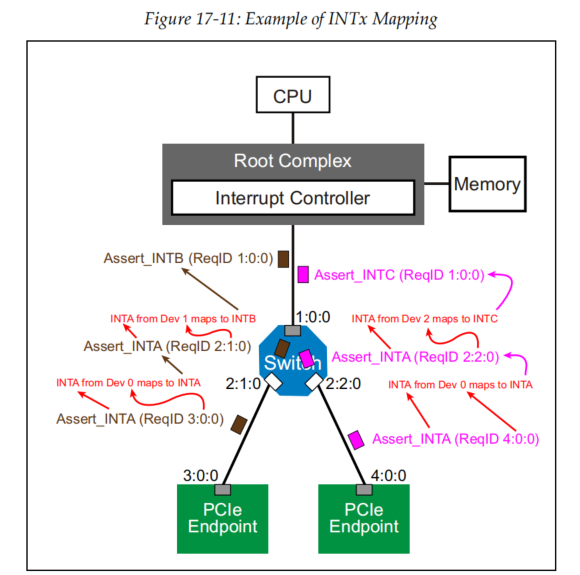

INTx Mapping

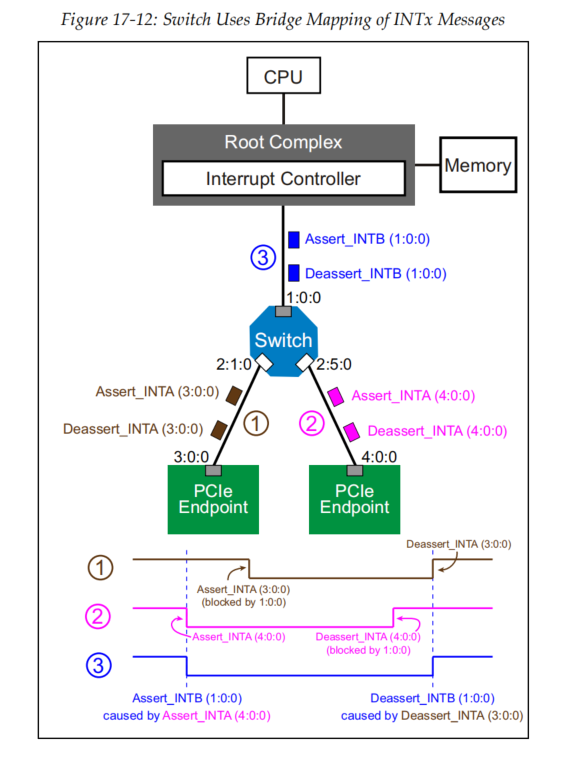

INTx Collapsing

PCIe交换机必须确保INTx消息以正确方式向上游传递。具体而言,对传统PCI实现的中断路由处理时需满足:软件能判定哪些中断被路由至中断控制器的哪个输入引脚。INTx#信号线可采用线或连接(wire-ORed) 方式接入中断控制器的同一IRQ输入引脚。当多个设备在同一中断线上触发中断时,中断控制器仅感知首个断言(assertion)信号;同理,当其中一个设备撤(deassert)其INTx#信号线时,该线将保持断言状态直至最后一个设备撤销中断。这些原则同样适用于PCIe的INTx消息机制。

但在某些场景下,两个重叠的INTx消息可能被出口端口的虚拟PCI桥映射为同一INTx消息,需要折叠这些消息。以图17-12为例:当上游交换机端口为中断消息映射传输路径时,两个下游交换机端口的中断消息(基于其设备号)均被映射为INTB。由于这两个重叠消息类型相同,必须进行折叠。

折叠机制确保中断控制器永远不会为共享中断接收到连续的Assert_INTx或Deassert_INTx消息,这与INTx信号采用线或连接的行为等效。

折叠机制的必要性

-

避免中断控制器状态冲突:

-

若连续发送

Assert_INTB→ 中断控制器误判为多次独立中断请求 -

若过早发送

Deassert_INTB→ 中断提前终止,遗漏未处理设备

-

-

与物理线或一致性:

折叠机制确保虚拟INTx信号行为完全匹配物理共享中断线的电平特性,保持与传统驱动兼容性

| 机制 | 实现目标 | 硬件要求 |

|---|---|---|

| 线或模拟 | 兼容共享IRQ的物理PCI中断行为 | 交换机维护虚拟INTx状态寄存器 |

| 动态映射 | 支持多级拓扑下的中断信号重组 | 端口内置设备号-INTx映射表 |

| 消息折叠 | 防止冗余中断消息,确保电平语义 | 丢弃同类型连续Assert/Deassert消息 |

INTx Delivery Rules

关键规则:

- Assert_INTx与Deassert_INTx仅向上游方向发送

- 交换机仅在中断状态变化时才向上游发送INTx消息

- 链路两端设备必须跟踪INTA-INTD的当前置位状态

- 交换机需独立跟踪每个下游端口的四个虚拟信号线状态,并在上游端口呈现折叠后的状态集合

- 根复合体必须为每个下游端口跟踪四个虚拟信号线(A-D)状态

- 可通过命令寄存器(Command Register)的中断禁用位(Interrupt Disable bit)关闭INTx信令

- 若存在活跃的INTx虚拟信号线时禁用中断,必须发送对应的Deassert_INTx消息

- 若下游交换机端口进入DL_Down状态,所有活跃的INTx虚拟信号线必须解除置位,并向上游端口发送Deassert_INTx消息更新状态

NOTE:

1. 单向传输与状态跟踪机制

-

仅上游传输:

INTx消息(Assert/Deassert)仅允许从下游设备向上游根复合体传递,禁止反向或同级传输。 -

链路级状态同步:

每个PCIe链路两端设备(如设备与交换机端口)需维护虚拟INTx信号线状态寄存器(如INTA_Status),确保电平行为与物理PCI信号一致。

2. 交换机的折叠处理(Collapsing)

-

状态变化触发:

交换机仅当检测到下游端口虚拟信号线状态从非活跃→活跃(Assert)或活跃→非活跃(Deassert)时,才向上游转发消息。 -

多设备信号合并:

多个下游设备共享同一INTx类型时(如设备号1和5均触发INTA),交换机将其折叠为单次Assert/Deassert消息,模拟PCI的线或(Wire-OR)行为。示例:下游两个设备同时Assert_INTA → 交换机仅向上游发送一次Assert_INTA,直至所有设备解除后才发Deassert。

3. 根复合体的职责

-

端口级状态管理:

根复合体需为每个下游端口维护独立的INTx状态表,映射到系统中断控制器(如APIC)。 -

中断资源映射:

根据BIOS/ACPI表将虚拟INTx信号(如INTA)转换为物理IRQ,供操作系统处理。

4. 中断禁用与异常处理

-

强制解除机制:

若启用命令寄存器的Interrupt Disable bit(偏移04h位10),需立即发送Deassert_INTx消息解除所有活跃中断。 -

链路失效响应:

下游端口进入DL_Down状态(链路训练失败)时,交换机自动解除其关联的INTx状态,并向上游发送Deassert消息。

📊 三、规则总结

| 规则 | 硬件行为 | 设计目的 |

|---|---|---|

| 单向传输 | 仅允许Assert/Deassert向上游传递 | 避免环路,确保路径唯一性 |

| 状态折叠 | 交换机过滤冗余状态变化消息 | 模拟电平触发,减少总线负载 |

| 根复合体跟踪 | 独立维护每端口INTx状态 | 精准映射系统中断资源 |

| 中断禁用强制解除 | 禁用时立即发送Deassert | 防止残留中断请求干扰系统 |

| DL_Down状态处理 | 自动解除关联INTx并更新上游 | 确保中断状态与物理链路同步 |

⚠️ 四、设计注意事项

-

与MSI的互斥性:

启用MSI/MSI-X时,INTx自动失效(配置空间Command Register的Interrupt Disable位强制置1)。 -

虚拟信号线映射:

交换机需按设备号(Device Number) 转换INTx类型(如设备号1的INTA→上游INTB)。 -

驱动兼容性:

传统PCI驱动依赖INTx,需确保在引导阶段(MSI未初始化时)正确处理Assert/Deassert消息。

核心结论:INTx消息规则通过状态跟踪+折叠转发+强制解除三重机制,在无物理信号线的PCIe架构中精准复现PCI中断语义,为传统设备提供无缝兼容,但高性能场景应优先选用MSI/MSI-X。