计算机结构-逻辑门、存储器、内存、加法器、锁存器、程序计数器

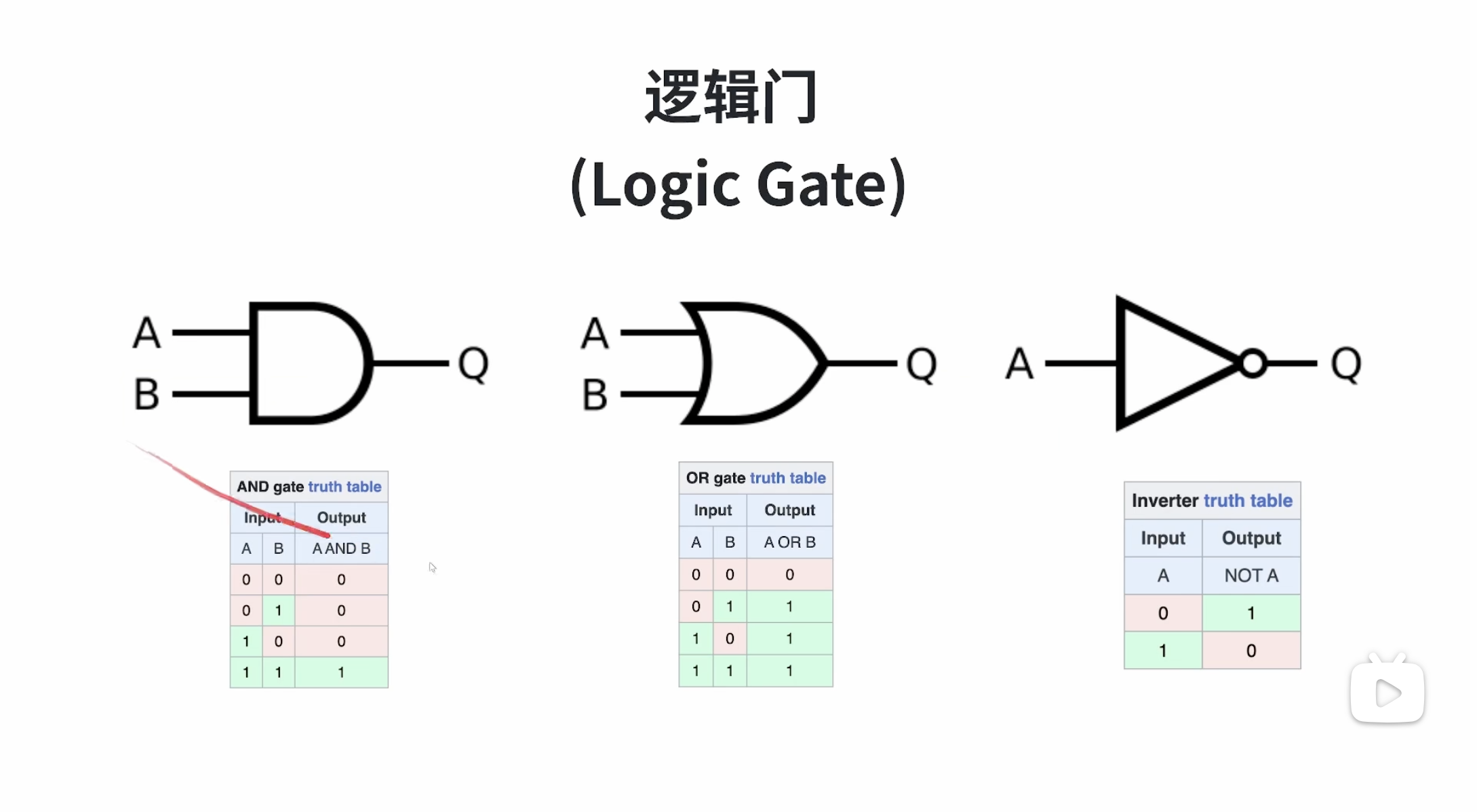

逻辑门

逻辑门简单地理解即通过特定的条件实现与、或、非、异或等相关逻辑

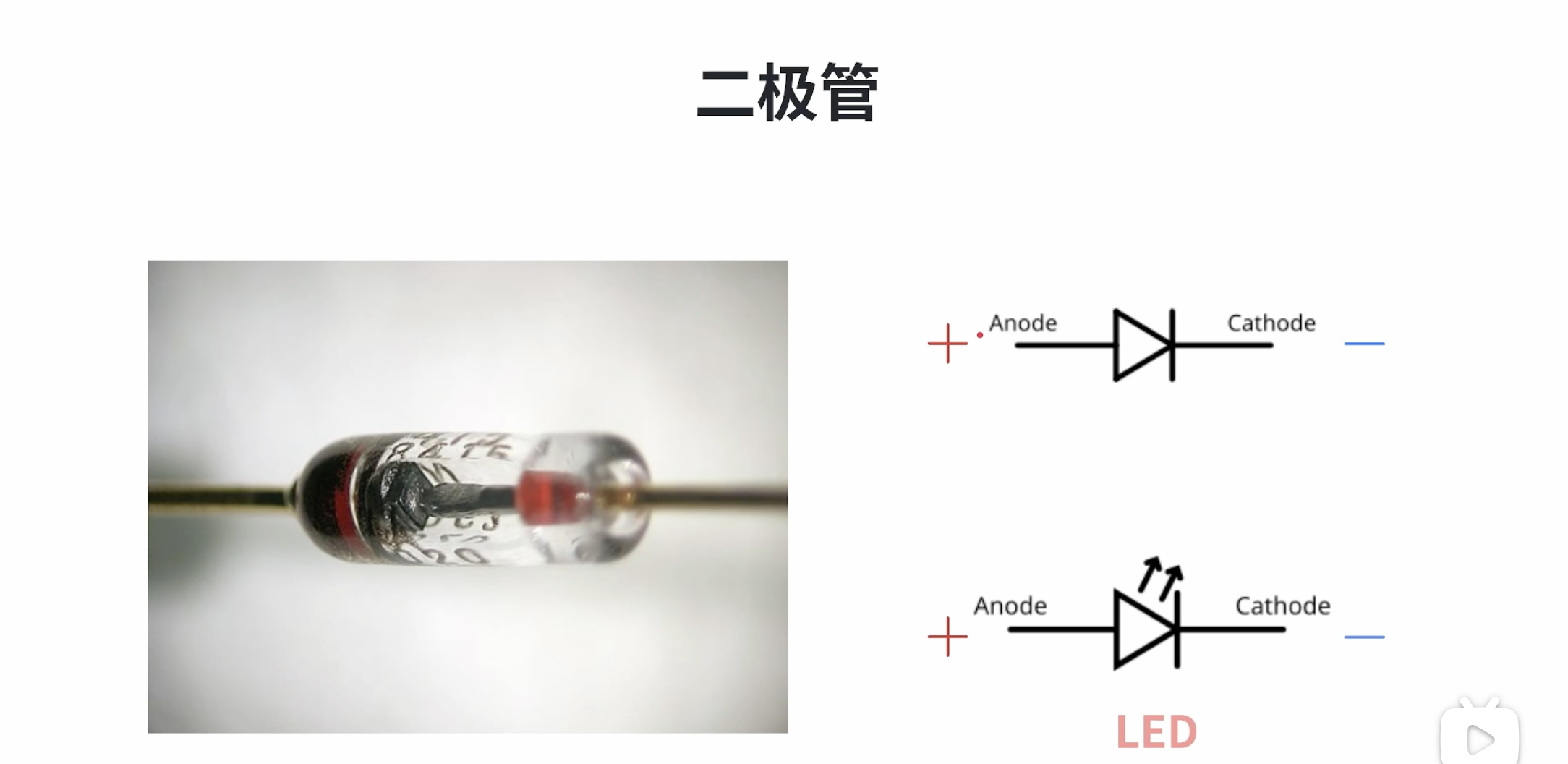

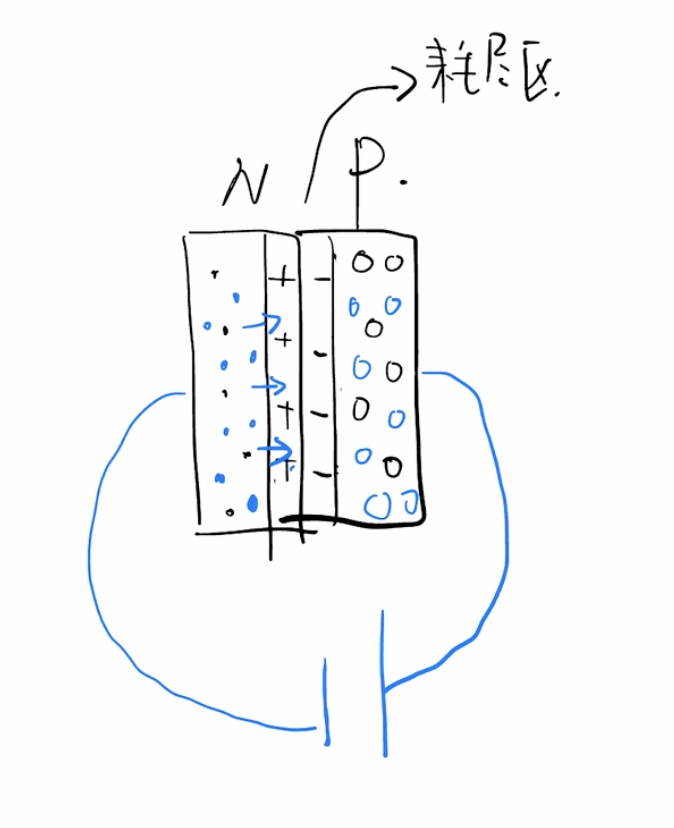

二极管

这些最基础的逻辑门都是通过电路元器件进行搭建的,即半导体材料搭建的二极管

二极管有个特点,一定条件下才可以导通,即得接对正负极,具体的原理可以参考模拟电子技术相关内容

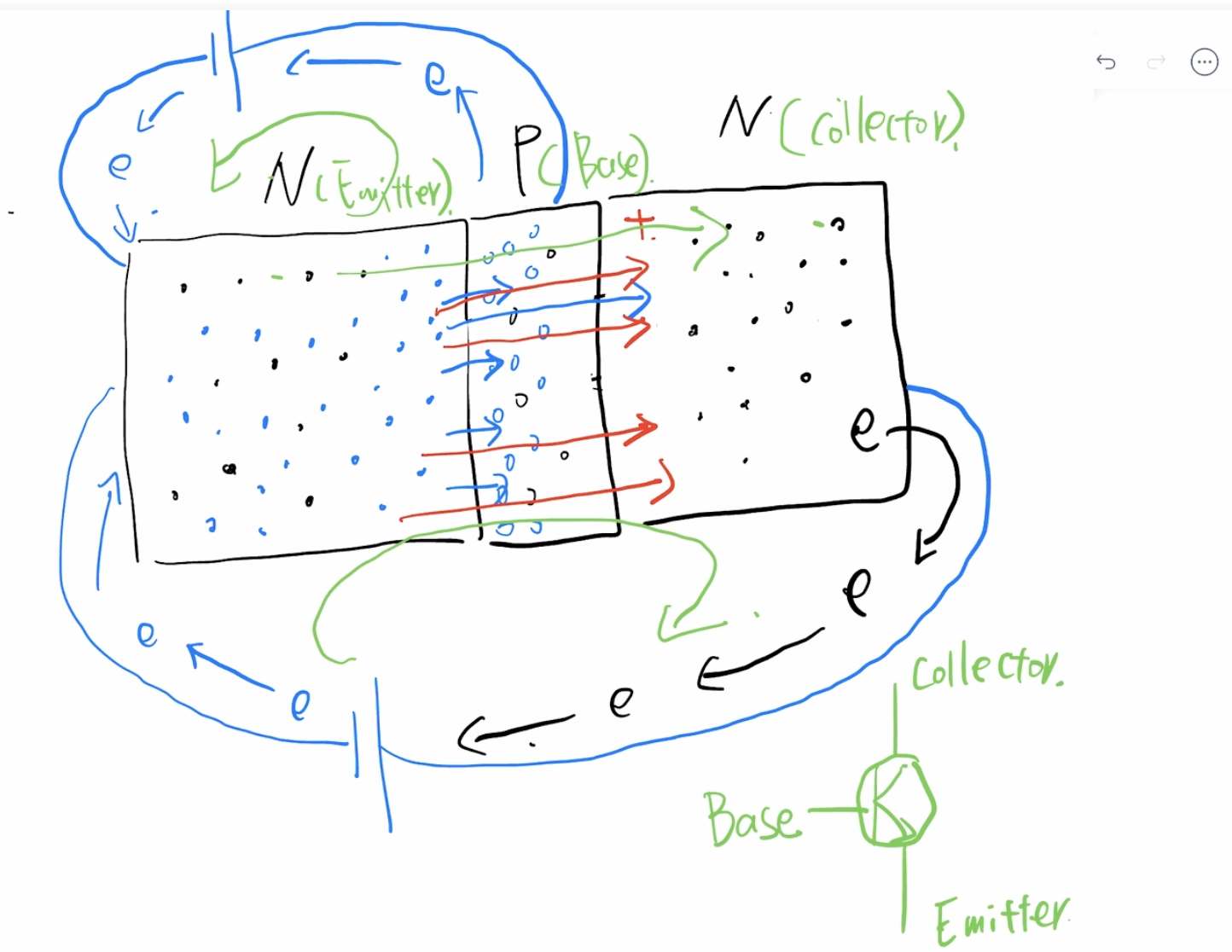

晶体管

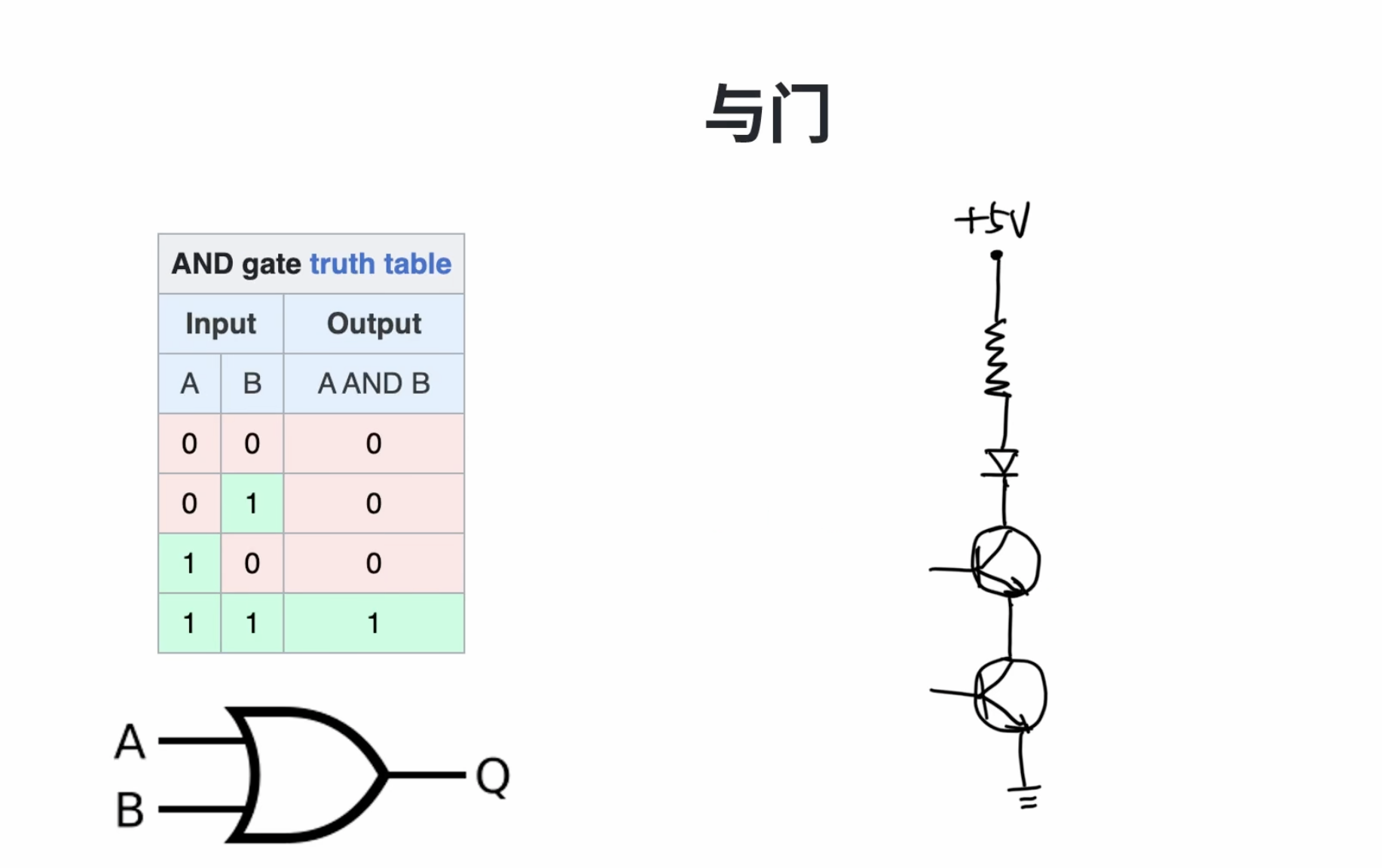

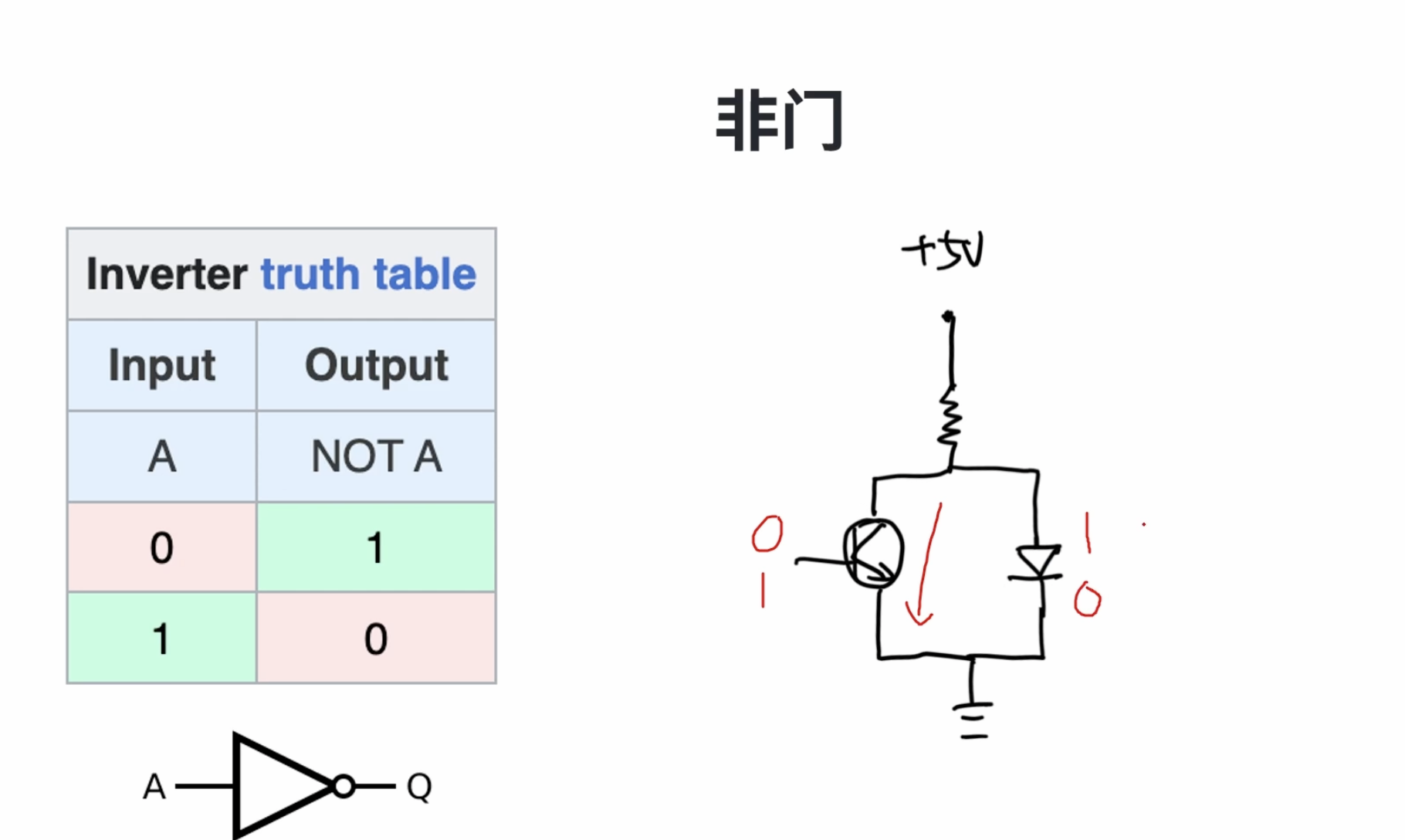

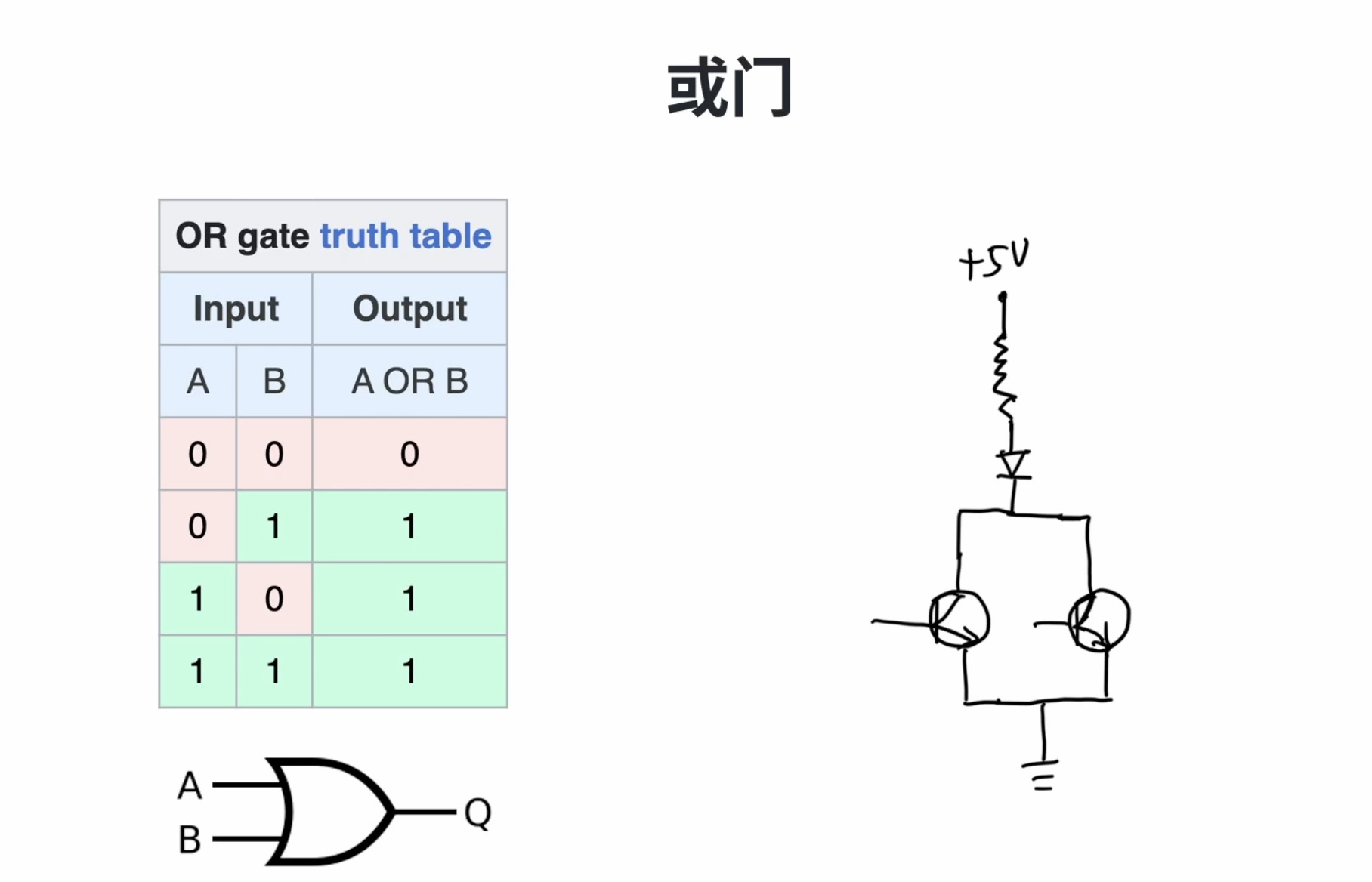

逻辑门搭建

在了解了以上基础原理之后,搭建逻辑门就很容易了

与门的搭建,即串联两个晶体管,控制端来控制是否导通,若两个晶体管的同时导通则整体电路导通,灯才会亮

非门的搭建,并联晶体管和灯泡,有两种情况

1,晶体管的控制端输入0晶体管这条电路不导通,则灯泡这边的电路导通,即输出1

2,晶体管的控制端输入1晶体管这条电路导通,则灯泡这边的电路被短路,即输出0

或门的搭建,通过灯泡串联两个并联的晶体管实现,有如下几类情况

- 1,左边晶体管导通(输入1),右边晶体管不导通(输入0),则整体电路导通,灯泡亮(输出1)

- 2,左边晶体管不导通(输入0),右边晶体管导通(输入1),则整体电路导通,灯泡亮(输出1)

- 3,左边晶体管不导通(输入0),右边晶体管不导通(输入0),则整体电路不导通被断路,灯泡不亮(输出0)

- 4,左边晶体管导通(输入1),右边晶体管导通(输入1),则整体电路导通,灯泡亮(输出1)

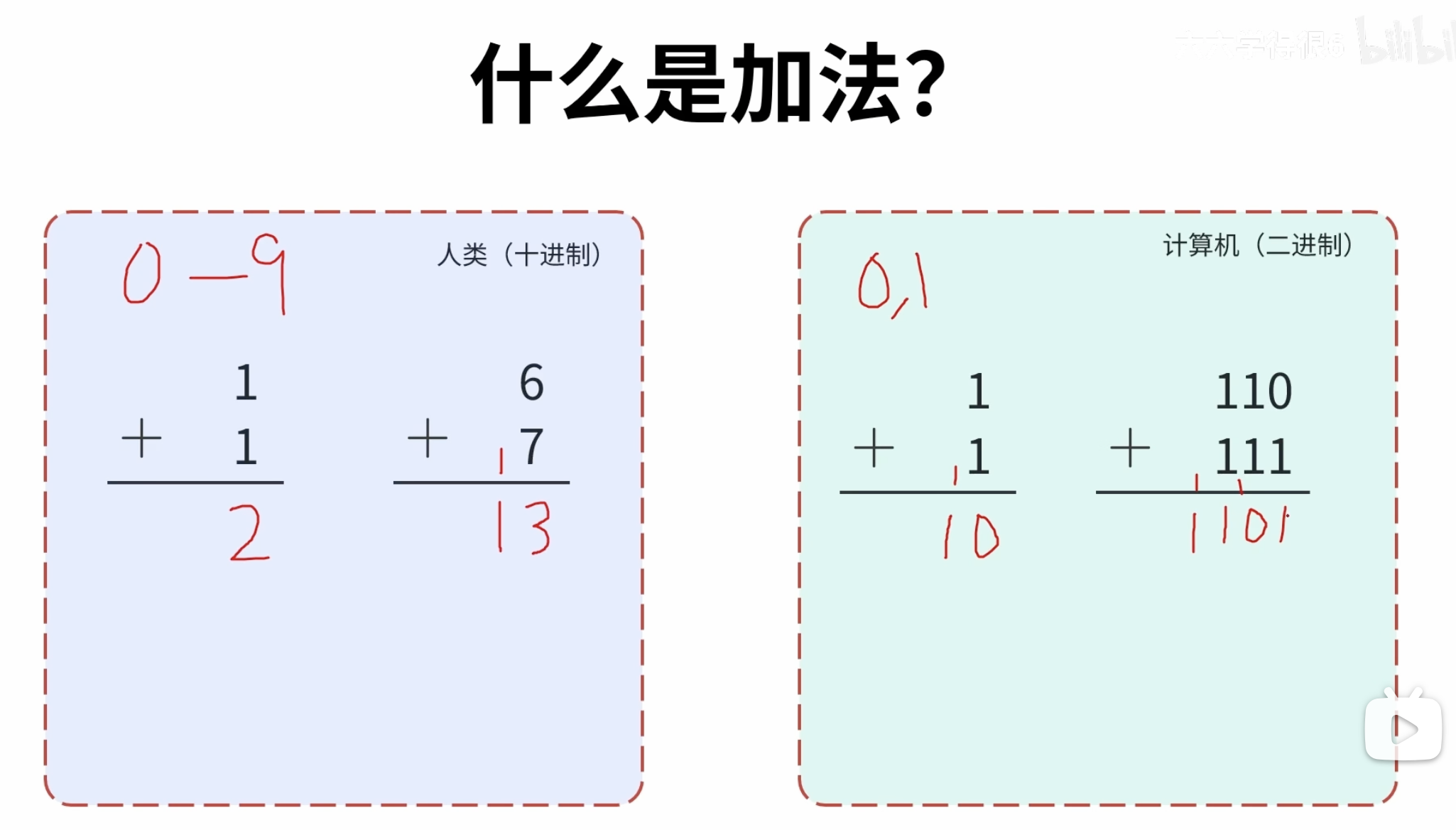

加法器

首先理解下加法原理,人类理解的加法采用的为十进制,比如1+1=2和6+7=13

在6+7这里超过10需进位,因此个位=3,十位=1 因此6+7=13

但是计算机只能给理解二进制,因此1+1,等于需进位因此 1+1=10

同理6+7 转换成二进制加法=> 110 + 111 = 1101

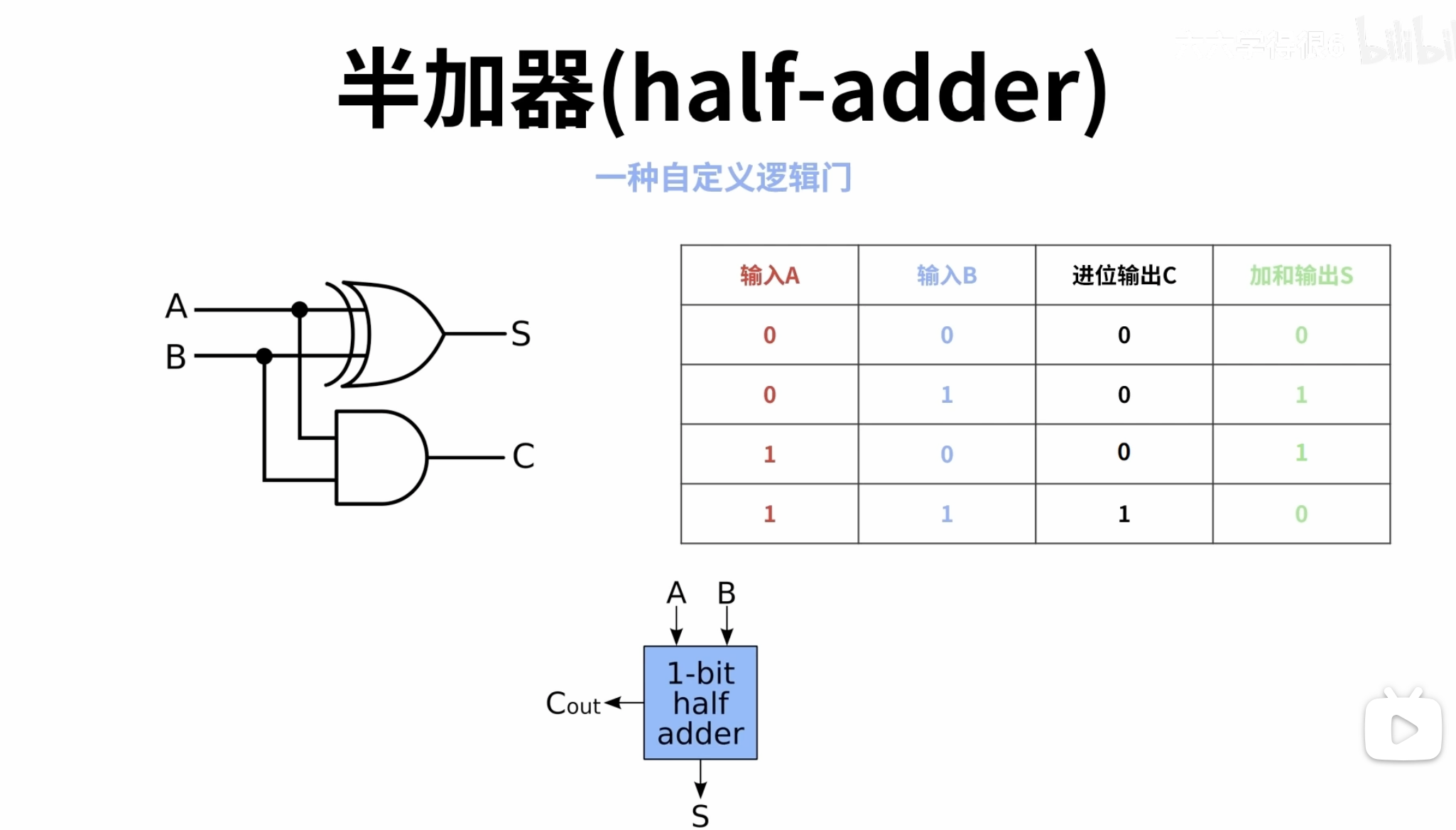

半加器

为啥称之为半加器呢,当计算1+1=10的时候,半加器可以实现,但计算110+111的时候,输出位数有4位,但半加器总共只有两位输出,因此无法实现多位数字的加法,因此称之为半加器

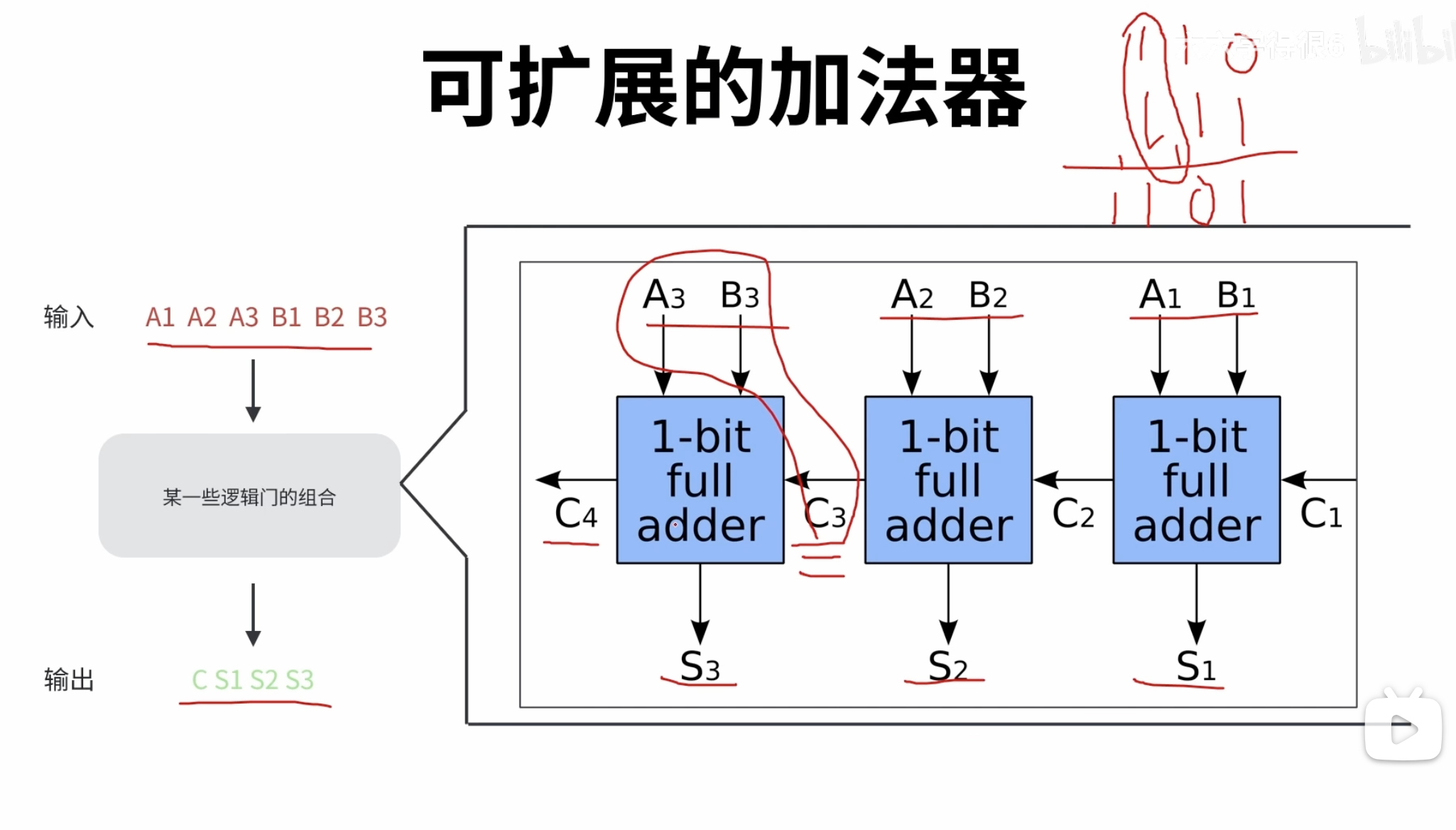

扩展加法器

将多个半加器串联,即C作为进位输出作为下一位的输入,S作为本位的输出,则实现了多位数字的加法器

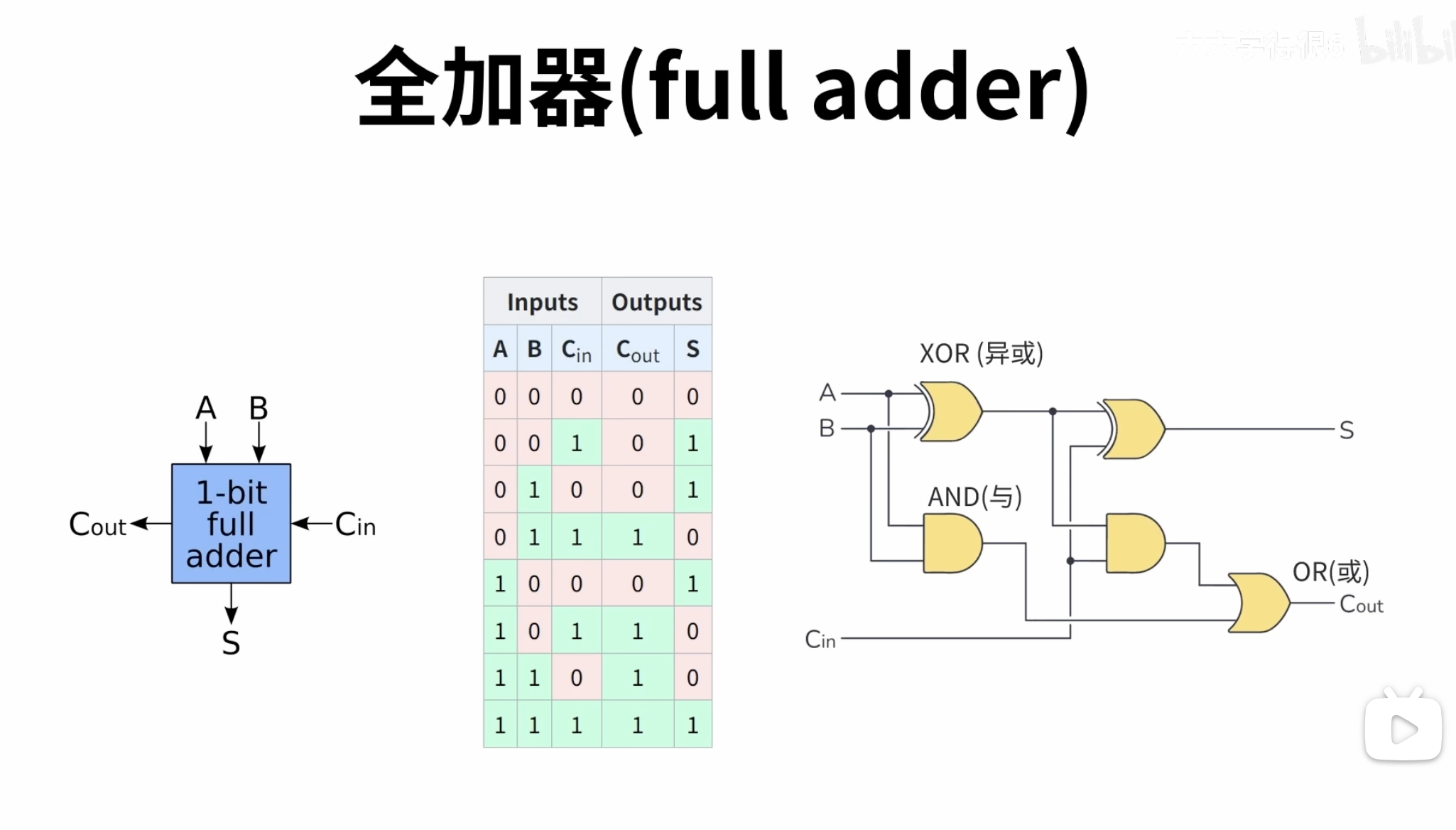

全加器

全加器逻辑门实现

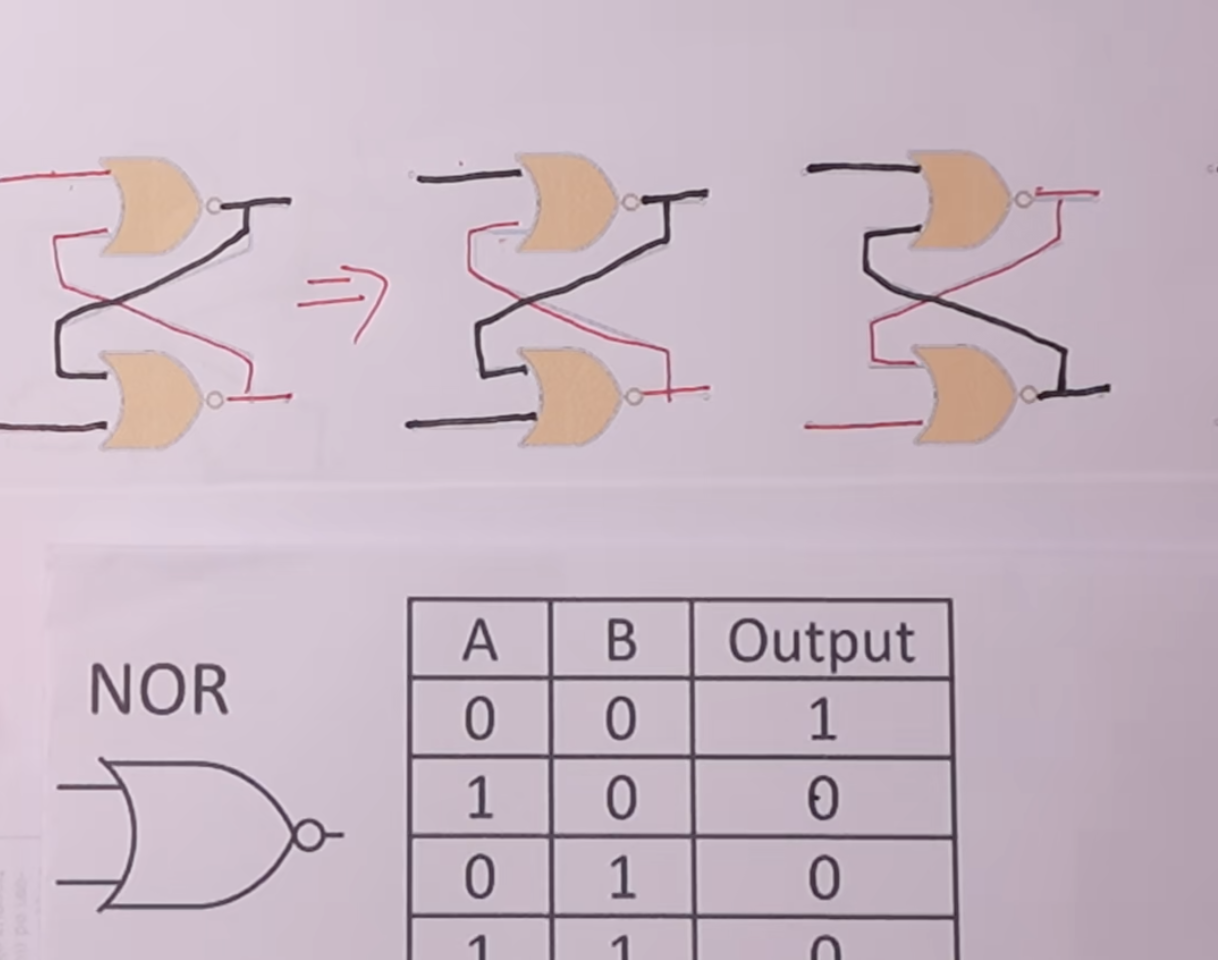

SR锁存器

为啥还需要锁存器

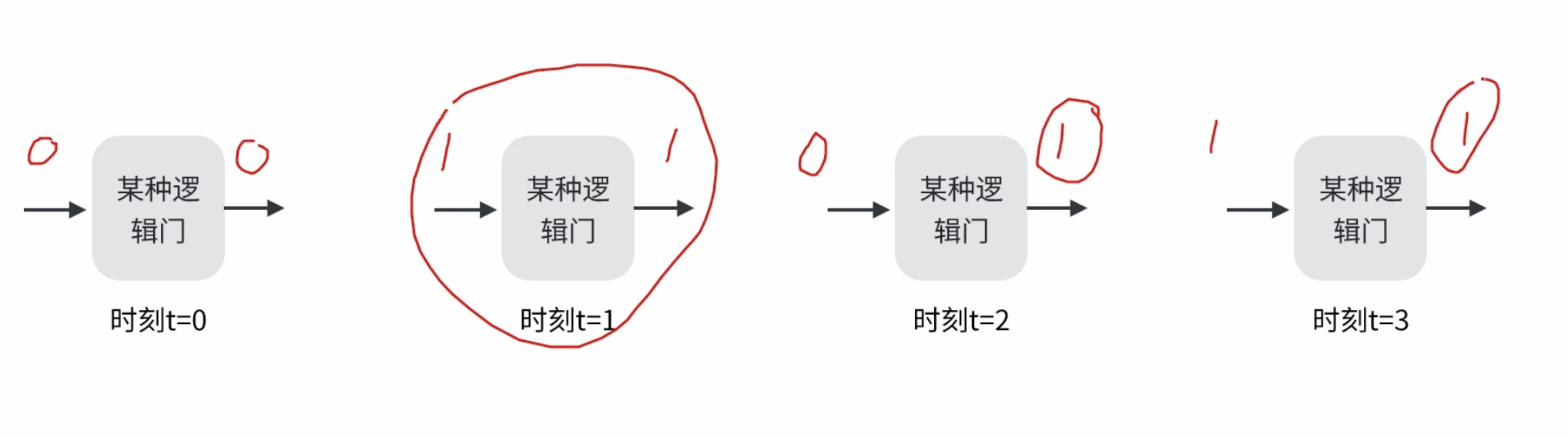

由于组合逻辑门都只有多个输入,给到多个输出,但输出永远由当前输入决定,且不会改变,一旦当前输入改变,则当前输出会改变,那么它不具有记忆功能,存储不了之前的输入

理解记忆

有记忆功能的逻辑门

比如在t=1的时刻,给定输入1,输出=1,之后不管任何输入,输出恒定不变,则说明它具有记忆功能

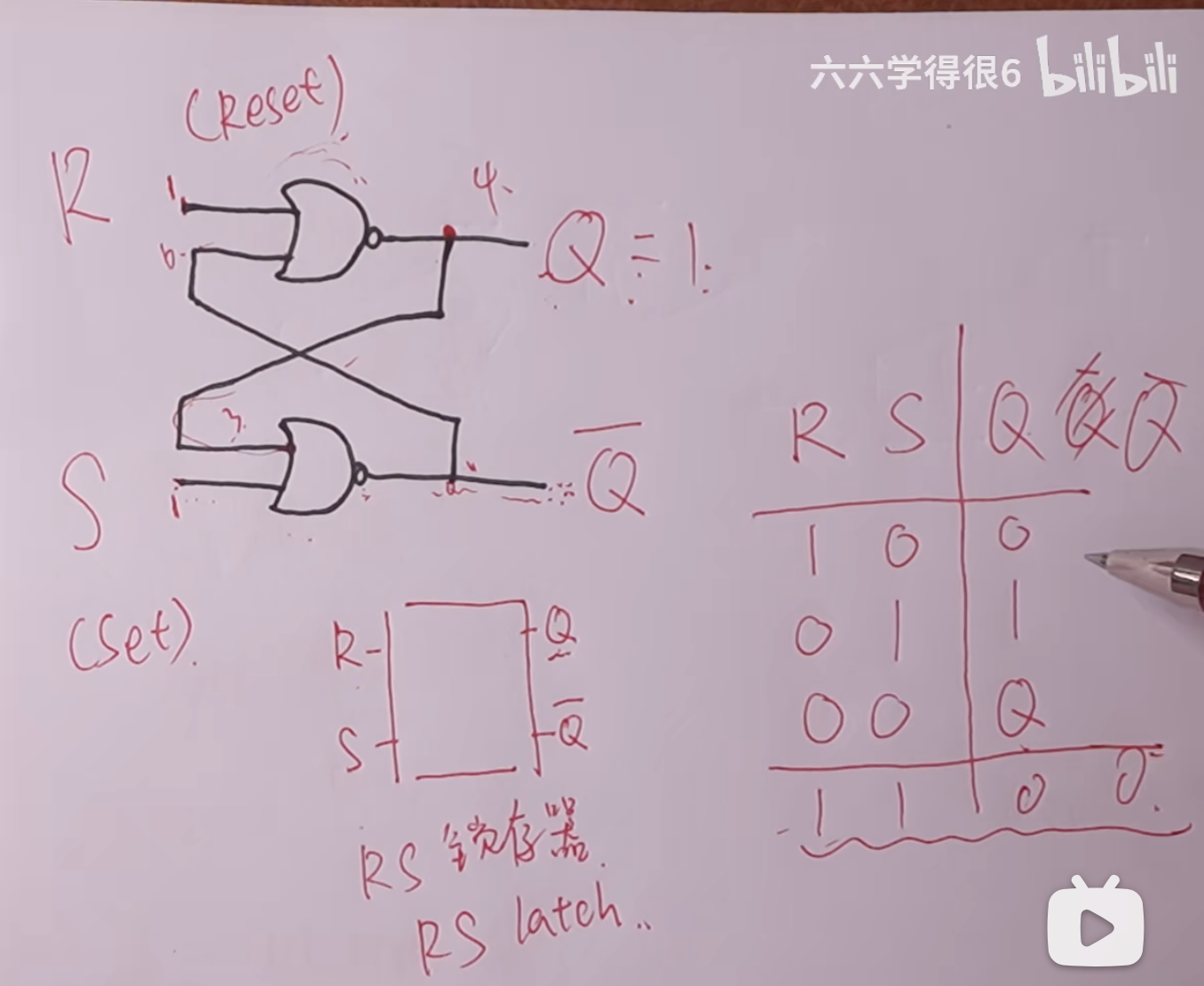

通过是S设置1,Q会输入1,因此把它称之为set端,通过Q端设置1, Q会置为0,因此称之为reset,因此把这个组合逻辑门称之为SR锁存器

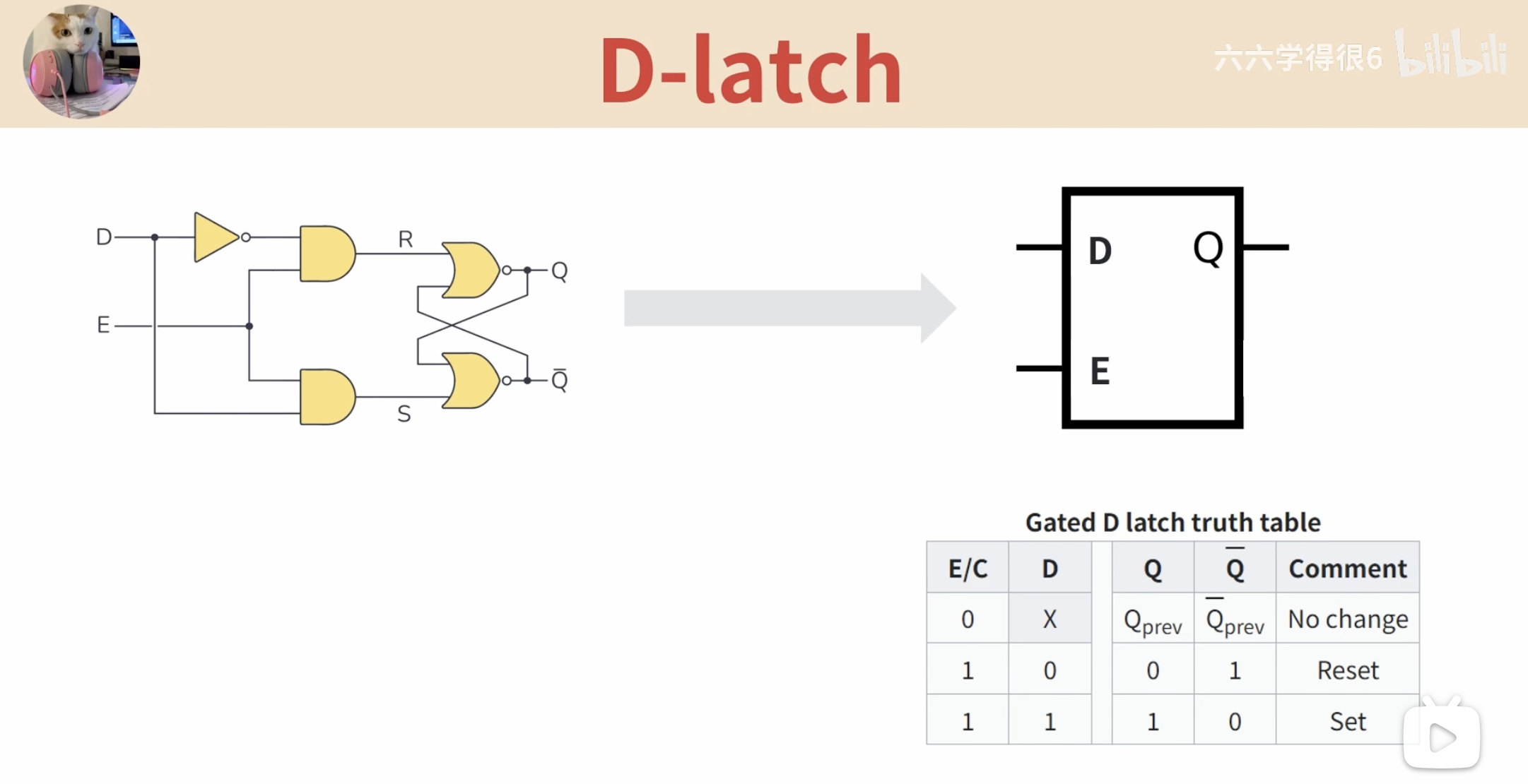

D锁存器

SR锁存器的局限

数据设置复杂,可以记忆1,但记忆不了0

没有总开关设置,无法在想要存储的时候存储,关闭存储的时候不存储

因此需加上控制位来做总开关,以及加上数据输入位,输入1,存储1,输入0,存储0

D锁存器在SR锁存器的基础上做了如下改动

- 1,控制位:加上E使能输入和与门

- 2,数据输入D串联非门

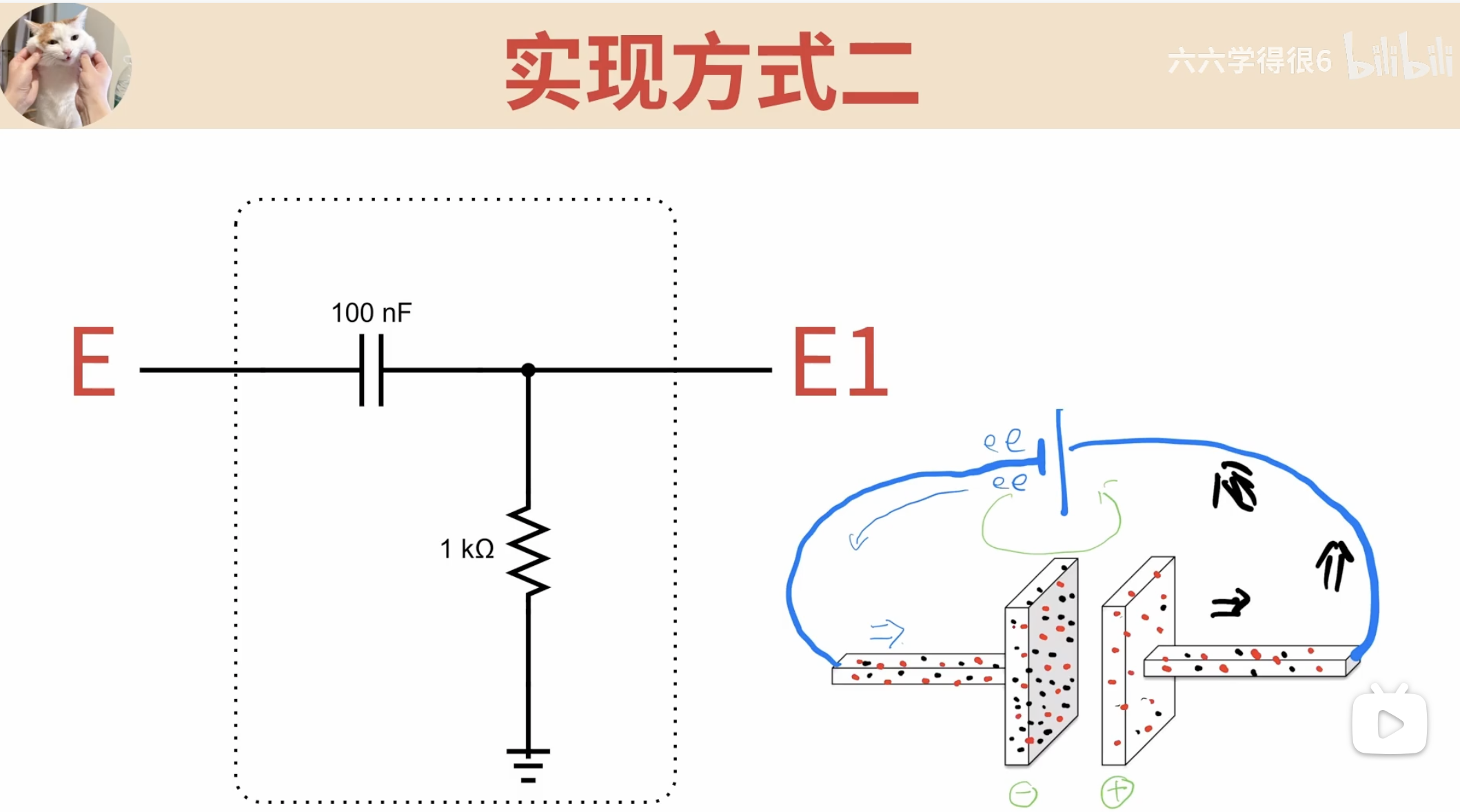

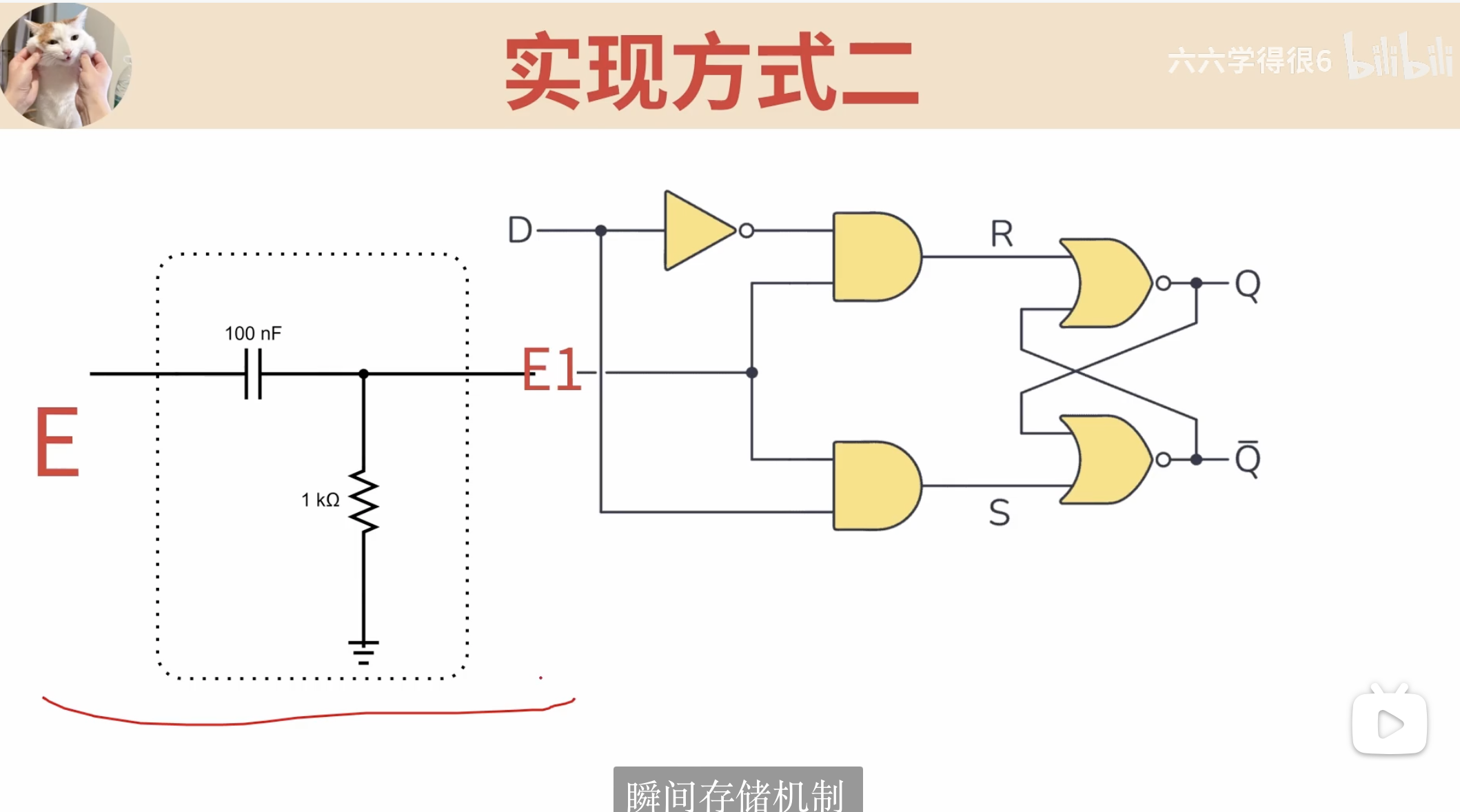

电容器

电容器可以简单地理解为可以充电和放电的元器件

通常采用电容串联电路实现RC电路从而准确控制电容充放电的时间

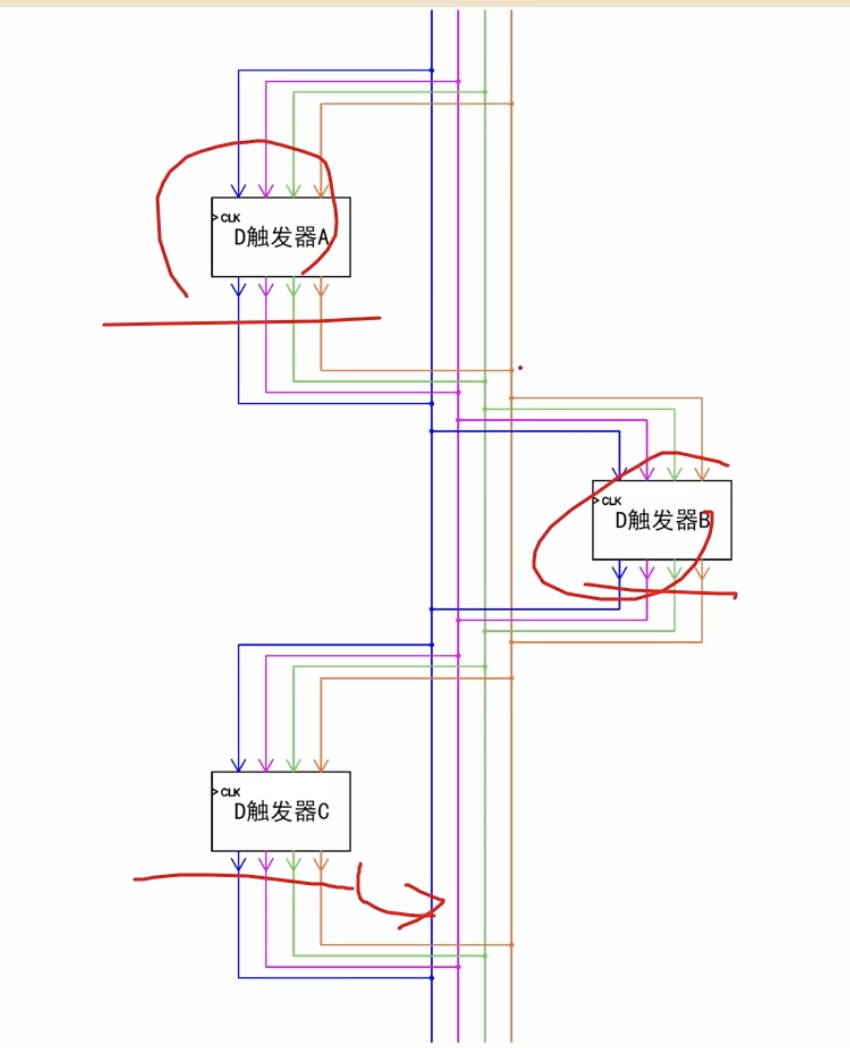

D触发器

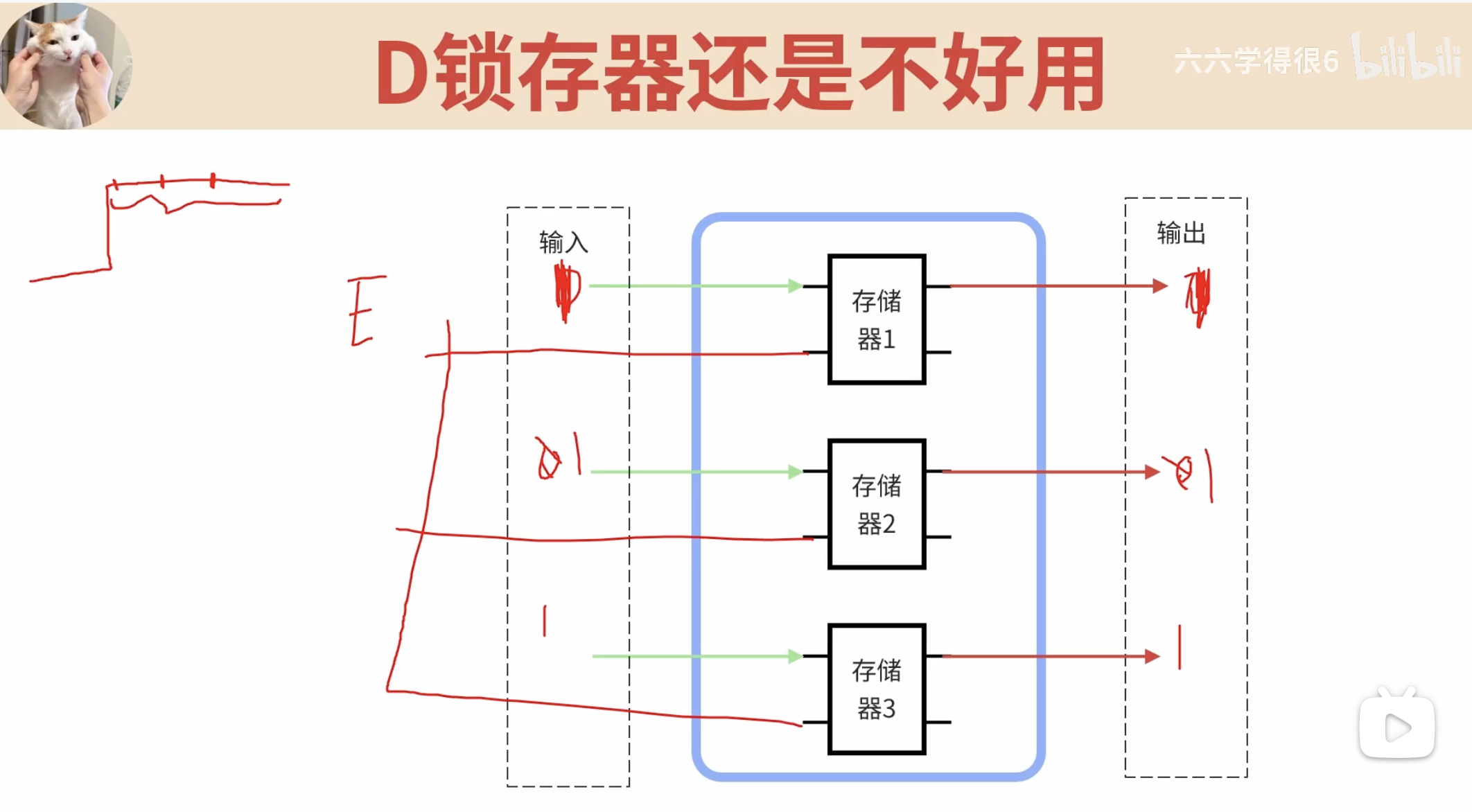

D锁存器的缺点

由于在E使能端的控制下,由于当前单位时间内输入时间内很长,很容易收到外界的影响,当某个输入任意一个改变了,输入会变得不稳定,因戏需要在一瞬间存储好时间,不给它误差的机会

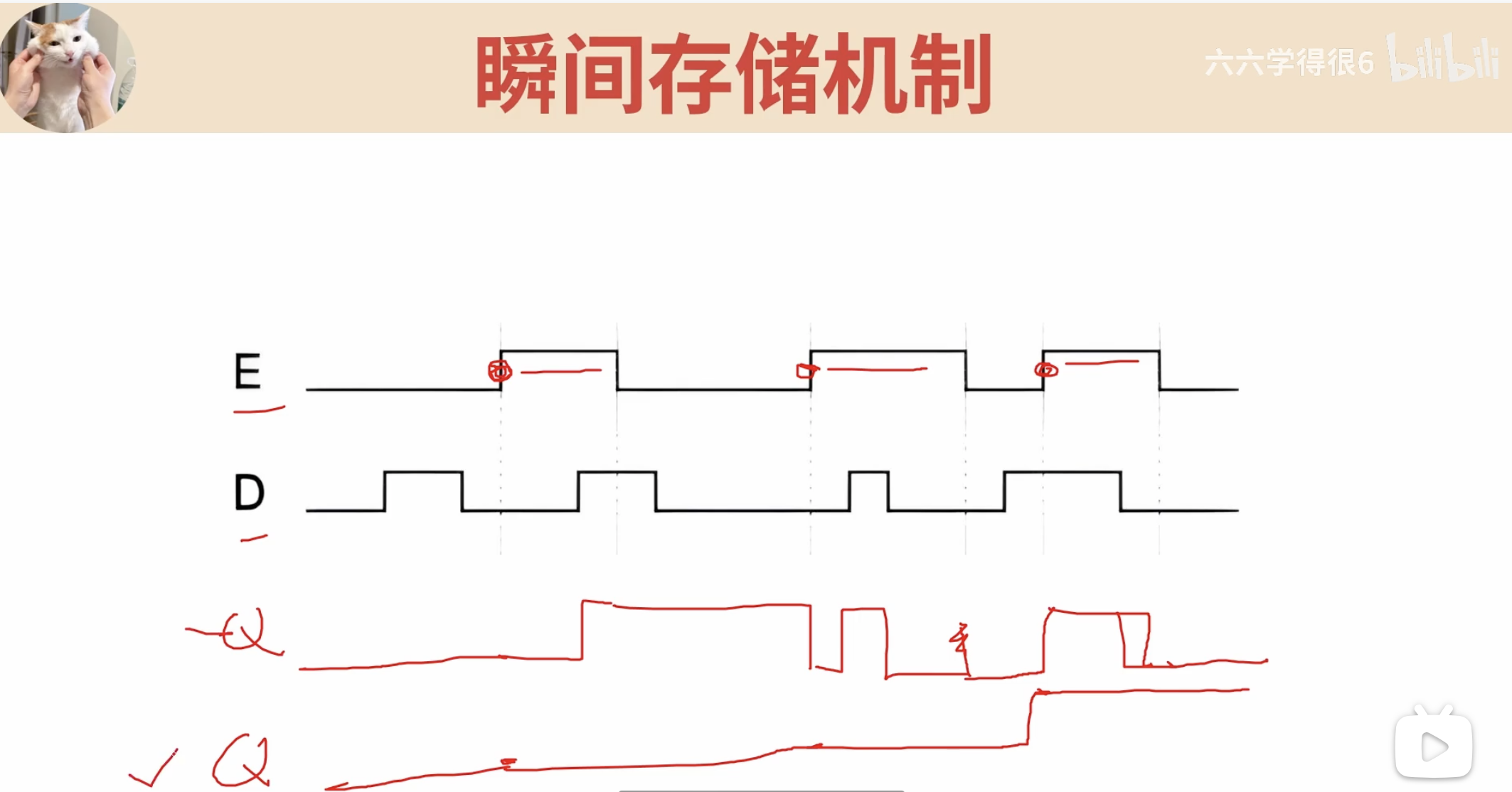

瞬间存储机制

当E使能端=1的时候,Q会随着D的输入而同步输出

但是现在需要在E=1的瞬间,保持D的输入,其它的时间不变,因此理想的Q输出为最后一条Q,而不是倒数第二条Q

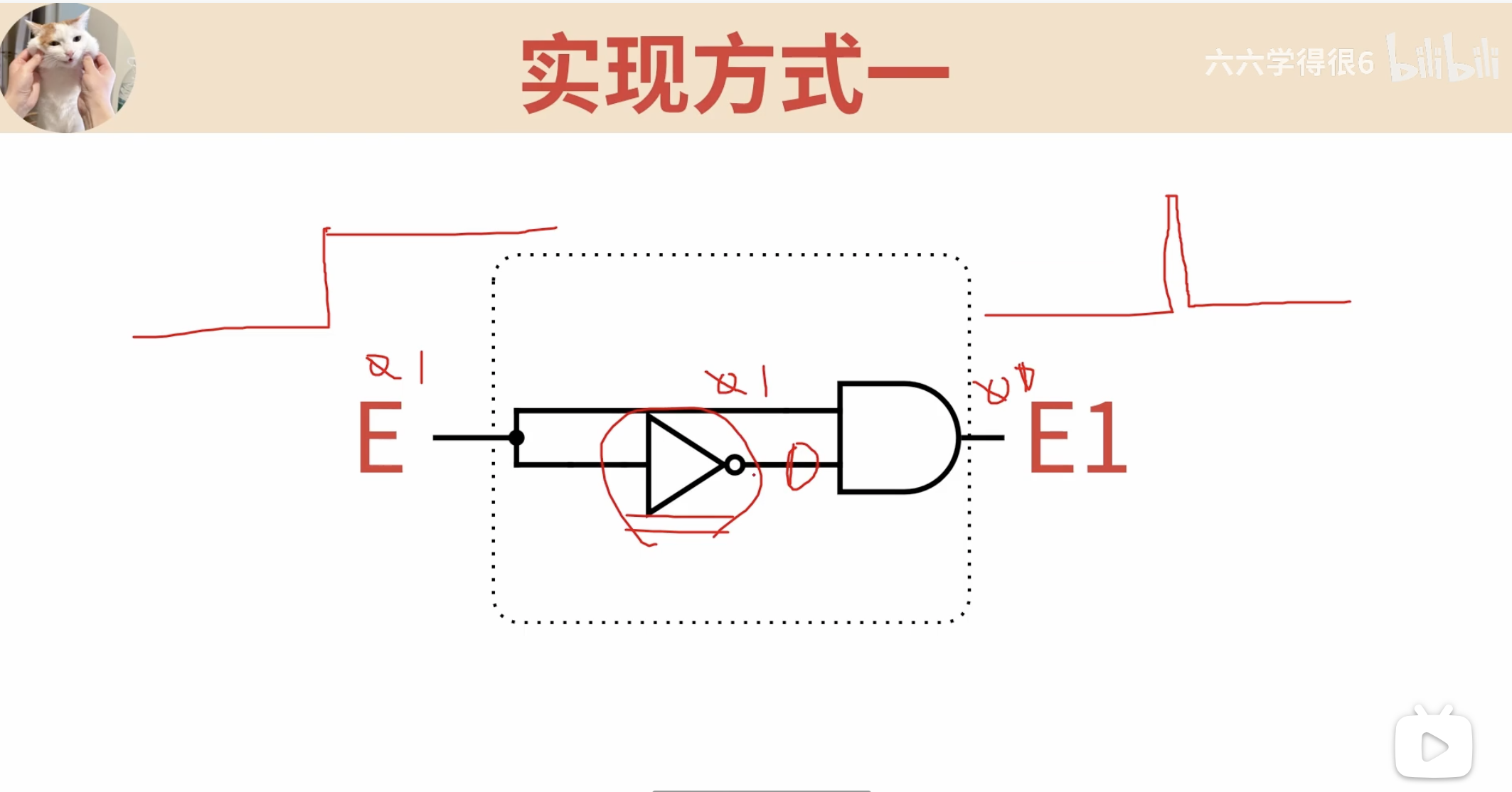

门电路实现

当E=1的时候 通过非门和与门 ,与门上边输入=1,下边输入由于非门的时间延迟仍然=1,因此E1=1

当时间延迟过了,与门的第二个输入变成了0,因此E1=0,因此实现了瞬间存储功能

但这个非门的延迟时间不可控

基于电容实现

利用电容的特点完成瞬间存储

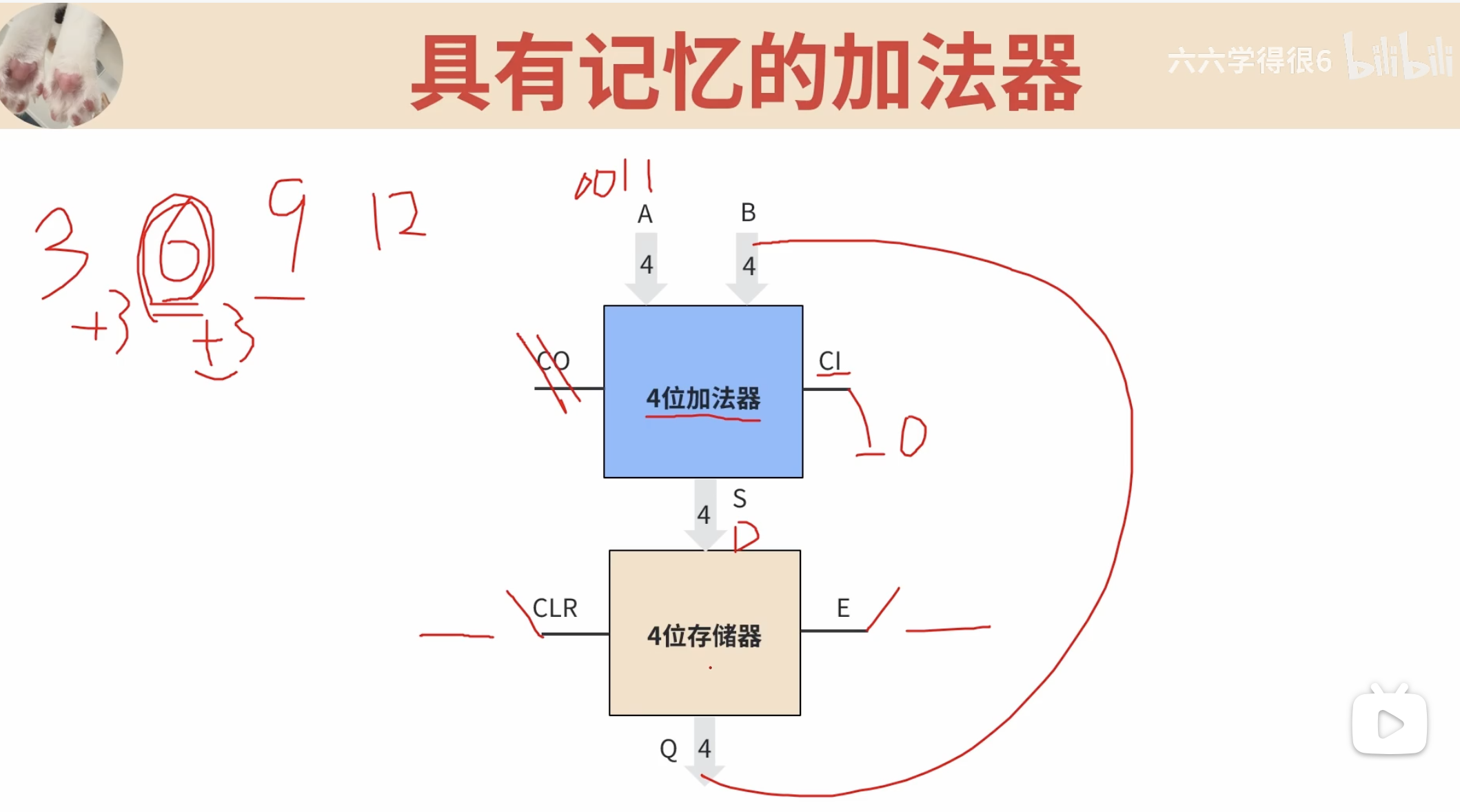

具有记忆的加法器

原理为将具有记忆的存储器的输出端再接回道加法器的输入端

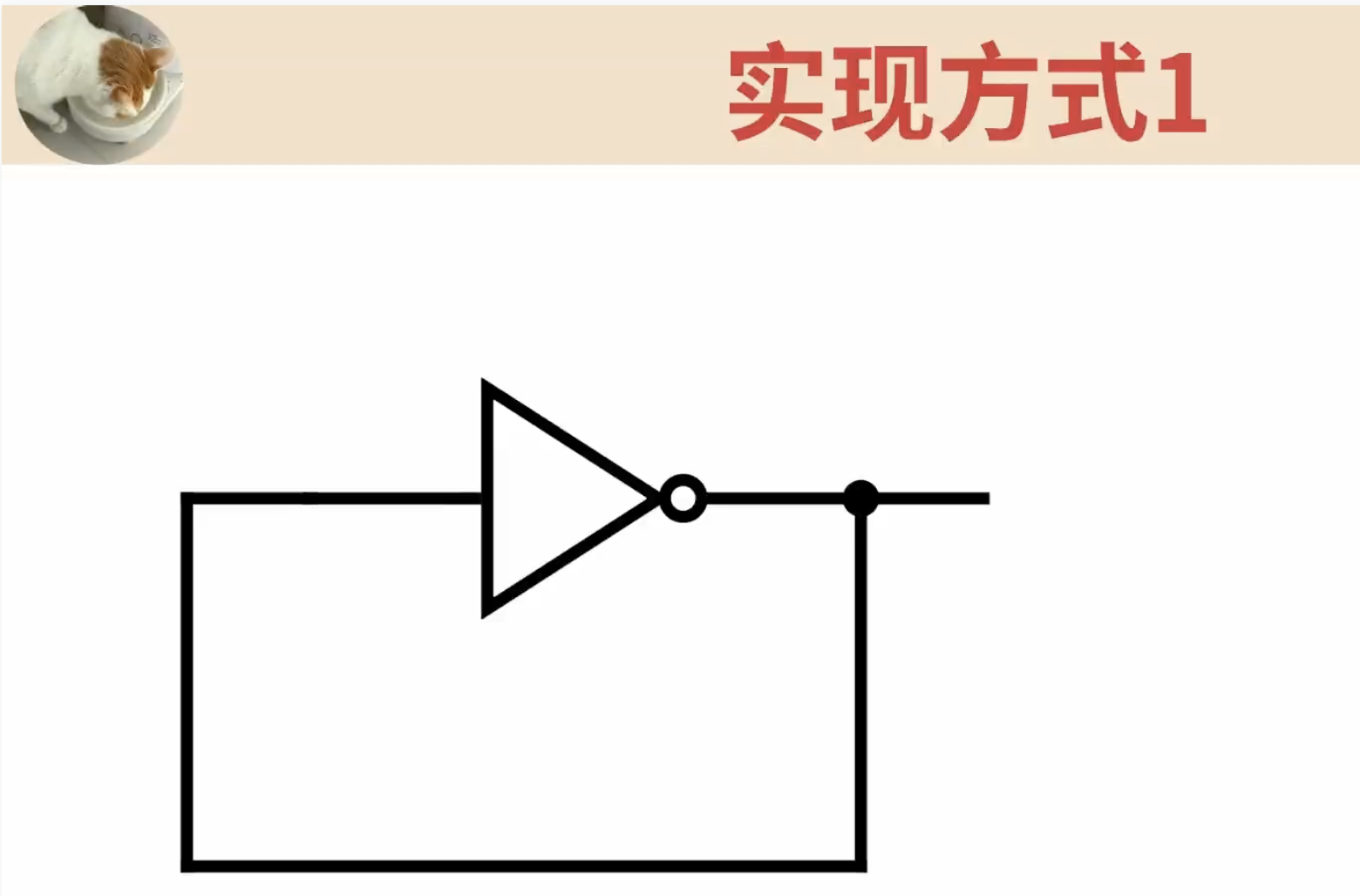

时钟原理

时钟主要用来计算机内部的触发协作,比如计算机在哪个时间节点做哪些操作

非门实现的时钟,当一开始输入=1,输出=0,输出0又返回到输入通过非门,此时输出就变成了1,循环往复输出的规律=> 0、1、0

但0和1持续的时间不可控

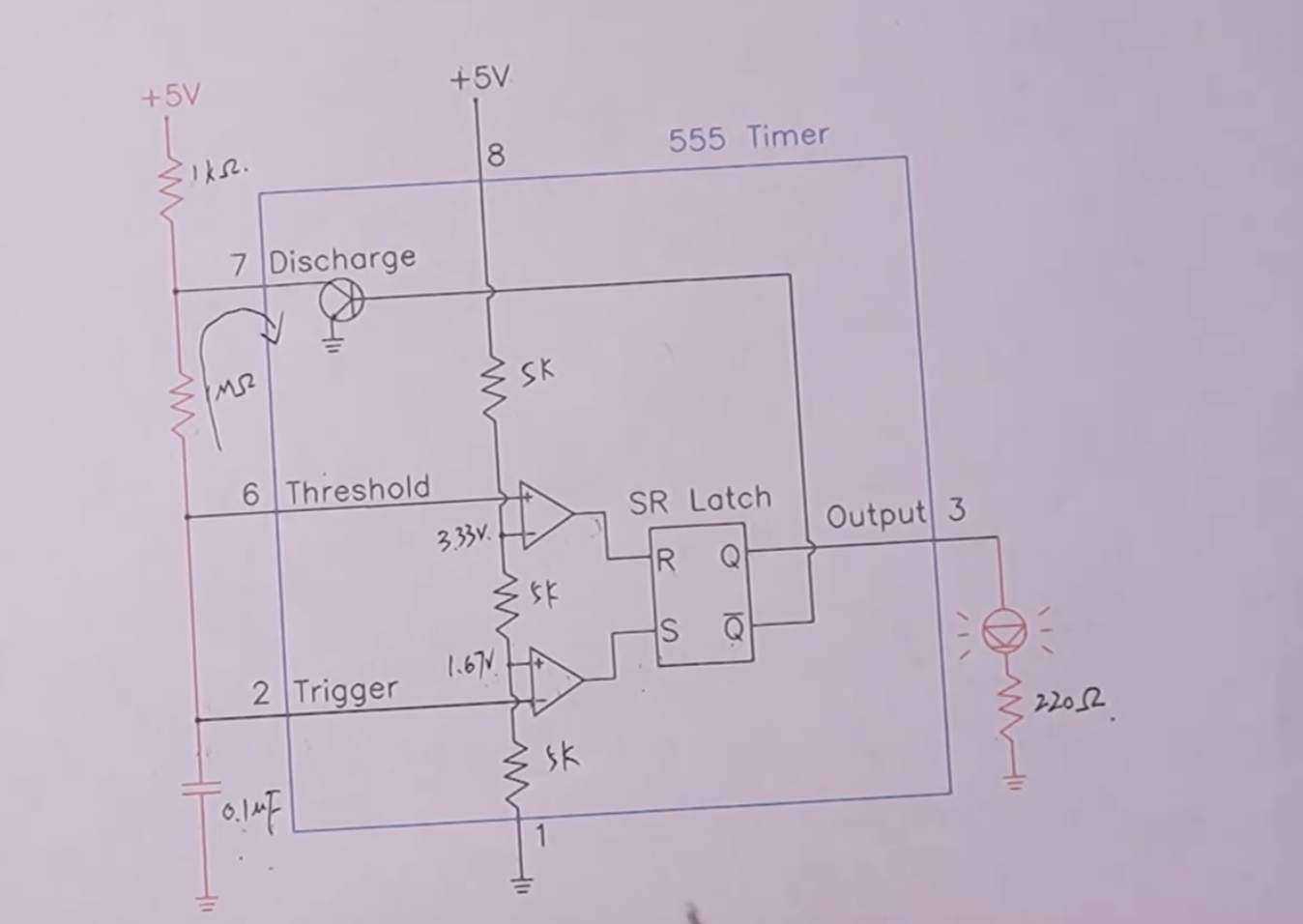

因此还有更好的实现,即通过555触发器来实现

其中内部用到了很重要的电容RC电路定时充放电,同时利用了比较器,当正极电压大于负极电压才会导通,具体的原理可以参考555的原理

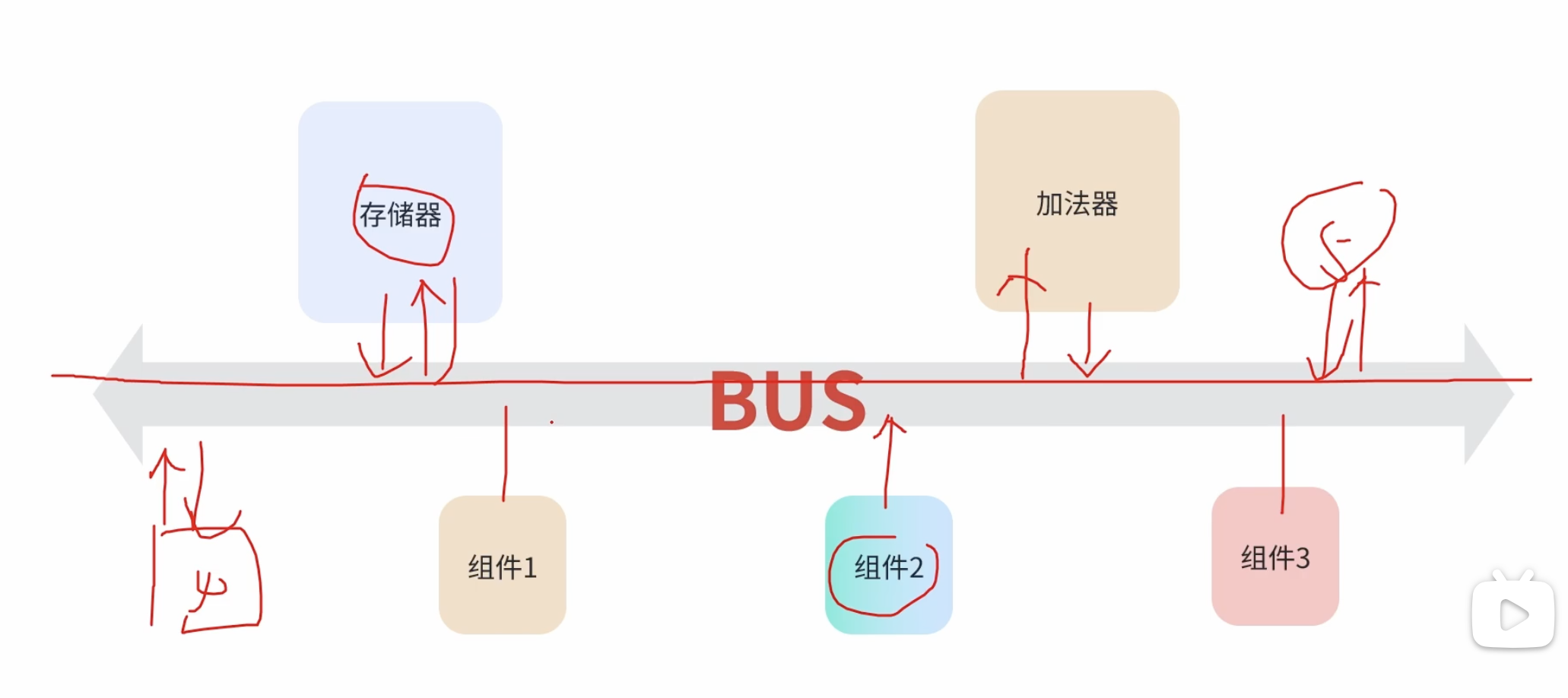

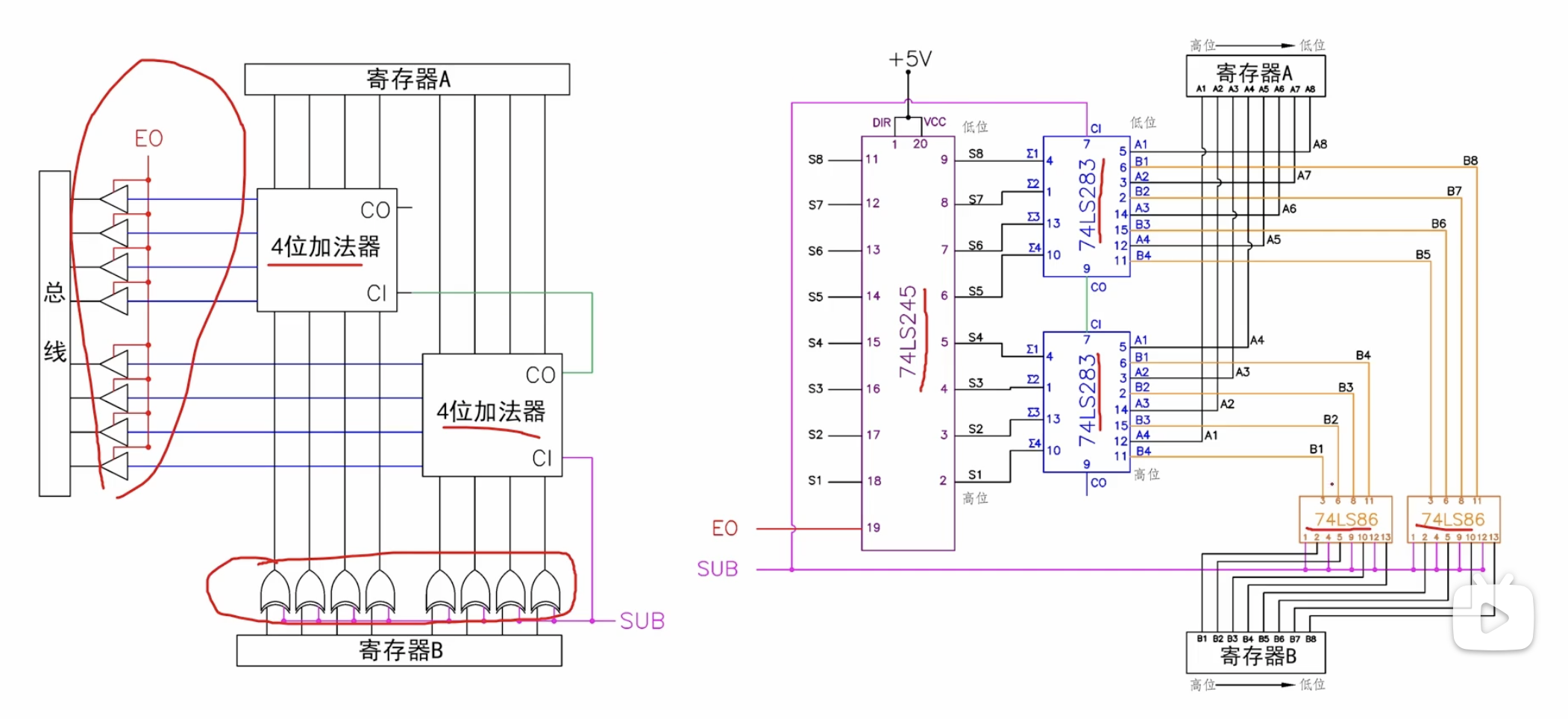

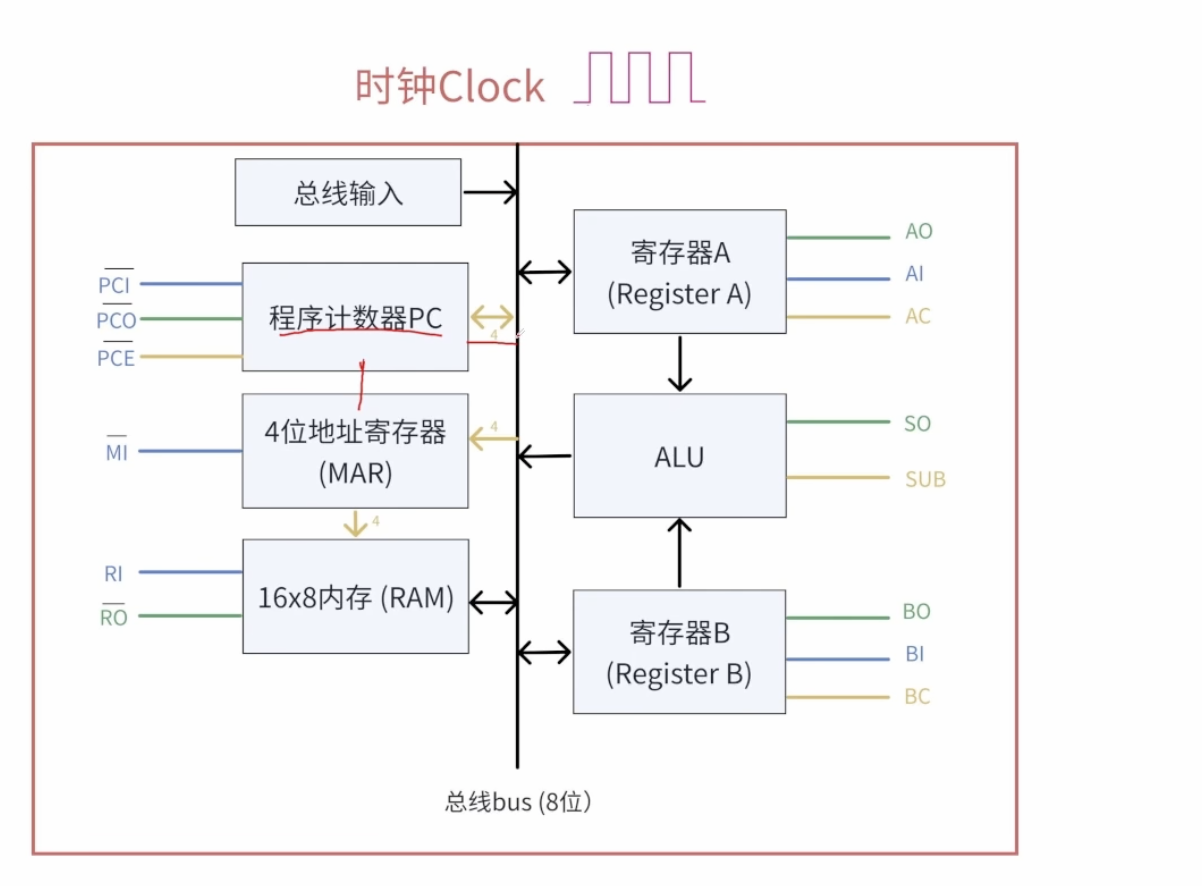

总线原理

简单地来将,总线即为了统一管理计算机内部所有的元器件,各个存储器、寄存器、内存等通过总线来传递数据,部分元器件输出数据到总线,部分元器件接受总线数据的输入

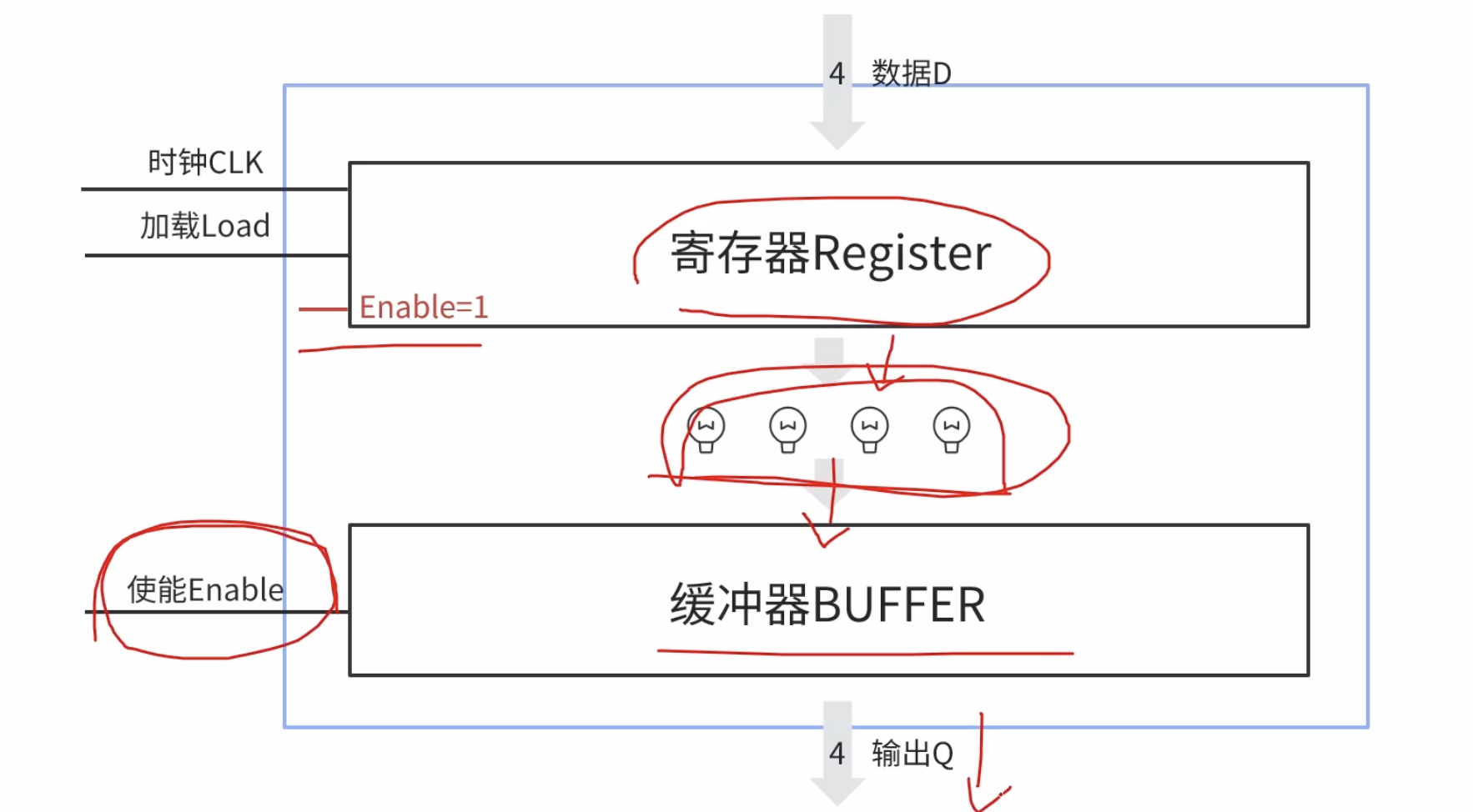

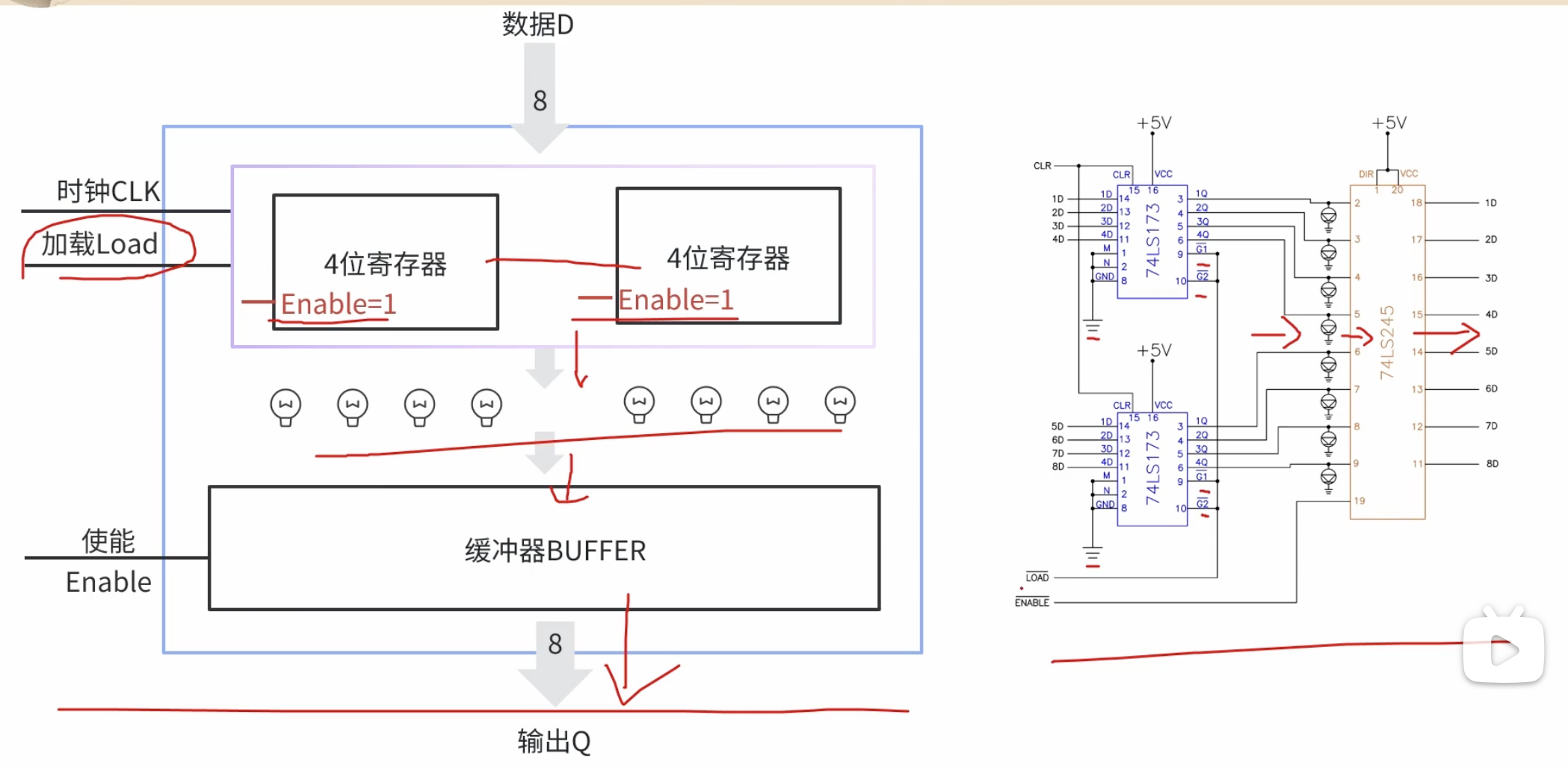

寄存器

D触发器存在的问题一:众多触发器,谁来读取此时的总线数据呢,之前的D触发器无法实现控制制定触发器谁来接受总线数据

解决问题一:因此在原有的触发器加上load加载端,当load=1,触发器接受总线数据,load=0,触发器不接受总线的数据

D触发器存在的问题二:众多触发器都输出了数据,此时输出哪个触发器的数据到总线呢

解决问题二:在触发器加上enable输出使能端,当enable=1的时候触发器才输出数据到总线

改良的触发器称之为寄存器

但此时的寄存器还存在如下问题:

- 无法观察到每个寄存器的输入输出到底是多少

- 有效位数太少了,输入输出只有4位

解决怎样观察输入输出:加上缓冲器,在缓冲期和寄存器之间加上灯泡,用灯泡观察寄存器的存储数据

解决有效位数太少:串联多位寄存器解决

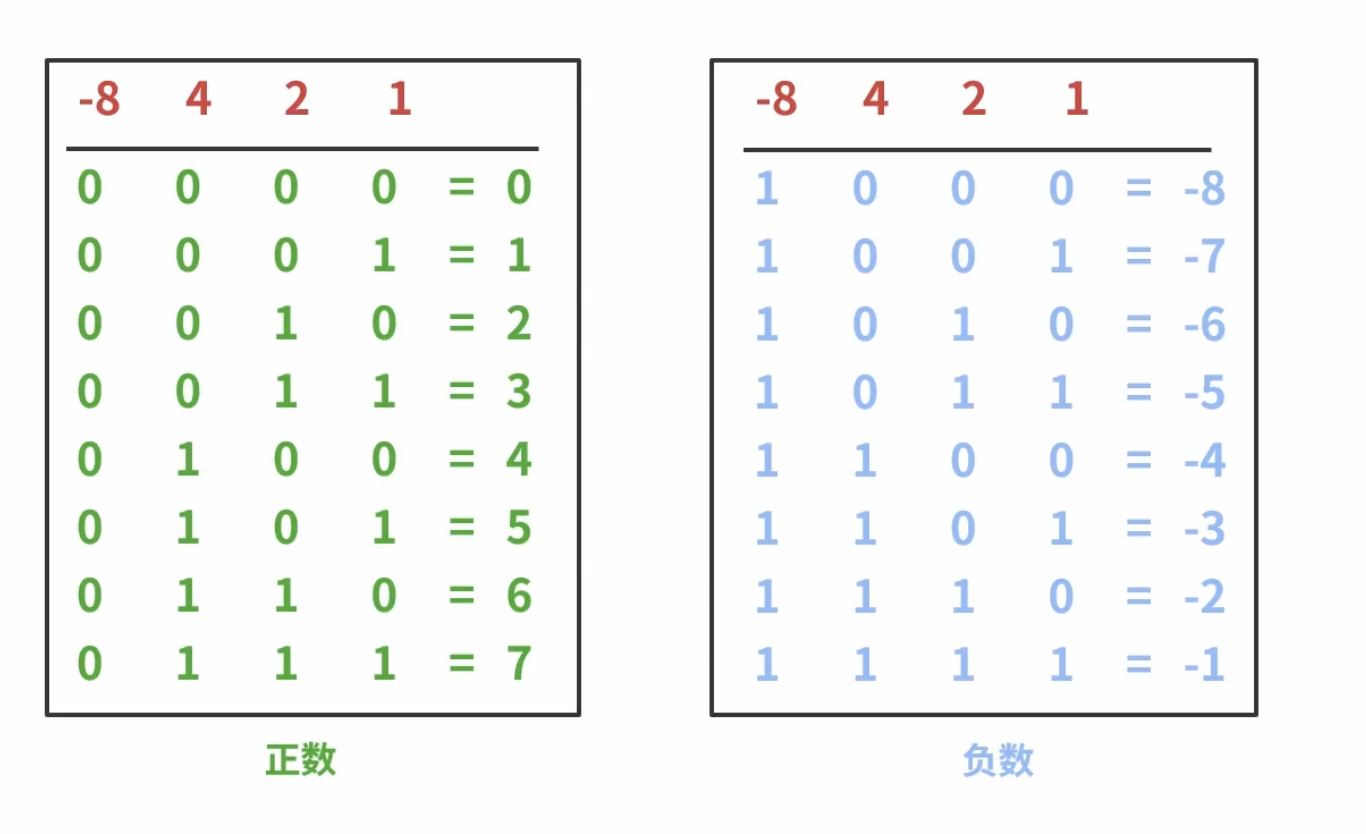

ALU

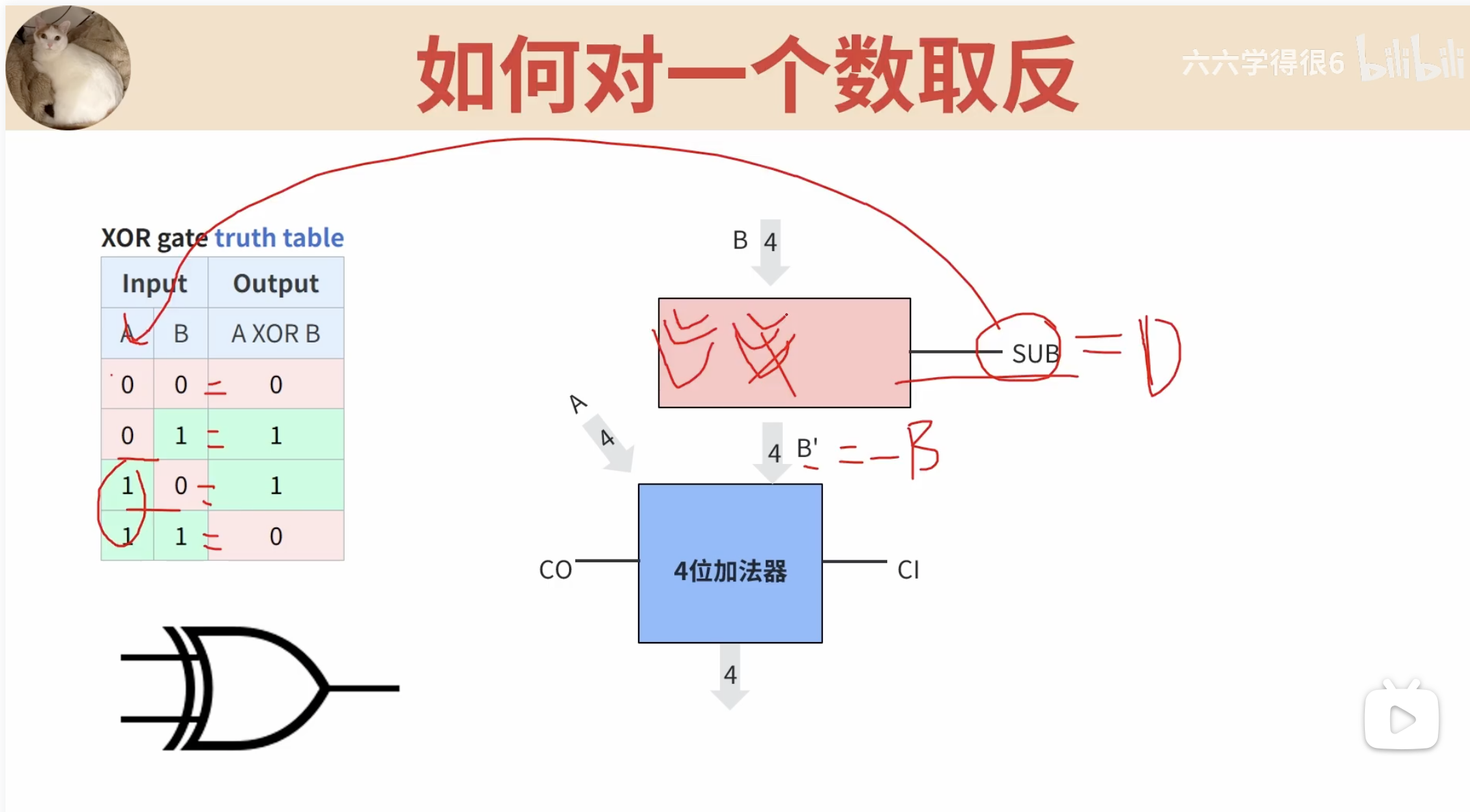

ALU即算数逻辑单元,之前已经实现了加法,ALU包括加减乘除,加法已实现,乘法和加法的本质原理差不多,减法和除法本质原理差不多,则当前只需解决怎样实现减法功能

例如,6-2 可以换成 6+ (-2) 此时它仍然为加法,重点在于怎样把2变成-2

规定最高位等于负数,比如4位二进制,最高表达-8,此时的二进制则可以表达负数

举例:6-2

6=0110 -2=1110

6-2= 0100 此时算出来=4

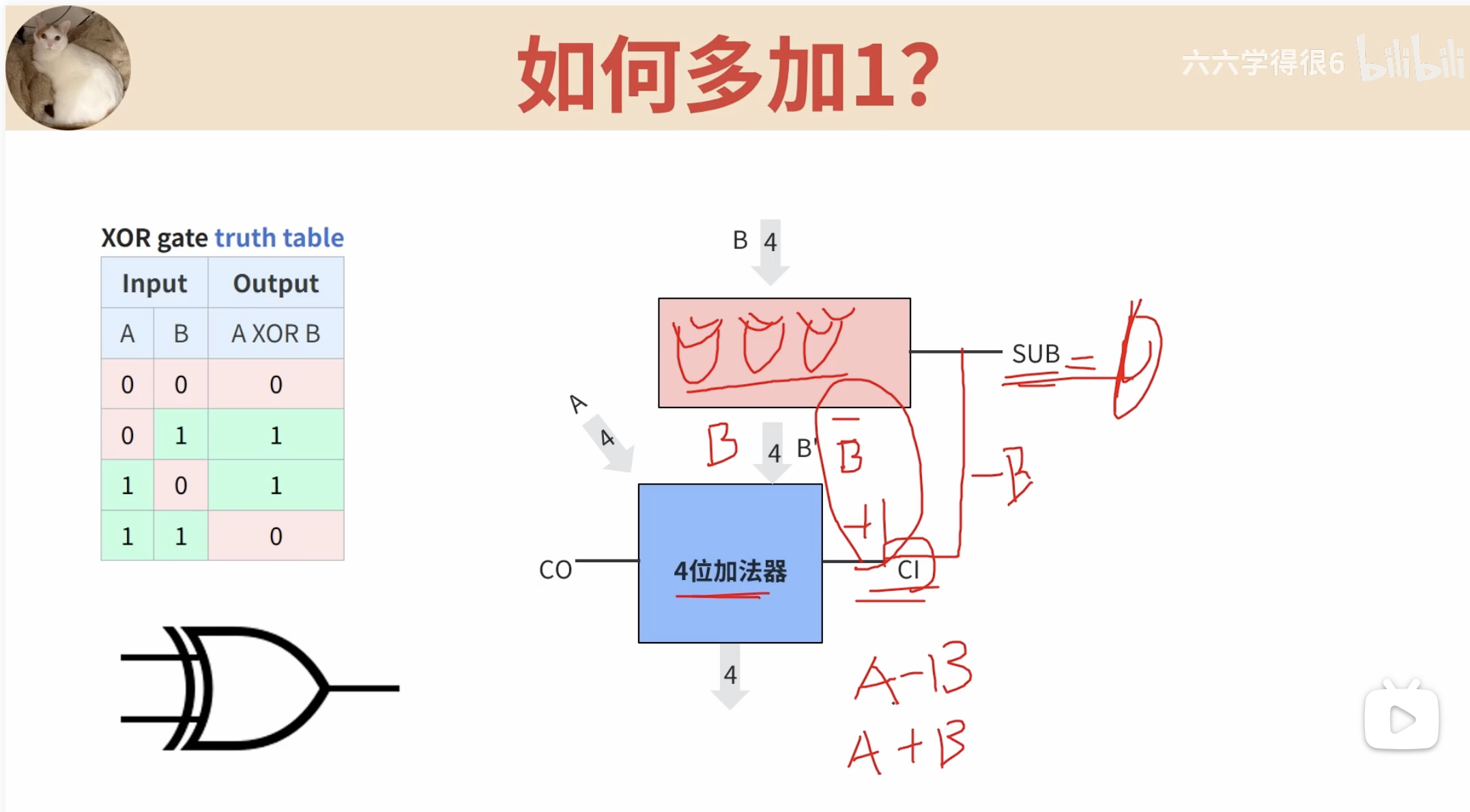

规律:负数二进制=正数取反+1

取反:采用异或门+sub控制端实现

+1操作:sub的输出直接接到Cl端,sub=1 即计算减法

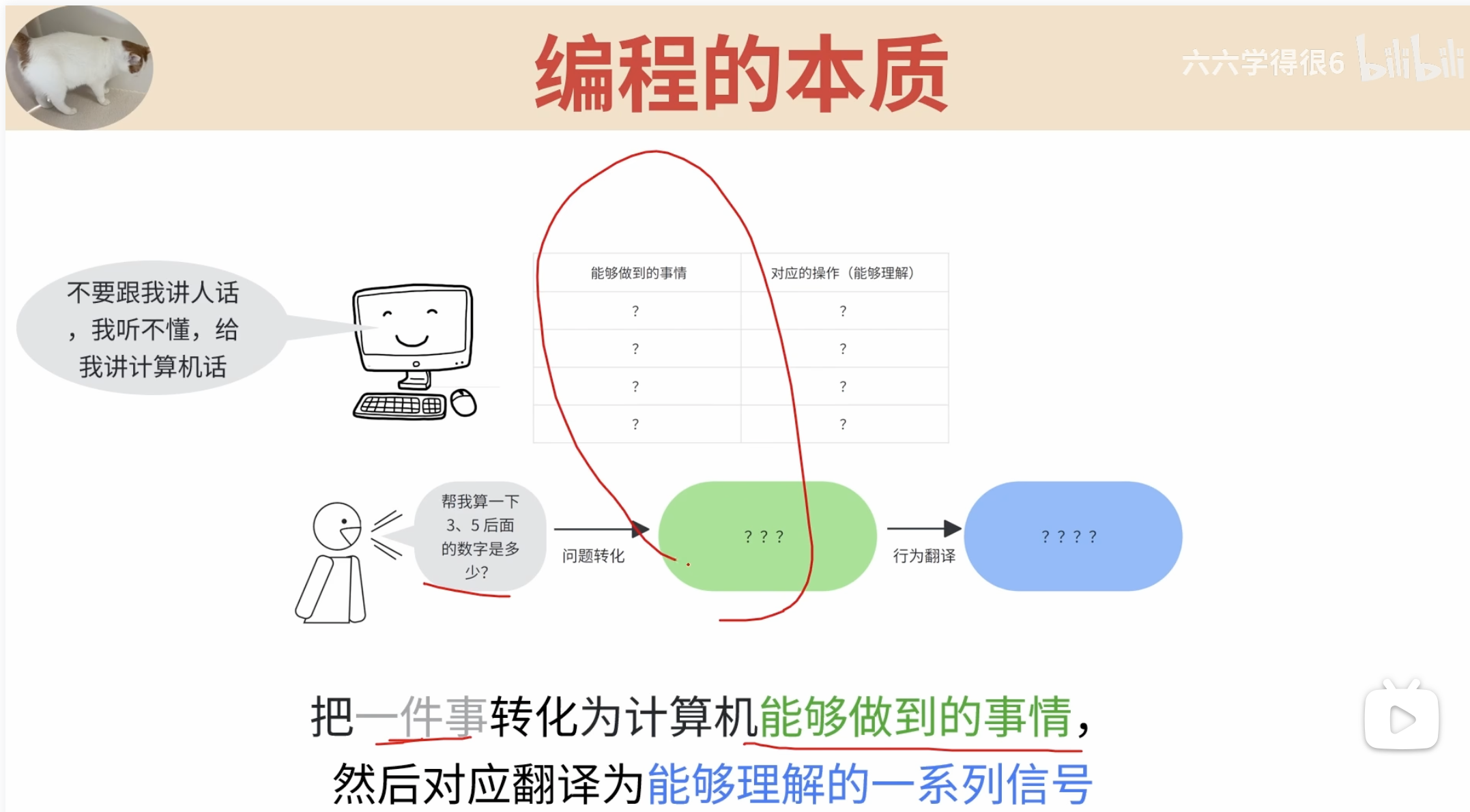

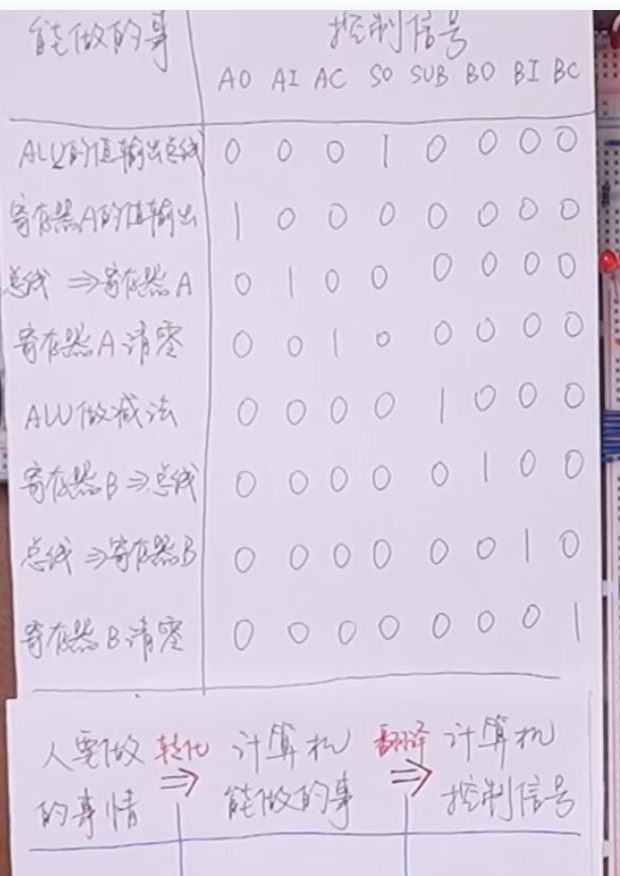

编程的本质

把计算机能够做的事情翻译成计算机能够理解的二进制

内存

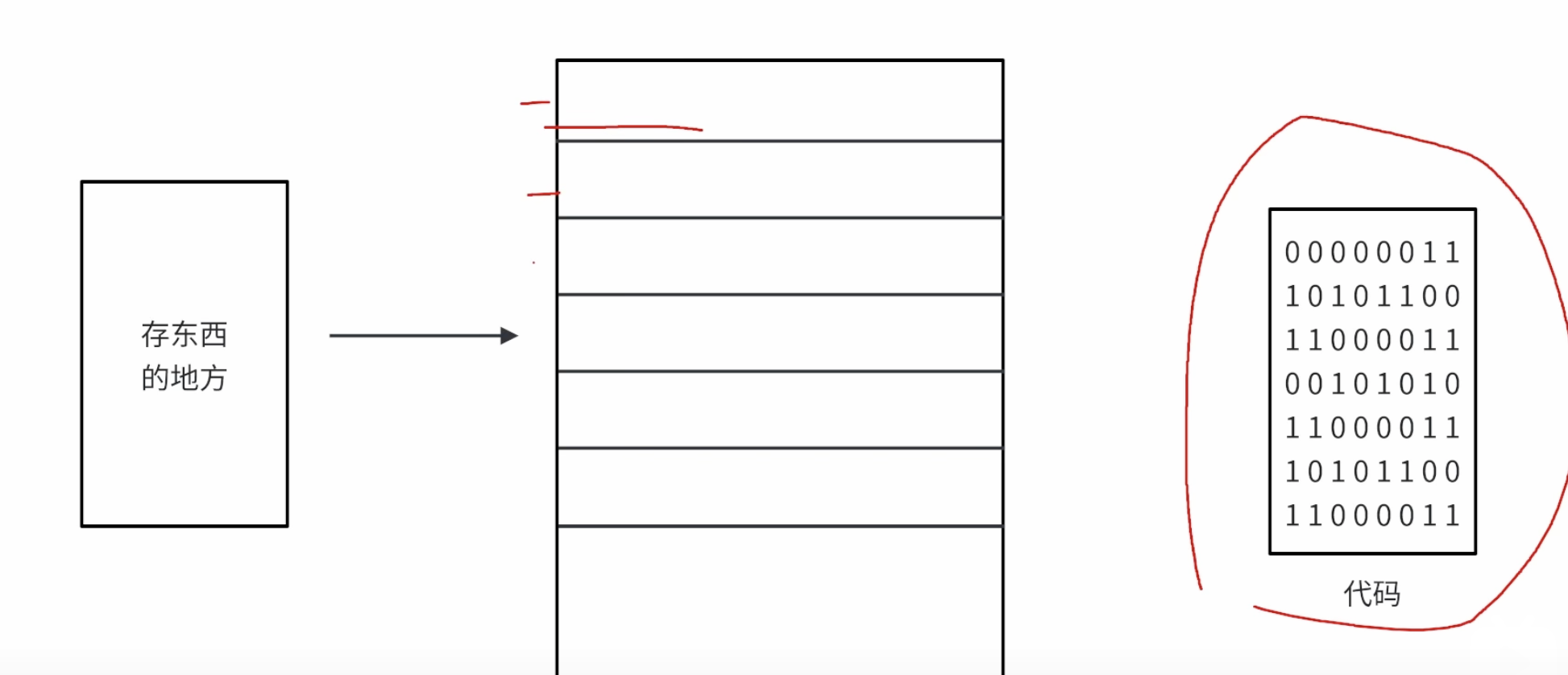

指令得存储在某个地方,给到后续某个元器件来读取

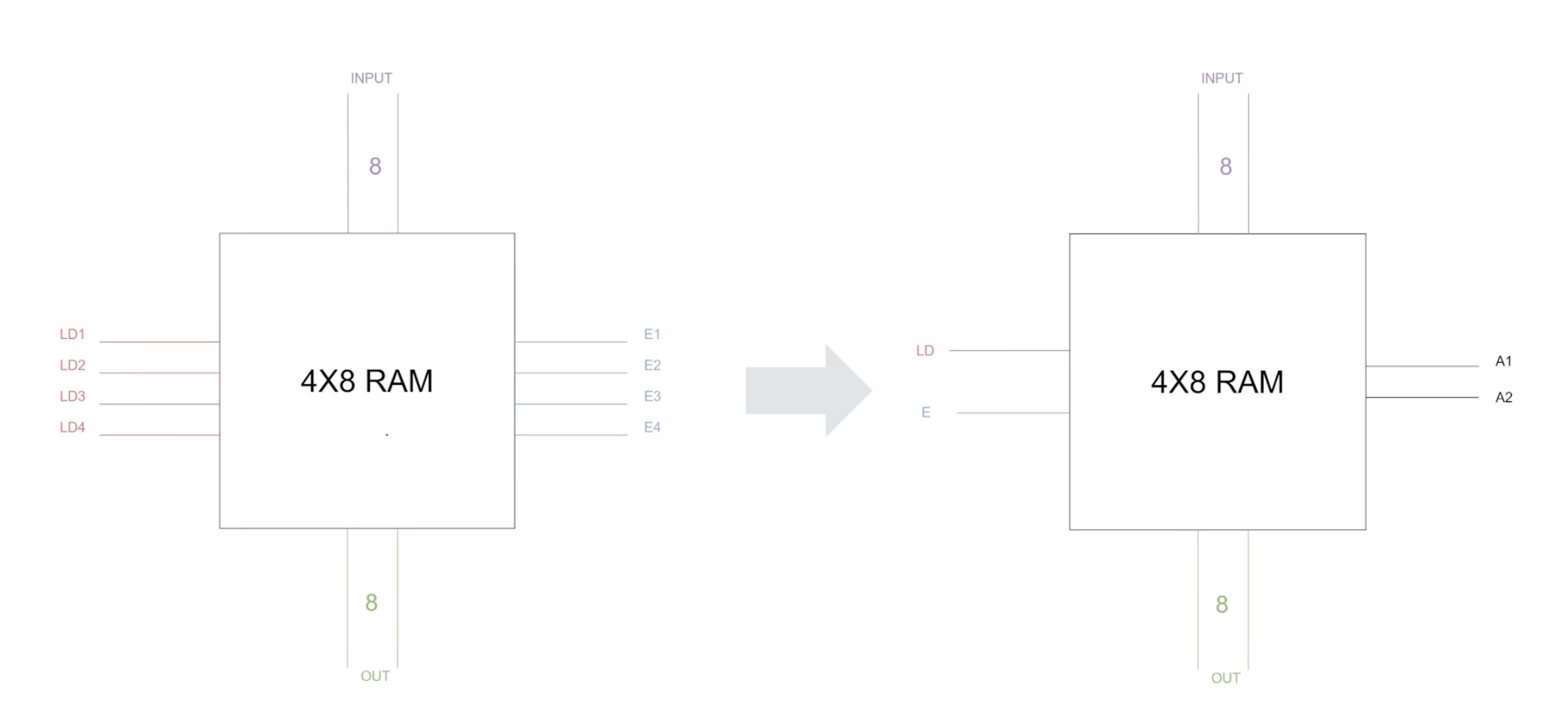

但由于需执行的8代码存在很多行,因此可以把多个寄存器串联在一起来实现

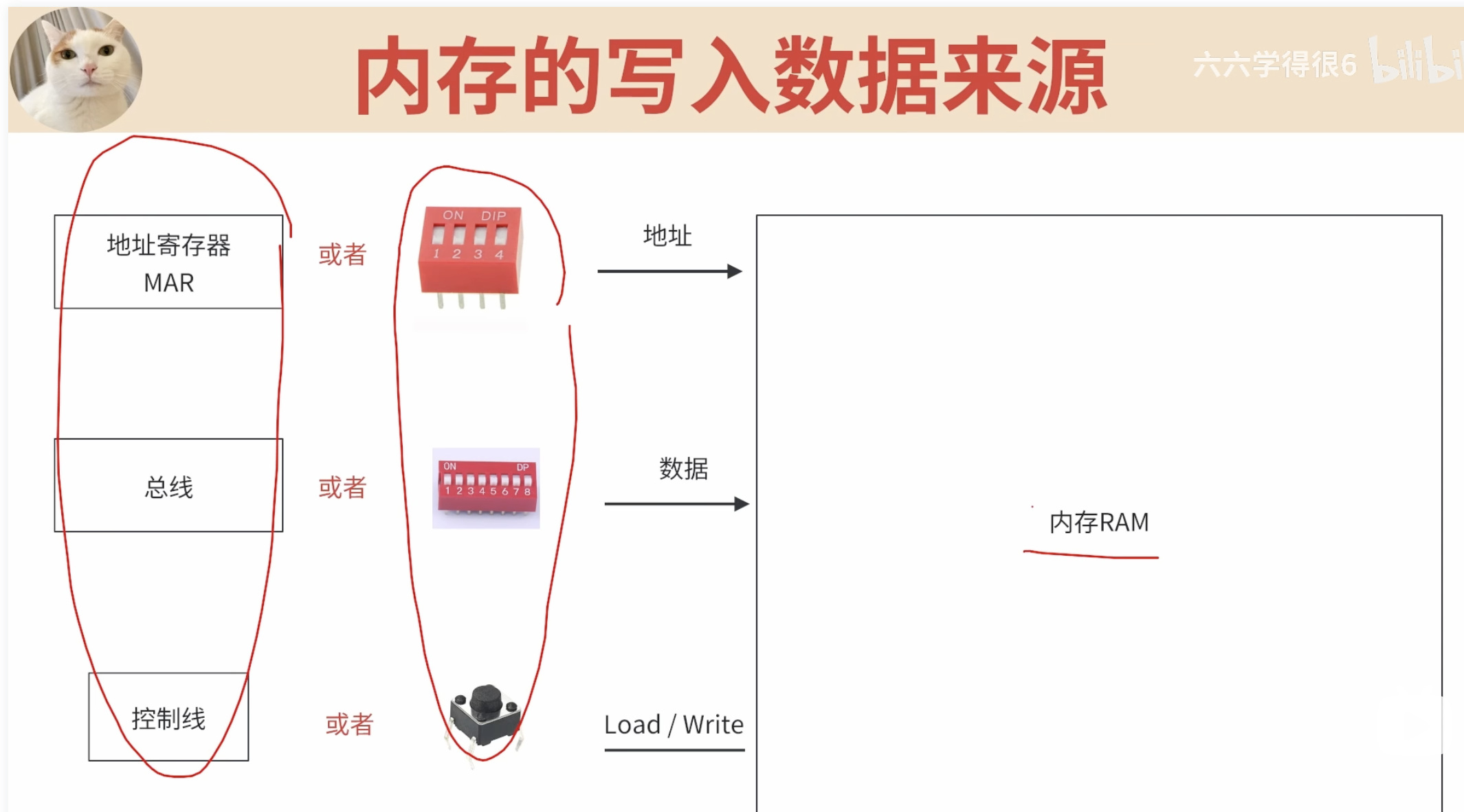

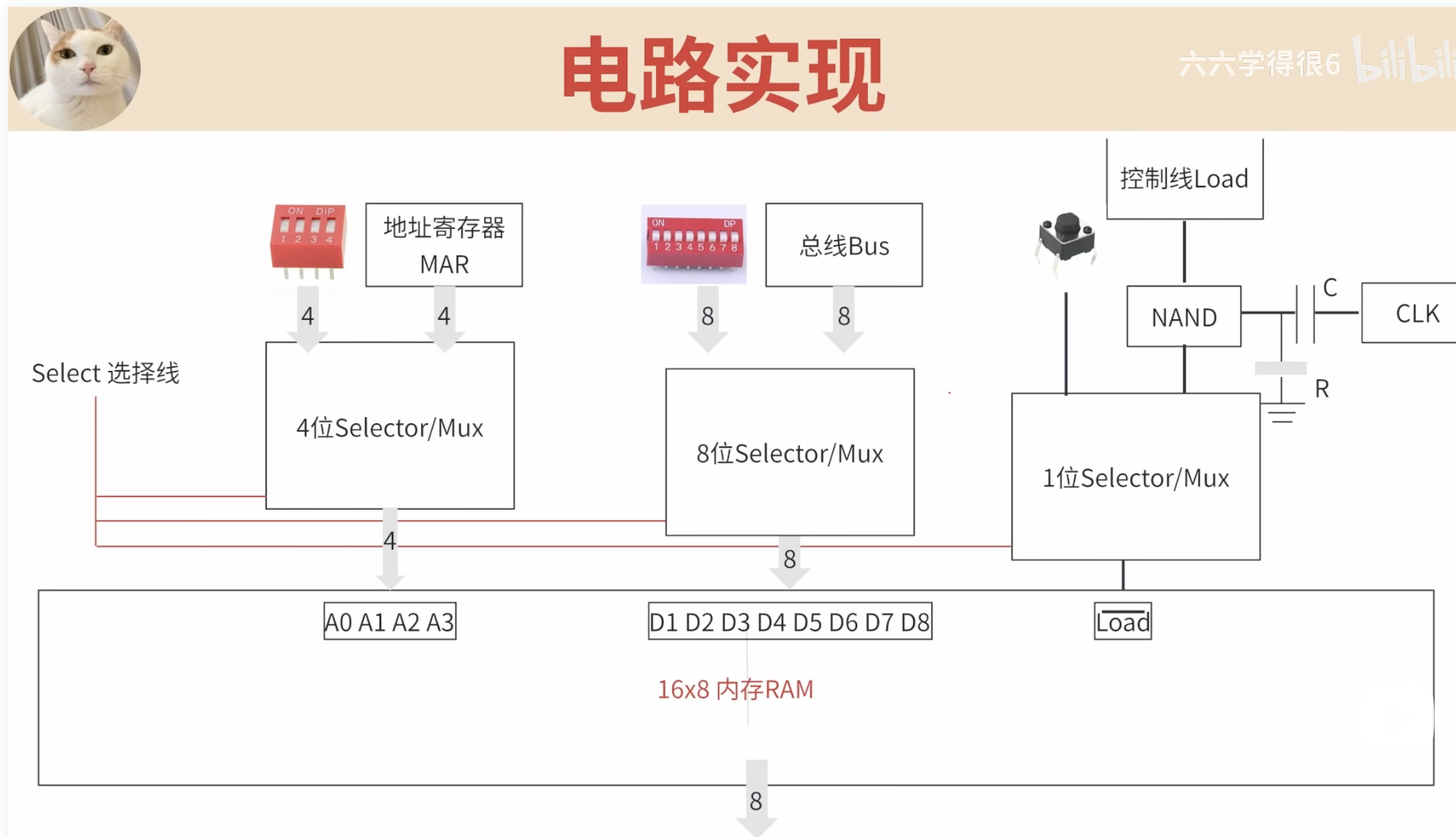

内存的数据来源

数据来源

地址寄存器:存储来自于哪里的数据地址

总线:从总线获取数据输入

控制线:控制加载数据还是写入数据

但怎样区分这不同的输入源呢

可以使用多路选择器控制采用哪里的输入数据

最后内存实现电路

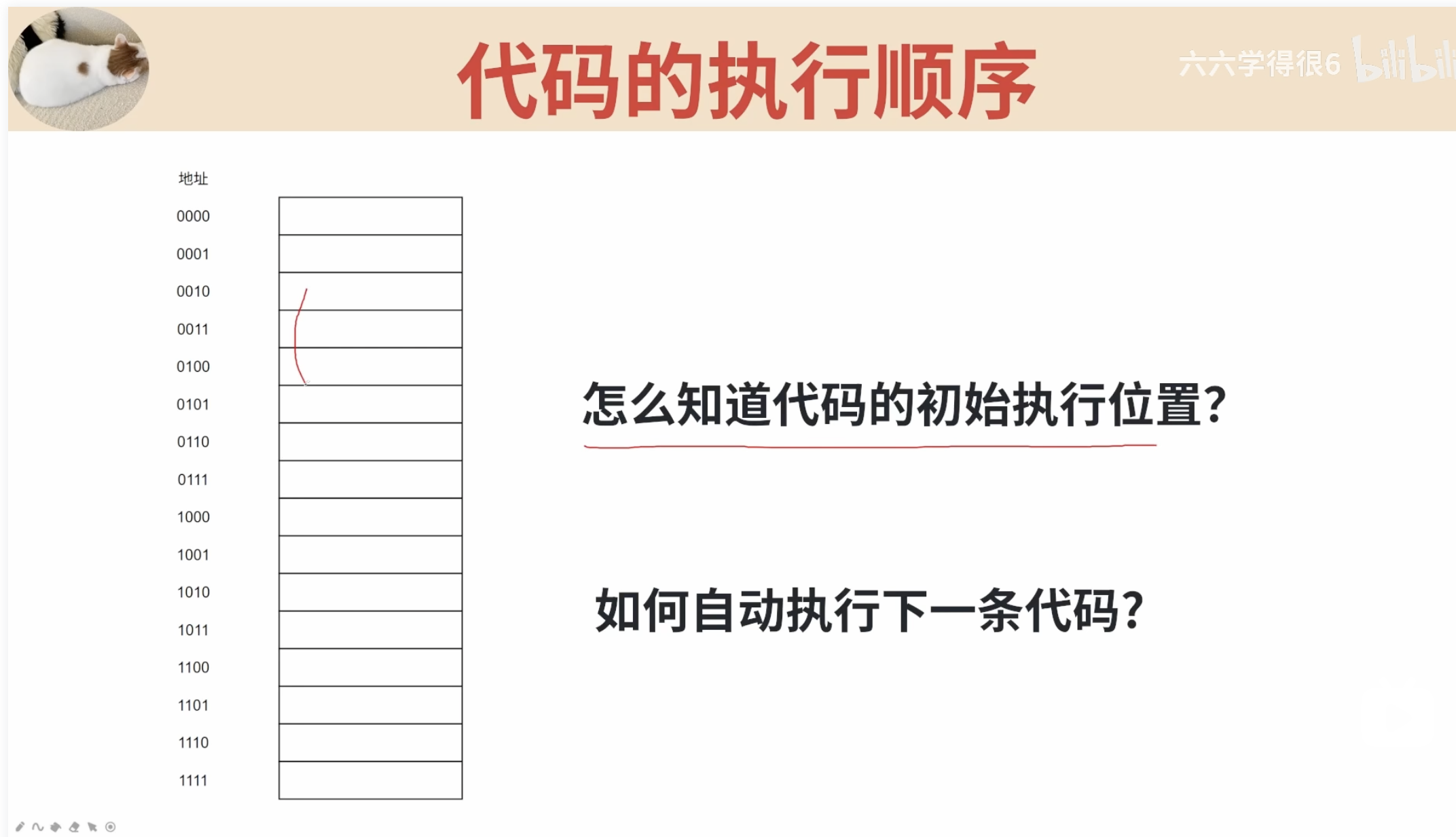

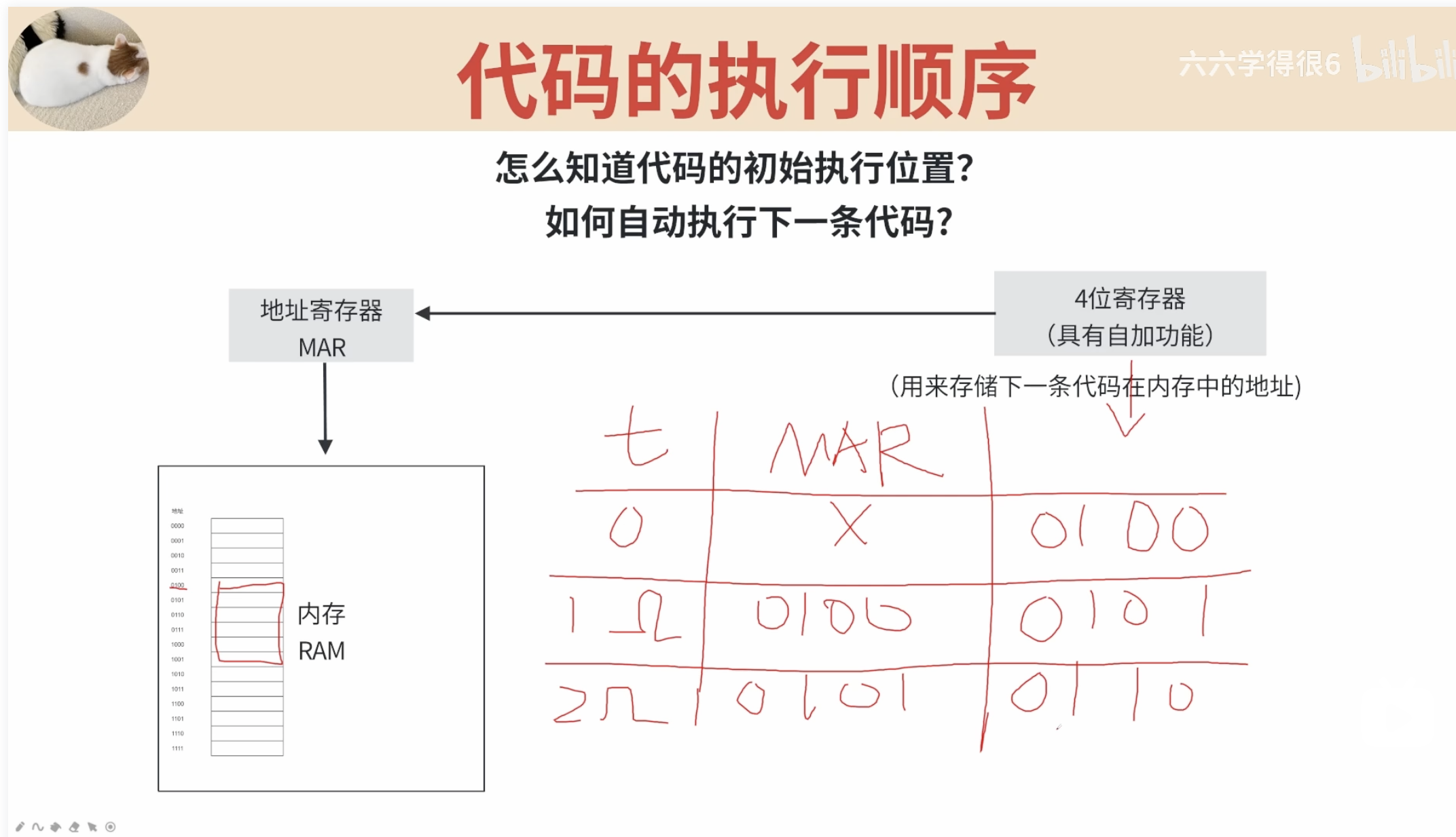

程序计数器 PC

计算机在执行逻辑的时候,执行完的当前数据怎样知道下一条呢

这个时候需要1个元器件:程序计数器,记录下一条执行逻辑的地址

可以存储位置以及能够自加一操作

完整计算机结构

参考:B站从零搭建计算机教程