LDPC码的编码算法

为了将LDPC 码在硬件上实现,需要考虑码的结构、编码的复杂度和编码的时延。

传统方法进行编码时,码长越长,编码复杂度和需要的时间越长,这非常不利于实际实现。所以将码构造和编码结合起来,构造符合一定规律的校验矩阵,再利用其直接进行编码是在工程实际应用中的最佳选择。

下面将介绍三种此类编码算法,它们拥有特殊校验矩阵形式如下三角或近似下三角,编码时的运算量也远小于传统的编码算法,而且易于在工程中使用。

1 基于高斯消去的编码

LDPC 码的校验矩阵是稀疏的,且行重和列重都很小。首先利用高斯消去法将矩阵转换成等效的下三角矩阵,接下来就可以利用转化后的矩阵直接进行编码。

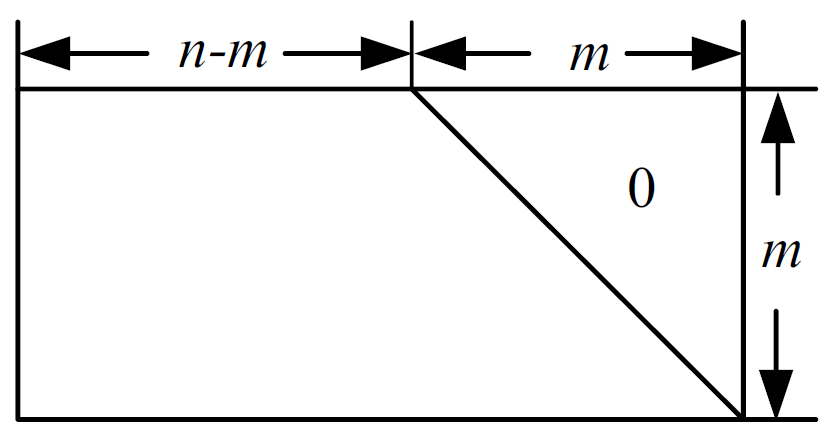

此时编码的运算量会增加,因为得到的转换后的矩阵不再具有稀疏性。经过数学方法处理后得到的具有特殊形式的矩阵即基于高斯消去法的校验矩阵如下图所示。

将 LDPC 码的码字设为c = (a,p),其检验矩阵为![]() ,则两者应该满足公式

,则两者应该满足公式![]() ,其中, p 表示校验位长度为m ,a 表示初始码元长度为n-m 。则基于高斯消去的编码算法可分为两步:

,其中, p 表示校验位长度为m ,a 表示初始码元长度为n-m 。则基于高斯消去的编码算法可分为两步:

第一步:将需要传输的初始码元直接赋值给a。

第二步:校验位![]() 的表达式如下所示:

的表达式如下所示:

![]()

2 基于近似下三角矩阵的编码

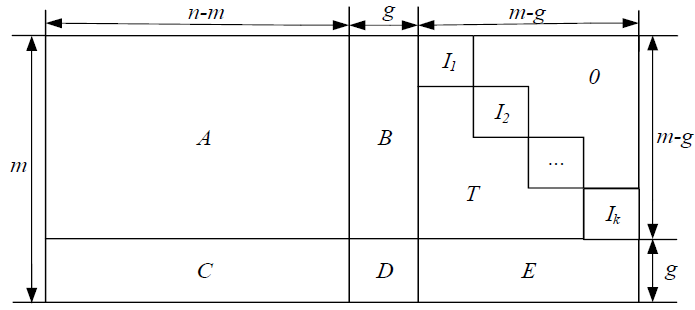

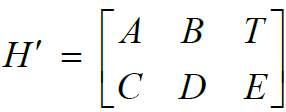

为了减小因为稀疏性变低引起的运算量的增加,只将矩阵H 的行和列进行变换,变成如下图所示的近似下三角的结构,虽然不像高斯消去法得到的下三角矩阵一样计算步骤简单且适用于所有LDPC 码,但是可以拥有更小的编码运算量。

变换后得到的近似下三角结构的校验矩阵可以分割成不同大小的6 个块矩阵,其中矩阵 D和矩阵 T 为方阵,大小分别为![]() 和

和![]() ,矩阵 T 对角上的元素全为“1”。于是可以将上述矩阵内的不同部分用不同的矩阵表示,则有下式的形式:

,矩阵 T 对角上的元素全为“1”。于是可以将上述矩阵内的不同部分用不同的矩阵表示,则有下式的形式:

通过公式推导,可以得到基于近似下三角矩阵的编码算法。首先将信息比特作为码字的第一部分输出,再通过矩阵运算公式计算出校验向量![]() 和

和![]() ,就得到了码字向量c 。

,就得到了码字向量c 。

3 基于IEEE 802.16e 标准LDPC 码的编码

在IEEE 802.16e 标准中提供了多种快速编码算法,这些算法的关键点都是利用了准双对角线结构和迭代的思想。这种结构的矩阵在编码时只需要进行加法、乘法和求逆矩阵的运算,使得编码的复杂度和硬件实现难度都大大降低了。最复杂的求逆运算可以在FPGA 实现时通过移位来实现且只有一次。