Xilinx FPGA MIPI DSI TX Subsystem 仿真笔记

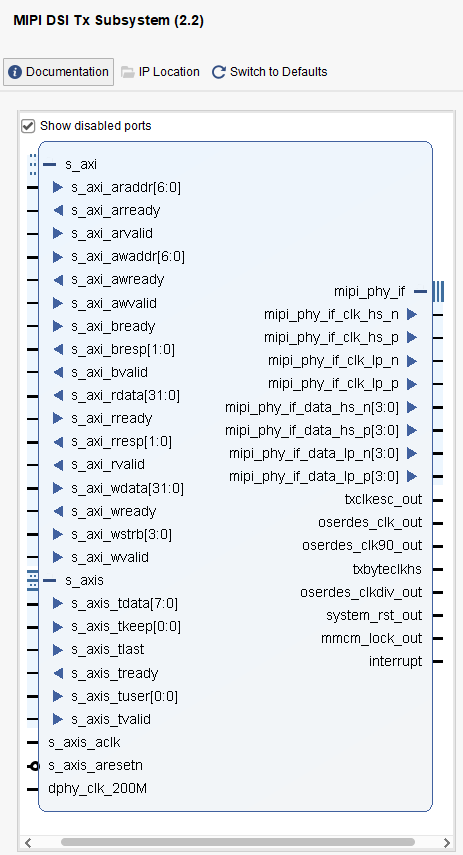

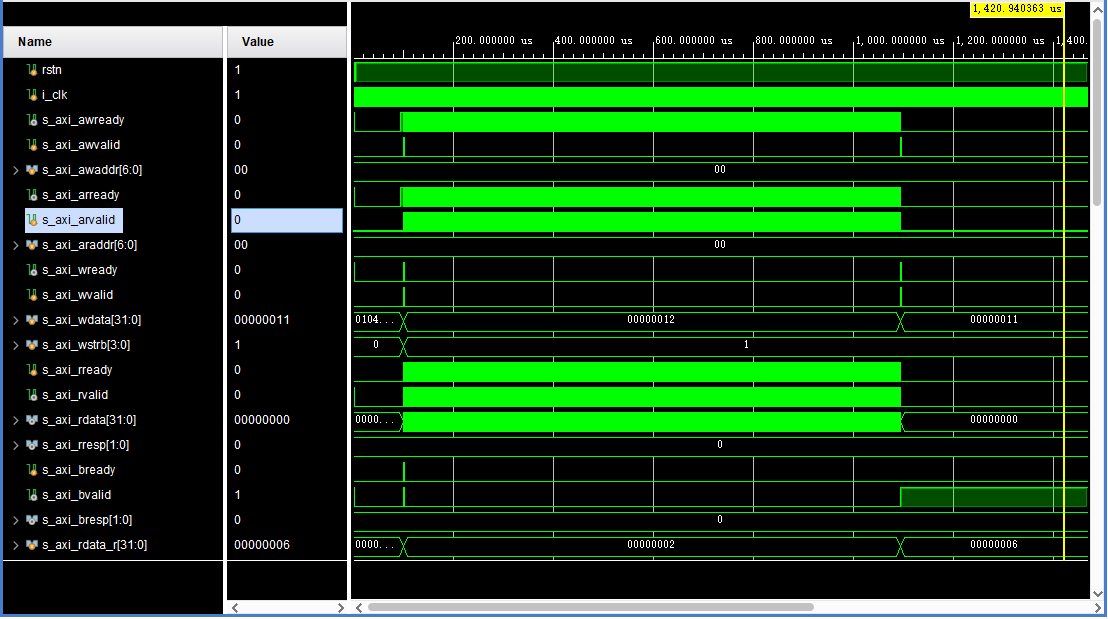

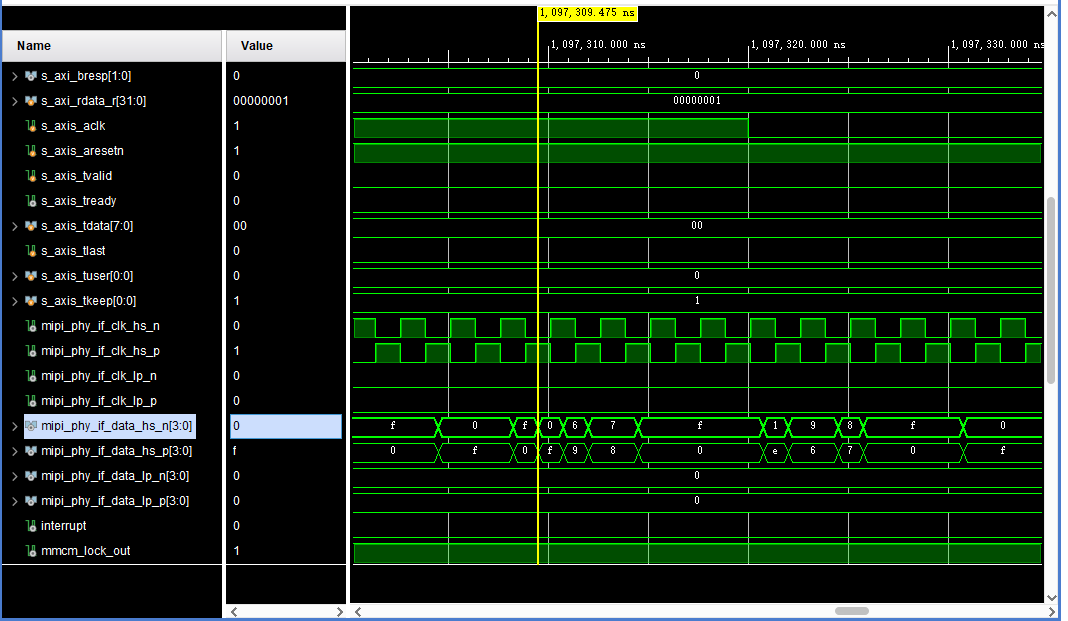

MIPI DSI TX Subsystem IP接口如图。

测试文件:

`timescale 1ns / 100ps

module Parallel2DSI_tb();

parameter periode_1 = 20;

parameter periode_2 = 20;

parameter periode_3 = 20;

parameter CLKT = 2;

reg rstn;

reg i_clk;

parameter C_M_AXI_ADDR_WIDTH = 7;

//s_axi

wire s_axi_awready ;

reg s_axi_awvalid ;

reg [C_M_AXI_ADDR_WIDTH-1:0] s_axi_awaddr ;

wire s_axi_arready ;

reg s_axi_arvalid ;

reg [C_M_AXI_ADDR_WIDTH-1:0] s_axi_araddr ;

wire s_axi_wready ;

reg s_axi_wvalid ;

reg [31:0] s_axi_wdata ;

reg [3:0] s_axi_wstrb ;

reg s_axi_rready ;

wire s_axi_rvalid ;

wire [31:0] s_axi_rdata ;

wire [1:0] s_axi_rresp ;

reg s_axi_bready ;

wire s_axi_bvalid ;

wire [1:0] s_axi_bresp ;

//s_axis

reg s_axis_aclk ;

reg s_axis_aresetn ;

// reg s_axis_tvalid ;

wire s_axis_tvalid ;

wire s_axis_tready ;

reg [7:0] s_axis_tdata ;

// reg s_axis_tlast ;

wire s_axis_tlast ;

// reg [95:0] s_axis_tuser ;

wire [0:0] s_axis_tuser ;

reg [0:0] s_axis_tkeep ;

reg [1:0] s_axis_tdest ;

wire mipi_phy_if_clk_hs_n;

wire mipi_phy_if_clk_hs_p;

wire mipi_phy_if_clk_lp_n;

wire mipi_phy_if_clk_lp_p;

wire [3 : 0] mipi_phy_if_data_hs_n;

wire [3 : 0] mipi_phy_if_data_hs_p;

wire [3 : 0] mipi_phy_if_data_lp_n;

wire [3 : 0] mipi_phy_if_data_lp_p;

wire interrupt;

wire s_axi_init_rdy;

initial begin

rstn = 1'b0;

s_axis_aresetn = 0;

s_axis_tdest = 0;

s_axis_aclk = 0;

s_axis_tdata = 0;

s_axis_tkeep = 1'b1;

//s_axi_bready = 1'b0;

#1600;

#1600 rstn = 1'b1;

#90000;

s_axis_aresetn = 1;

end

initial begin

s_axi_awaddr = 7'd0;

s_axi_araddr = 7'd0;

s_axi_awvalid = 1'b0;

s_axi_wvalid = 1'b0;

s_axi_arvalid = 1'b0;

s_axi_rready = 1'b0;

s_axi_bready = 1'b0;

s_axi_wdata = 32'h0104_15bc;

s_axi_wstrb = 4'b1001;

#99000;

s_axi_awaddr = 7'd0;

s_axi_araddr = 7'd0;

s_axi_awvalid = 1'b1;

s_axi_wvalid = 1'b1;

s_axi_arvalid = 1'b1;

s_axi_rready = 1'b1;

s_axi_bready = 1'b1;

s_axi_wdata = 32'h0104_15bc;

s_axi_wstrb = 4'b1001;

wait(s_axi_awready == 1'b1) #(20 * 1) s_axi_awvalid = 1'b0;

end

initial begin

i_clk = 1'b0;

end

always i_clk = #periode_1 ~i_clk;

always #20 s_axis_aclk = ~s_axis_aclk;

//assign s_axis_aresetn = locked;

reg [10:0] cnt_h = 0;

reg [10:0] cnt_v = 0;

// 128*32

always @(posedge s_axis_aclk)

if(s_axis_aresetn && s_axi_init_rdy==1 )

begin

if(s_axis_tready)

if(cnt_h==200)

cnt_h <= 40;

else

cnt_h <= cnt_h + 1;

if(cnt_h==200)

if(cnt_v >= 31)

cnt_v <= 0;

else

cnt_v <= cnt_v + 1;

end

//----------------------------------------------------------------------------------

// assign s_axis_tvalid = 0;

assign s_axis_tvalid = (cnt_h >= 73) ? 1:0;

assign s_axis_tuser[0] = (cnt_v==0 && cnt_h==73)? 1 : 0 ;

assign s_axis_tlast = (cnt_h==200)? 1 : 0 ;

// s_axis_tuser[0] = 0; //Frame start

always @(posedge s_axis_aclk)

if(s_axis_tvalid && s_axis_tready) begin

s_axis_tdata[7:0] <= s_axis_tdata[7:0] + 1;

end

clk_wiz_0 clk_wiz_0inst

(

.clk_in1 (i_clk)

,.resetn (rstn)

,.clk_out1 (dphy_clk_200M)

,.clk_out2 (txclkesc_in)

,.clk_out3 (oserdes_clk_in)

,.clk_out4 (oserdes_clk90_in)

,.clk_out5 (txbyteclkhs_in)

,.locked (locked)

);

mipi_dsi_tx_subsystem_0 tx_inst

(

.s_axis_aclk (s_axis_aclk)

,.s_axis_aresetn (s_axis_aresetn)

,.dphy_clk_200M (dphy_clk_200M)

,.txclkesc_out (txclkesc_out)

,.oserdes_clk_out (oserdes_clk_out)

,.txbyteclkhs (txbyteclkhs)

,.oserdes_clkdiv_out (oserdes_clkdiv_out)

,.system_rst_out (system_rst_out)

,.mmcm_lock_out (mmcm_lock_out)

,.interrupt (interrupt)

,.s_axi_araddr (s_axi_araddr)

,.s_axi_arready (s_axi_arready)

,.s_axi_arvalid (s_axi_arvalid)

,.s_axi_awaddr (s_axi_awaddr)

,.s_axi_awready (s_axi_awready)

,.s_axi_awvalid (s_axi_awvalid)

,.s_axi_bready (s_axi_bready)

,.s_axi_bresp (s_axi_bresp)

,.s_axi_bvalid (s_axi_bvalid)

,.s_axi_rdata (s_axi_rdata)

,.s_axi_rready (s_axi_rready)

,.s_axi_rresp (s_axi_rresp)

,.s_axi_rvalid (s_axi_rvalid)

,.s_axi_wdata (s_axi_wdata)

,.s_axi_wready (s_axi_wready)

,.s_axi_wstrb (s_axi_wstrb)

,.s_axi_wvalid (s_axi_wvalid)

,.s_axis_tdata (s_axis_tdata)

,.s_axis_tlast (s_axis_tlast)

,.s_axis_tready (s_axis_tready)

,.s_axis_tuser (s_axis_tuser)

,.s_axis_tvalid (s_axis_tvalid)

,.mipi_phy_if_clk_hs_n (mipi_phy_if_clk_hs_n)

,.mipi_phy_if_clk_hs_p (mipi_phy_if_clk_hs_p)

,.mipi_phy_if_clk_lp_n (mipi_phy_if_clk_lp_n)

,.mipi_phy_if_clk_lp_p (mipi_phy_if_clk_lp_p)

,.mipi_phy_if_data_hs_n (mipi_phy_if_data_hs_n)

,.mipi_phy_if_data_hs_p (mipi_phy_if_data_hs_p)

,.mipi_phy_if_data_lp_n (mipi_phy_if_data_lp_n)

,.mipi_phy_if_data_lp_p (mipi_phy_if_data_lp_p)

);

endmodule

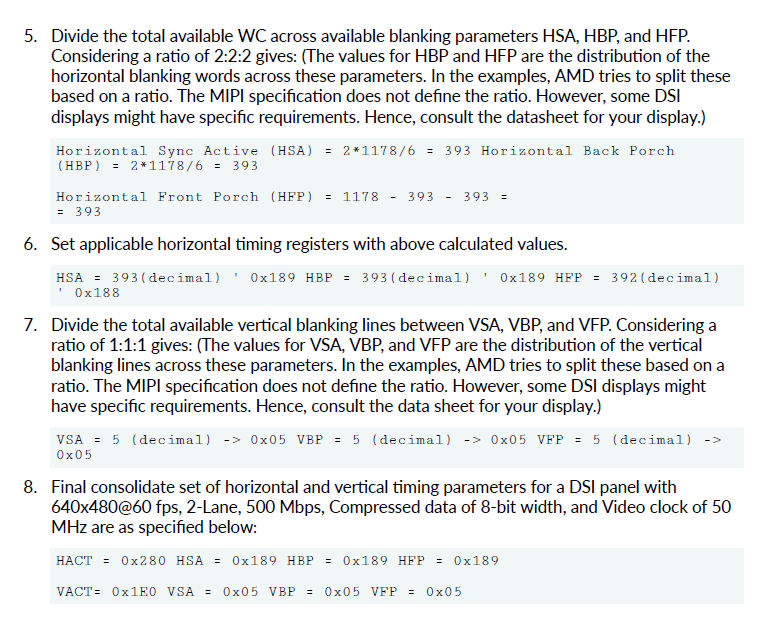

启动仿真后,发现MIPI并没有信号发出来。

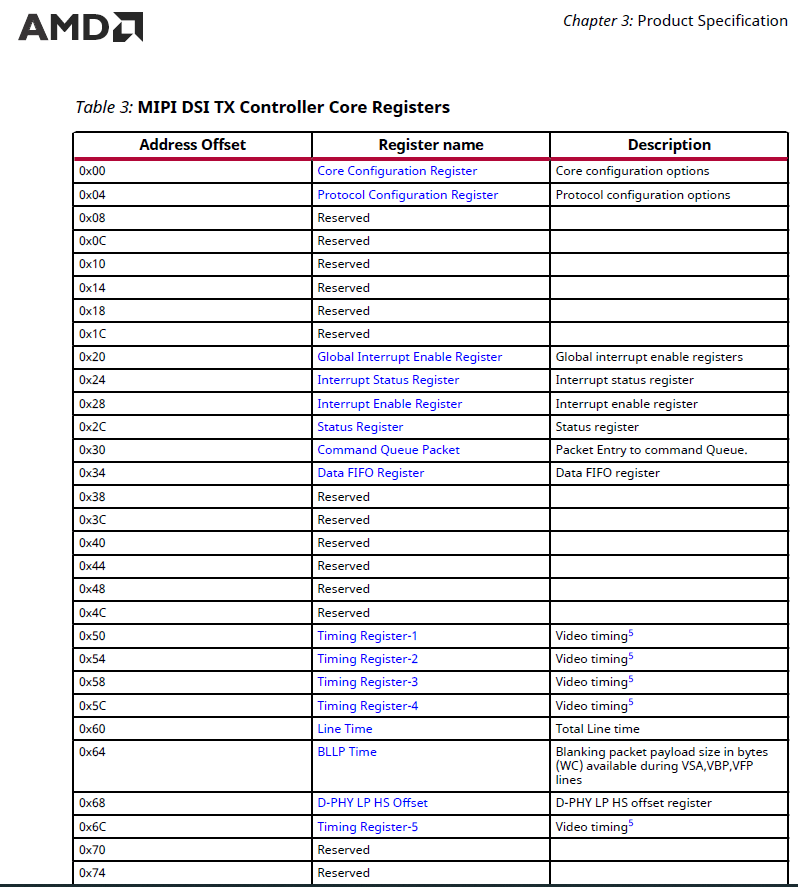

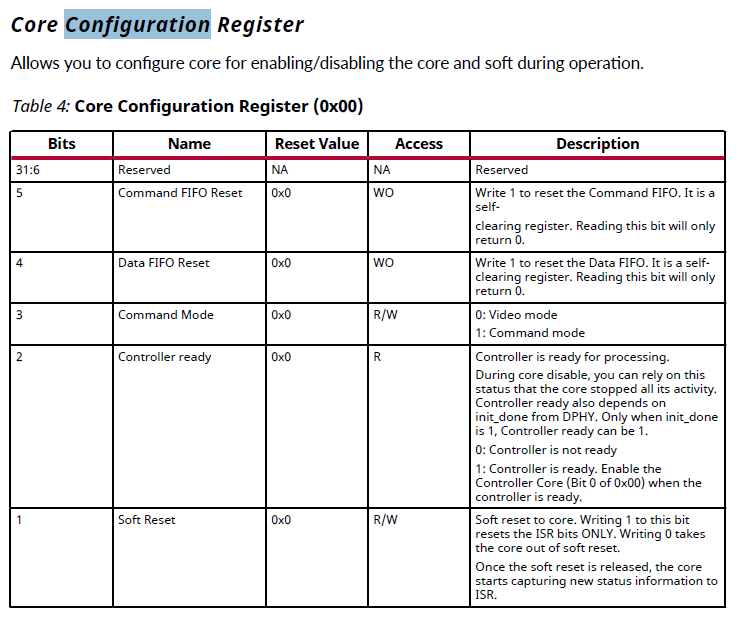

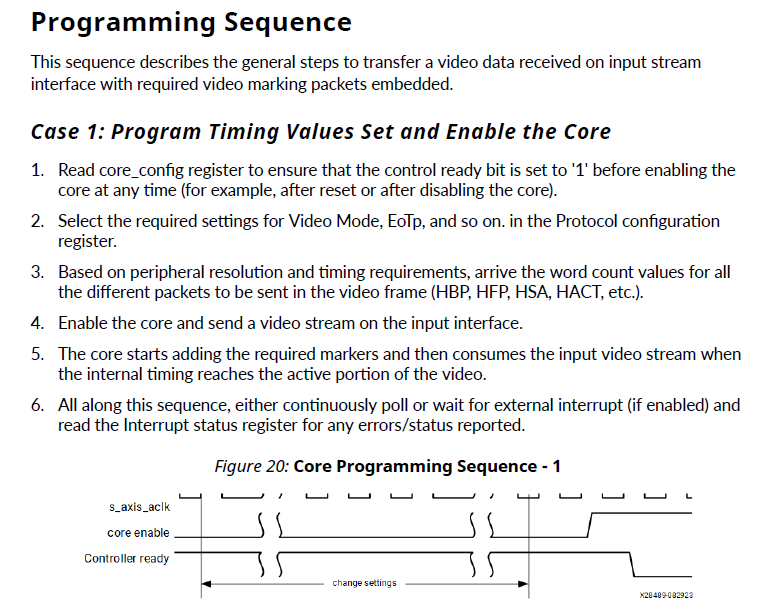

查看指导,需要先对MIPI DSI TX Controller Core Registers进行初始化。

初始化后,读寄存器查看Controller ready是否OK。OK后才可以继续操作。

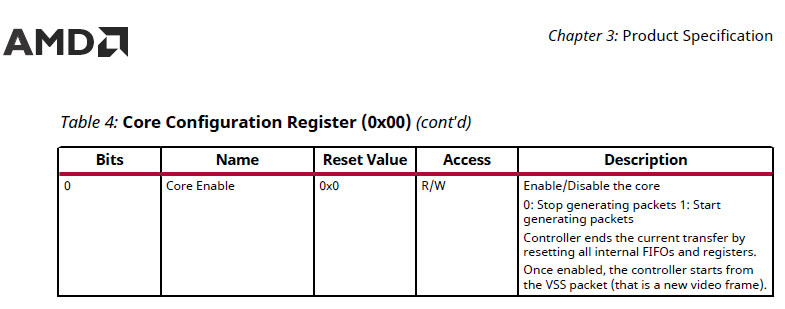

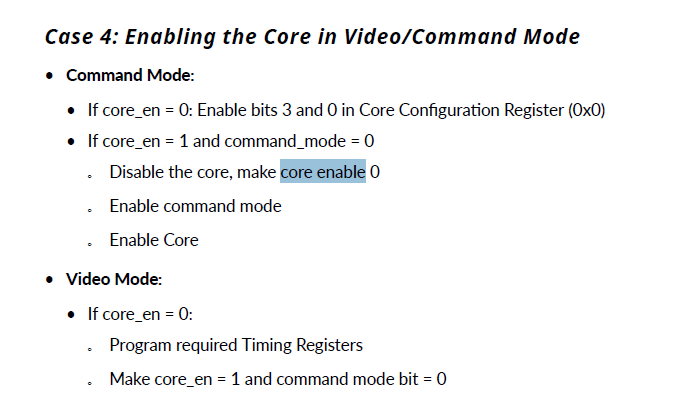

初始化步骤:软件复位Soft Reset,等待Soft Reset释放后Controller readyOK,初始化参数和模式等,最后启动Core Enable,发送视频流。

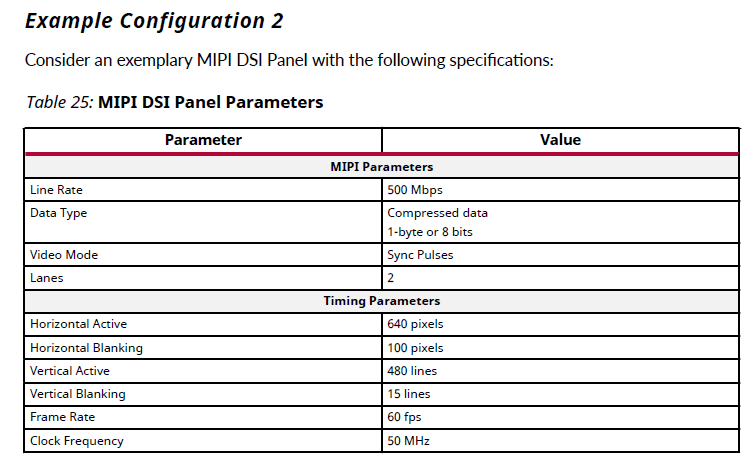

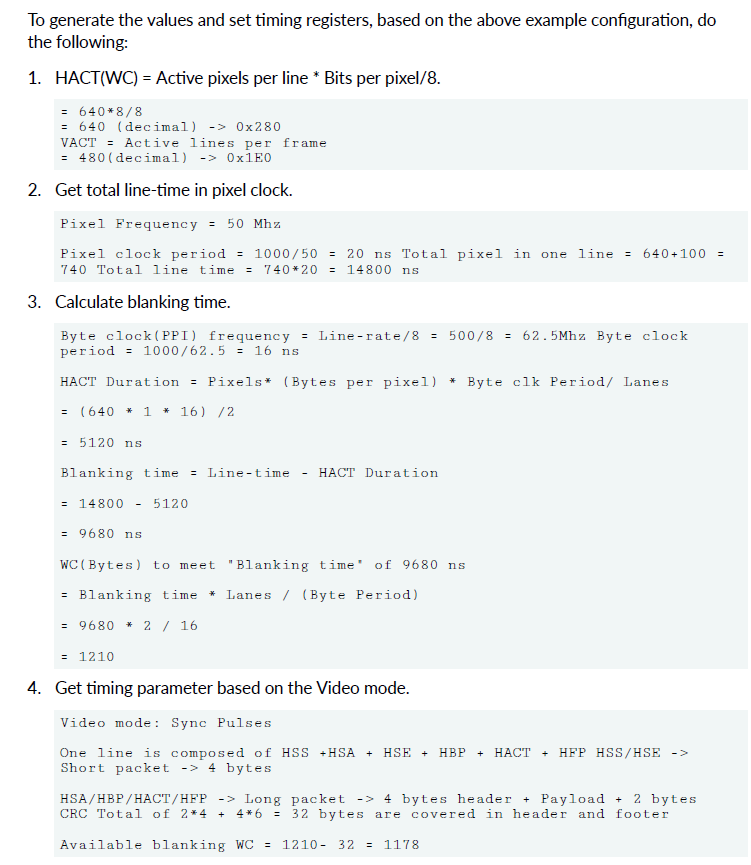

配置例子:

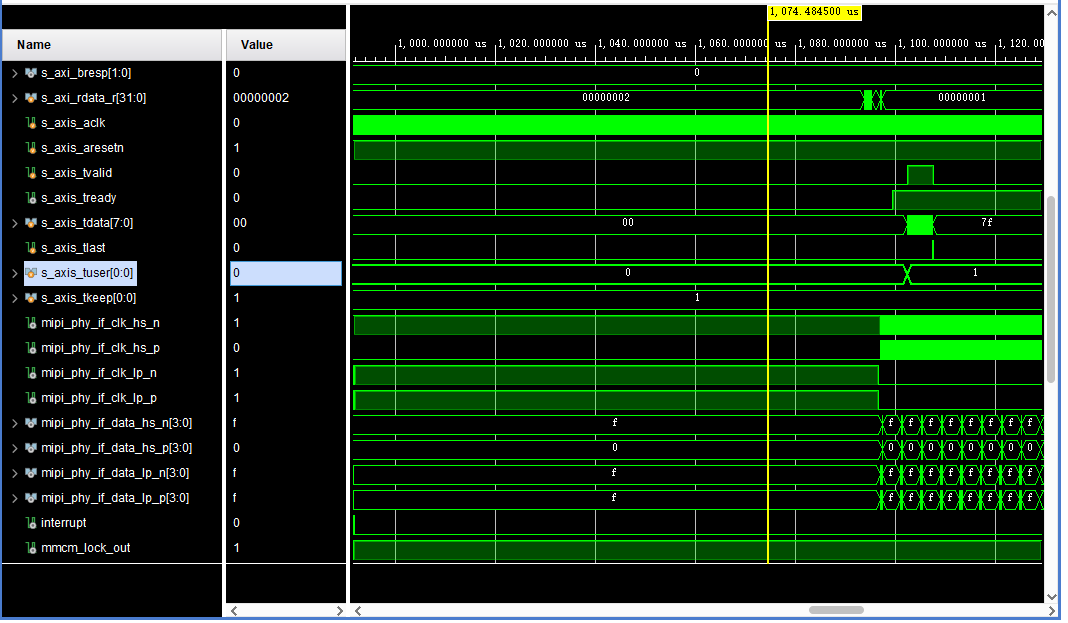

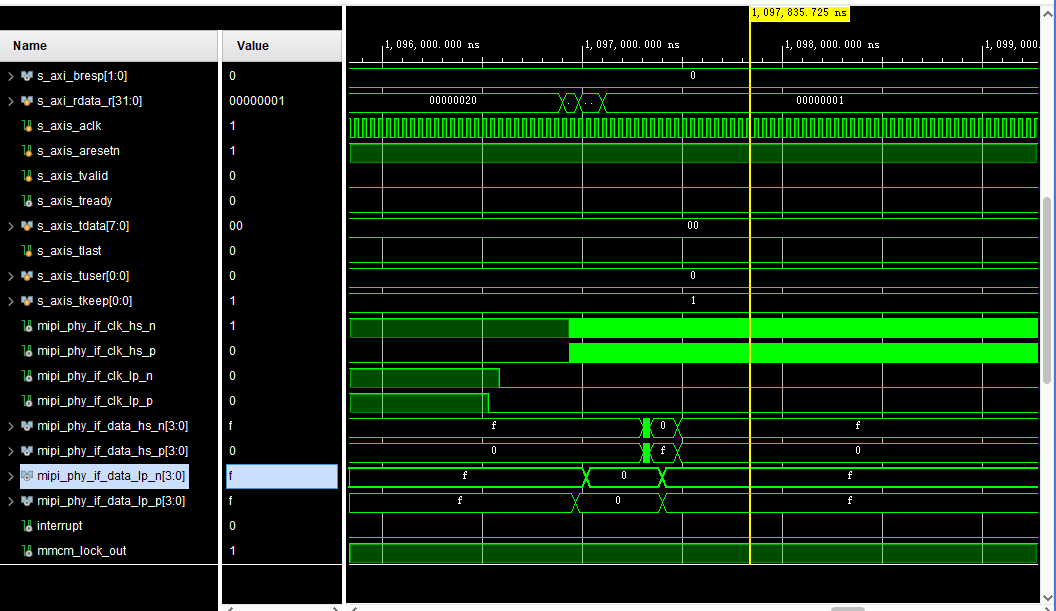

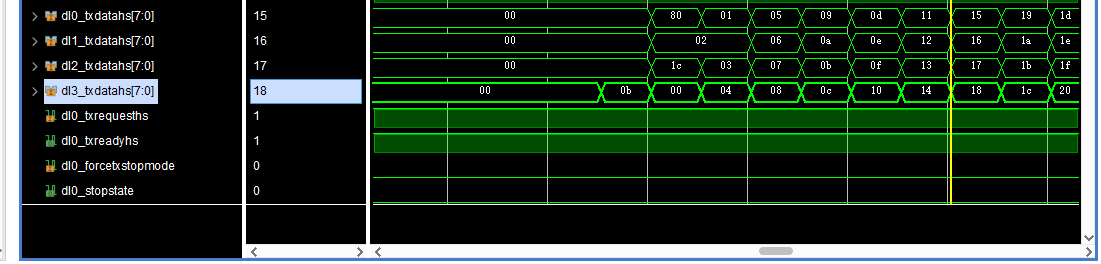

按照上面配置后,发送视频流。MIPI接口正常发出MIPI波形。MIPI DSI TX Subsystem可以正常工作。

MIPI PHY

欢迎讨论交流。

微:moning_hello