高速ADC数据格式与JESD204B IP数据格式映射关系

本文参考硕士论文:基于FPGA架构的高速信号传输系统的设计与实现-孙昌达

- ADC端数据输出格式:data format

- FPGA端数据接收格式:data format

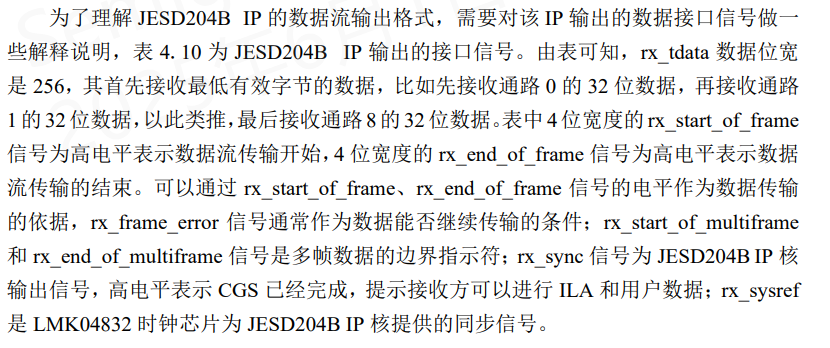

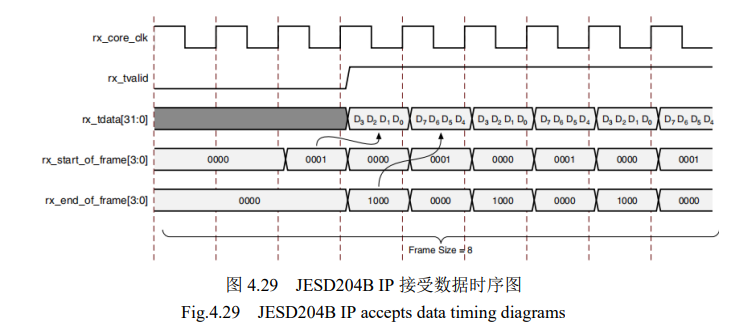

Note:JESD204B IP先入数据存放在低字节,后入数据存放在高字节。

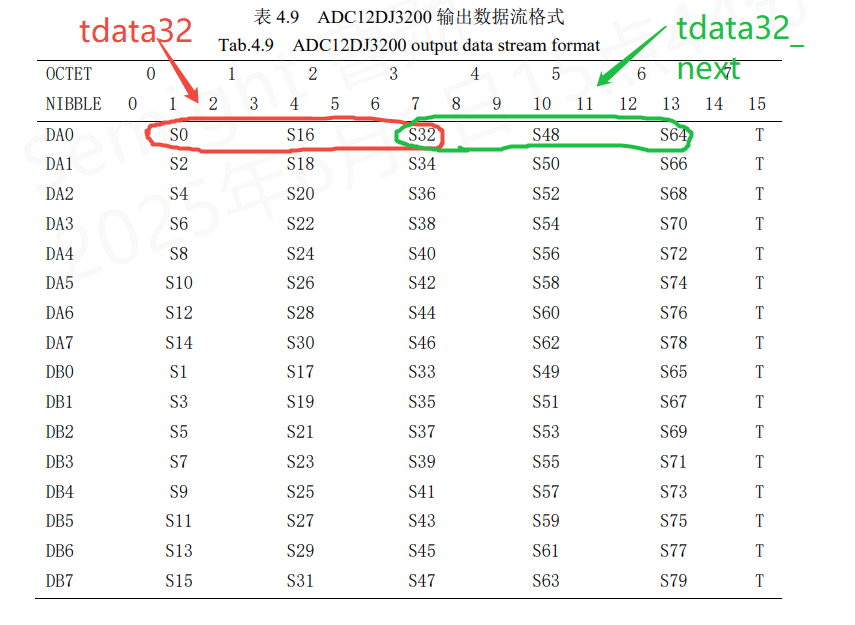

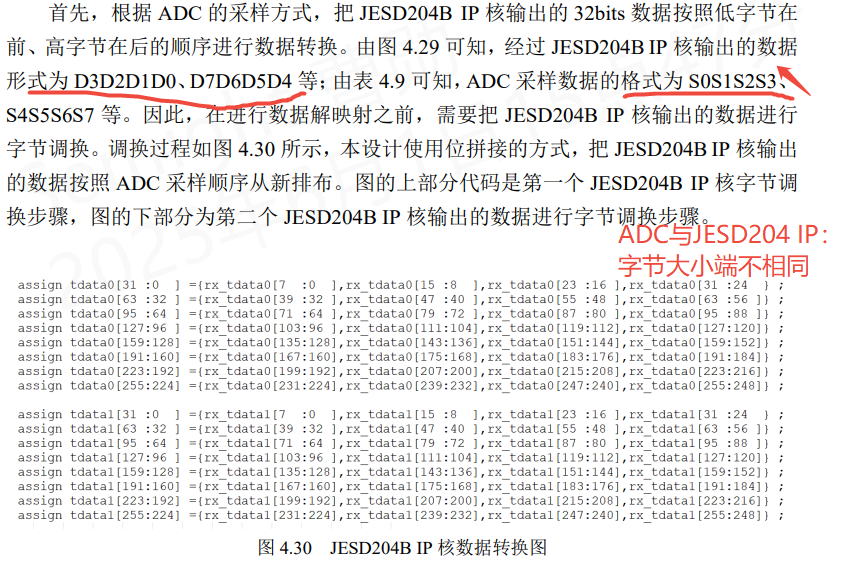

参考表4.9 OCTET这一行可知, ADC Sn采样数据均采用高字节数据在前,低字节数据在后,这样的顺序输出。因此,JESD204B IP接收的数据格式,字节顺序与ADC的字节顺序正好相反,故需要进行字节顺序调换。

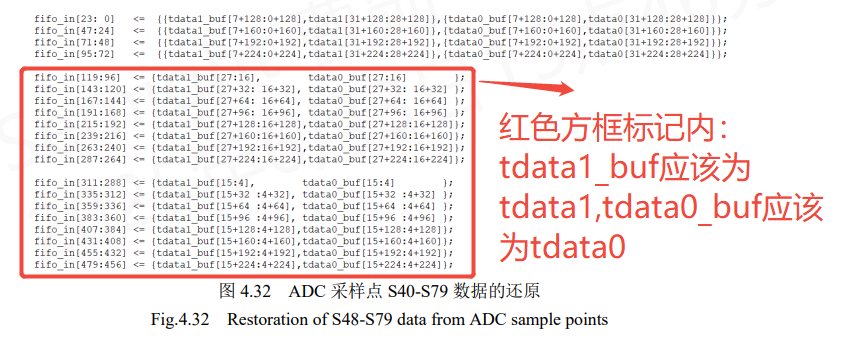

- note:按照我的理解,上图中,tdata1_buf应该是tdata1的上一个32位数据点,tdata1应该是tdata1_buf的下一个32位数据点。类似于reg_buf是reg打一拍。

- 总结:ADC与FPGA数据映射规律

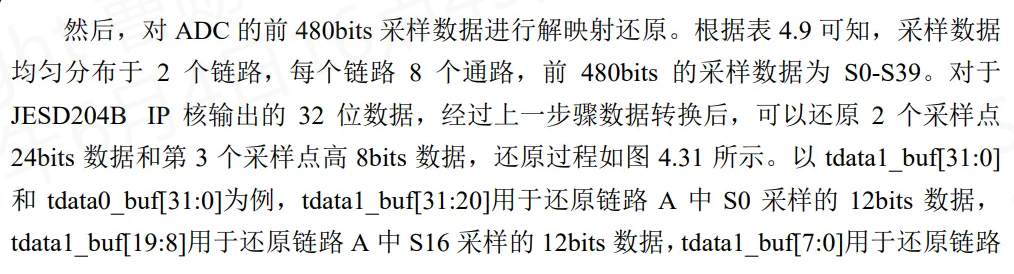

- 由表4.9可知,ADC12DJ3200整个采样周期的采样点数是80个,S0 ~ S79。有效数据比特为960bit,无效数据比特为64。 总的数据位宽为1024比特。

- FPGA的rx_data位宽为32比特,每个IP有8个Lane,所以对应的数据位宽为256比特。假设上述FPGA仅例化一个JESD204B IP。那么,ADC12DJ3200整个采样周期的采样点数,需要4个256比特数据点,对应FPGA IP输出的前后依次的4个数据点。

- 上述工程中,FPGA例化2个JESD204B IP。所以需要分别映射。两个JESD204B IP的tdata1_buf和tdata1名字相同,但不是同一个信号。