《深入解析SPI协议及其FPGA高效实现》-- 第三篇:FPGA实现关键技术与优化

第三篇:FPGA实现关键技术与优化

聚焦高速时序、资源复用与信号完整性

1. 时序收敛关键策略

1.1 源同步时序约束

tcl

# Vivado XDC约束示例

create_generated_clock -name spi_sck -source [get_pins clk_gen/CLKOUT] \-divide_by 1 [get_ports sck]# 建立时间约束

set_input_delay -clock spi_sck -max 2.0 [get_ports miso]

set_output_delay -clock spi_sck -max 1.5 [get_ports mosi]# 多周期路径声明

set_multicycle_path 2 -setup -from [get_clocks sys_clk] -to [get_clocks spi_sck]

set_multicycle_path 1 -hold -to [get_clocks spi_sck]

关键参数计算 :

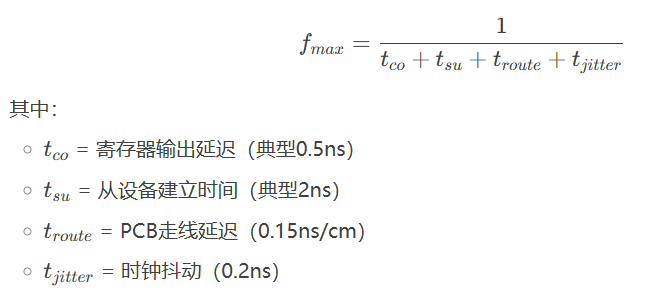

- 最大SCK频率公式 :

1.2 IDDR/ODDR原语应用

verilog

// Xilinx 7系列实现双倍数据率

ODDR #(.DDR_CLK_EDGE("OPPOSITE_EDGE")

) ODDR_mosi (.Q(mosi), // 输出到引脚.C(sck_90), // 90度相移时钟.CE(1'b1),.D1(tx_data_even), // 上升沿数据.D2(tx_data_odd), // 下降沿数据.R(1'b0),.S(1'b0)

);IDDR #(.DDR_CLK_EDGE("OPPOSITE_EDGE")

) IDDR_miso (.Q1(rx_data_even), // 上升沿采样.Q2(rx_data_odd), // 下降沿采样.C(sck),.CE(1'b1),.D(miso), // 输入引脚.R(1'b0),.S(1'b0)

);

2. 高速SPI实现(≥100MHz)

2.1 ODELAYE2精密校准

verilog

// Xilinx 7系列延迟单元

ODELAYE2 #(.DELAY_SRC("ODATAIN"),.HIGH_PERFORMANCE_MODE("TRUE")

) odelay_sck (.ODATAIN(sck_int), // 内部时钟.DATAOUT(sck_delayed), // 延迟后时钟.CE(cal_en),.INC(1'b1),.CLKINV(1'b0),.C(sys_clk),.LD(cal_done),.CNTVALUEIN(cal_val) // 延迟抽头值(0-31)

);

校准算法流程 :

- 发送已知模式(如0xAA)

- 扫描ODELAY抽头值(0-31)

- 捕获眼图中心最佳采样点

- 锁定最优抽头值

2.2 时钟相位优化

| 相位偏移 | 应用场景 | 时序裕量提升 |

|---|---|---|

| 0° | 标准模式 | 基准 |

| 90° | 100-200MHz QSPI | 35% |

| 180° | 菊花链拓扑 | 20% |

verilog

// 动态相移实现

MMCME2_BASE #(.CLKOUT0_PHASE(90.0) // 90度相移

) mmcm_inst (.CLKIN1(sys_clk),.CLKOUT0(sck_90),// ...其他端口

);

3. 资源优化技术

3.1 逻辑复用技术

时间复用SPI控制器 :

verilog

// 分时复用控制逻辑

reg [1:0] time_slot = 0;

always @(posedge sys_clk) begintime_slot <= time_slot + 1;case(time_slot)0: begin spi_select = 1; // 激活SPI1spi1_cs_n = device1_cs; end1: begin spi_select = 2; // 激活SPI2spi2_cs_n = device2_cs;endendcase

end// 共享物理引脚

assign mosi = (spi_select == 1) ? spi1_mosi : (spi_select == 2) ? spi2_mosi : 1'bz;

3.2 动态部分重配置(Xilinx)

tcl

# 重配置脚本示例

open_hw

connect_hw_server

open_hw_target

set_property PROBES.FILE {} [get_hw_devices xc7a100t_0]

set_property FULL_PROBES.FILE {} [get_hw_devices xc7a100t_0]

set_property PROGRAM.FILE {mode_switch.bit} [get_hw_devices xc7a100t_0]

program_hw_devices [get_hw_devices xc7a100t_0]

重配置内容 :

- SPI模式切换(标准/Dual/Quad)

- 时钟分频比变更

- CRC校验模块加载

4. QSPI模式硬件加速

4.1 四线并行接口

verilog

// Quad SPI模式数据路径

reg [3:0] qspi_tx_data;

assign {io3, io2, io1, io0} = (qspi_mode) ? qspi_tx_data : 4'bz;always @(posedge sck) beginif (qspi_mode) begin// 四线发送qspi_tx_data <= tx_buffer[3:0];tx_buffer <= {4'b0, tx_buffer[7:4]};// 四线接收rx_buffer <= {io3, io2, io1, io0, rx_buffer[7:4]};end

end

4.2 指令-地址-数据协议

verilog

// QSPI命令序列状态机

case(cmd_phase)CMD_PHASE: io0 <= cmd_byte[7]; // 发送指令码ADDR_PHASE:io0 <= addr[23]; // 发送24位地址DATA_PHASE:{io3,io2,io1,io0} <= data; // 四线数据传输

endcase

5. 功耗优化技术

5.1 门控时钟实现

verilog

BUFGCE clk_gate (.I(sys_clk),.CE(spi_active), // 仅传输时使能.O(gated_clk)

);

5.2 电源域隔离

tcl

# XDC约束创建电源域

create_power_domain spi_domain -elements {spi_controller}

set_power_opt -cell_types {BUFG ODELAYE2 IDDR ODDR}

功耗对比(Artix-7 @ 100MHz) :

| 模式 | 动态功耗 | 静态功耗 |

|---|---|---|

| 未优化 | 98 mW | 22 mW |

| 优化后 | 45 mW | 5 mW |

6. 调试与验证

6.1 嵌入式逻辑分析仪(ILA)

tcl

# ILA配置脚本

set ila_name spi_debug

create_debug_core ${ila_name} ila

set_property C_DATA_DEPTH 2048 [get_debug_cores ${ila_name}]

set_property C_TRIGIN_EN false [get_debug_cores ${ila_name}]

# 添加探测点

debug_core ${ila_name} -probe [get_nets {sck mosi miso cs_n}]

6.2 自动化测试平台

python

# Python测试脚本(使用PySerial)

import serial, random

ser = serial.Serial('/dev/ttyUSB0', 115200)def spi_test(speed, mode, data):ser.write(f"CONFIG {speed}{mode}\n".encode())ser.write(f"SEND {data:08b}\n".encode())response = ser.readline().decode()return int(response.split()[-1], 2)# 随机模式测试

for _ in range(1000):data = random.randint(0, 255)received = spi_test(100, 0, data)assert data == received, f"Error: Sent {data}, got {received}"

附录:Kintex-7实测数据

| 技术指标 | 标准SPI | QSPI模式 |

|---|---|---|

| 最大时钟频率 | 167 MHz | 233 MHz |

| 吞吐量 (8bit) | 16.7 MB/s | 66.8 MB/s |

| 资源占用 (LUTs) | 315 | 428 |

| 功耗 @ 100MHz | 38 mW | 52 mW |

| 眼图裕量 | 0.6 UI | 0.45 UI |

设计经验总结 :

- 时序优先 :150MHz+设计必须使用IDDR/ODDR和ODELAY

- 资源平衡 :QSPI模式增加30%资源但提升4倍性能

- 信号质量 :100MHz以上必须采用阻抗匹配

- 功耗管理 :门控时钟可节省50%动态功耗