DDR5 ECC详细原理介绍与基于协议讲解

本文篇幅较长,涉及背景原理介绍方便大家理解其运作方式 以及 基于DDR5协议具体展开介绍。

背景原理介绍

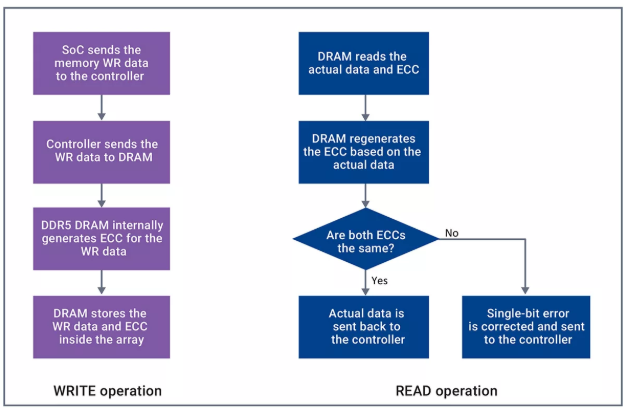

上图参考:DDR 内存中的 ECC

写入操作时,On-die ECC的工作过程如下:

- SoC将需要写入到Memory中的数据发送给控制器

- 控制器将需要写入的数据直接发送给DRAM芯片

- 在DDR5 DRAM内部,根据写入的数据进行计算,生成对应的ECC码

- DRAM芯片将写入的数据和对应的ECC码保存在存储阵列中

读取操作基本上是写入过程的逆过程,On-die ECC的具体工作过程如下:

- DRAM芯片将数据和对应的ECC码读取出来

- DRAM根据读取出的数据进行计算,生成用于校验的ECC码

- DRAM将读取出的ECC码和上一步中计算生成的ECC码进行比较

- 若这两个ECC码相同,则表明读取出的数据没有发生错误,数据将直接传输给控制器;若这两个ECC码不同,则表明读取出的数据存在错误,将会对数据以单bit纠错的方式进行数据纠正

综上,On-die ECC的基本特征是ECC码的计算生成和比较都在DRAM芯片上进行。On-die ECC其实是一种较新应用在DRAM中的技术,随着DRAM芯片的不断微缩,到了DDR5技术代,BL和WL的间距和线宽不断减小,存储单元间发生串扰的可能性逐渐增加,因此误码率也在不断上升,需要通过On-die ECC来降低误码率。

Note:row hammer作为一种经典的内存硬件错误,即就是狂锤某一行,隔山打牛,让隔壁的行不寒而栗,在颤抖中改变立场。通俗一点的语言解释一下row hammer:DDR数据读取的过程,是通过ACT命令激活某一行row,读取到sense amp中,之后再写回到原来的cell。由于DDR芯片密度的增高,这种频繁的读写会对临近行产生影响,多次之后甚至会造成该cell的电量变化,进一步引起电平翻转。

4.35 片上ECC -- 基于协议展开介绍

DDR5设备应实现内部单错误纠正(SEC:Single Error Correction)ECC以提高DRAM内部的数据完整性。DRAM将使用128个数据位来计算8个ECC校验位的ECC码。

对于x4 DDR5设备,即使x4是64位预取设备,内部预取用于片上ECC的是128位。对于x4设备的每个读或写事务,将内部访问DRAM阵列的额外部分,以提供用于128位ECC计算中所需的额外64位。换句话说,在x4设备中,每个8位ECC校验位字与DRAM的两个64位部分相连。对于x8设备,不需要额外的预取,因为预取与外部传输大小相同。对于x16设备,从不同的内部bank(相同的外部bank地址)中提取了两个128位数据字和它们对应的8个校验位。每个128位数据位和对应的8个校验位分别并行地进行检查。

在读取时,DRAM会在将数据返回给内存控制器之前纠正任何单比特错误。在读取周期中,DRAM不会将纠正后的数据写回阵列。

在写入时,DRAM会计算ECC并将数据和ECC位写入阵列。如果外部数据传输大小小于128个数据位编码字(对于x4设备),则DRAM将需要执行内部的“读-修改-写”操作。在合并传入的写入数据之前,DRAM会纠正因内部读取而产生的任何单比特错误,并重新计算8个ECC校验位,然后将数据和ECC位写入阵列。对于x8和x16 DDR5的情况,不需要进行内部读取操作。

对于x16设备,从两个内部bank(相同的外部bank地址)读取两个136位码字(two 136-bit code words