PCIe-PCI、PCIe中断机制概述

PCI、PCIe中断概述

PCIe 中断机制在继承 PCI 传统中断(INTx)的基础上,引入了更高效的 MSI/MSI-X 方案,以提升设备性能并减少 CPU 轮询开销。以下是核心要点及技术演进:

⚙️ 一、PCIe 中断类型与演进

-

INTx(传统中断)

- 原理:通过物理引脚(INTA#~INTD#)发送电平信号,经中断控制器(如PIC/IO APIC)转换为中断请求(IRQ),CPU 通过中断向量表调用 ISR。

- PCIe 兼容性:PCIe 设备虽无物理引脚,但通过 Assert_INTx/Deassert_INTx 消息报文模拟电平变化,实现软件兼容。

- 局限:共享中断线易冲突,且需等待所有设备中断响应完成才能清除信号,效率低。

-

MSI/MSI-X(消息信号中断)

- 原理:设备直接向 Host 预设的内存地址写入特定数据(Message Data),触发内存写 TLP 报文提交中断,无需物理线路。

- 优势:

- 无共享冲突:每个中断向量独立,避免 INTx 的共享瓶颈。

- 数据一致性:中断写入操作严格按事务顺序执行,确保数据先于中断到达内存。

- 扩展性:MSI 支持 32 个连续中断向量;MSI-X 支持 2048 个非连续向量,适用多队列设备(如网卡/NVMe)。

- 配置:通过 PCIe Capability 结构(Message Address/Data 寄存器)动态设置。

⚡️ 二、中断处理流程优化

-

INTx 流程

graph LR A[设备触发INTx] --> B[中断控制器转换IRQ] B --> C[CPU 中断应答] C --> D[获取中断向量] D --> E[执行ISR]- 问题:中断状态寄存器需手动读取确认,易因异步信号导致数据竞争。

-

MSI/MSI-X 流程

graph LR A[设备写Message Address] --> B[生成Memory Write TLP] B --> C[Host 解析为中断请求] C --> D[直接触发对应ISR]- 优化点:

- 消除物理信号延迟,中断响应更快。

- 支持 中断聚合(Interrupt Coalescing),合并多个请求减少 CPU 负载。

- 优化点:

🐧 三、Linux 中的实现关键

-

中断号分配

- PCIe 设备扫描时,内核通过

of_irq_parse_and_map_pci()解析设备树中断路由,分配虚拟中断号(virq)并写入配置空间Interrupt Line寄存器。 - 驱动通过

request_irq(pci_dev->irq, ISR)注册中断处理函数。

- PCIe 设备扫描时,内核通过

-

配置空间关键寄存器

寄存器 作用 Interrupt Pin标识设备使用的中断引脚(1=INTA#, 2=INTB#, 等) Interrupt Line存储软件分配的中断号(Linux 写入 virq) MSI Capability控制 MSI 使能、消息地址/数据配置 -

性能问题解决

- 中断风暴:优化 ISR 逻辑,将耗时操作移至下半部(如 tasklet)。

- 虚拟化支持:MSI-X 的向量隔离特性更适配虚拟化环境,避免 VM 中断干扰。

⚖️ 四、设计

- 优先选用 MSI-X:尤其多队列设备(如 25G 网卡),避免向量数量瓶颈。

- 中断均衡:多核系统中,利用

irqbalance将中断分发不同 CPU 核心。 - 错误处理:

- 使能 PCIe AER(高级错误报告),结合

PERR#/SERR#捕获物理层错误。 - MSI 中断丢失时,检查 Capability 结构中的 Pending Bits 状态。

- 使能 PCIe AER(高级错误报告),结合

PCIe二种中断机制

⚙️ 一、传统INTx中断传递(Legacy Interrupt Delivery)

-

物理实现原理

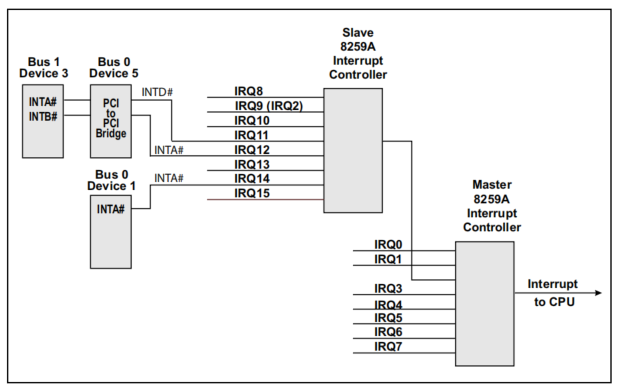

- PCI设备通过边带信号引脚(INTA#~INTD#)发送电平触发的中断请求,经中断控制器(如8259 PIC)转换为CPU可识别的INTR信号。

- 共享冲突问题:多个设备共用同一中断线(Wire-OR连接),需等待所有设备中断响应完成才能释放信号,导致延迟增加。

-

PCIe的兼容性改造

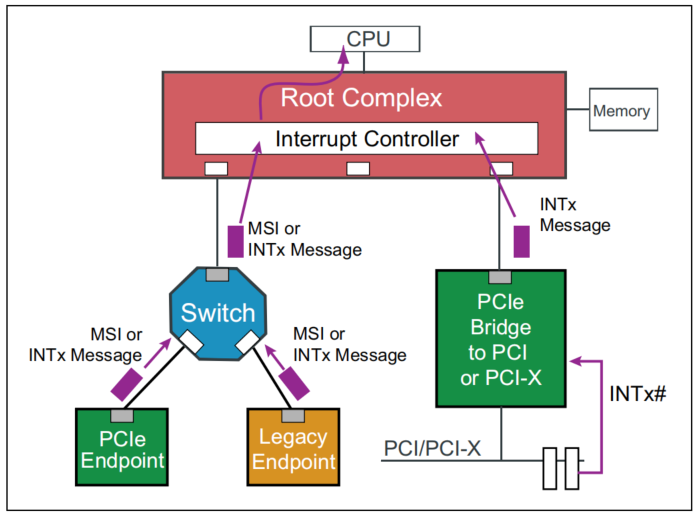

- 虚拟化实现:PCIe取消物理引脚,改用 Assert_INTx/Deassert_INTx消息报文 模拟电平变化(如Assert_INTA消息对应下降沿)。

- 桥接转换:PCIe-to-PCI桥将下游PCI设备的物理INTx#信号转换为上游的INTx消息(见图表映射关系)。

graph LR A[PCI设备物理INTx#] --> B[PCIe-PCI桥] B --> C[转换为INTx消息TLP] C --> D[Root Complex] D --> E[中断控制器] -

配置空间关键控制

- Interrupt Pin寄存器:标识设备使用的中断引脚(0=无,1=INTA#,2=INTB#等)。

- Command寄存器bit3:置1禁用INTx(仅影响传统中断,不影响MSI)。

⚡ 二、MSI/MSI-X中断传递(Message Signaled Interrupts)

-

核心机制

- 内存写入替代物理信号:设备向Host预设的Message Address写入Message Data,触发Memory Write TLP提交中断。

- 本质辨析:虽名为“Message”,实为Posted Memory Write事务,非PCIe Message TLP类型。

-

技术优势

- 无共享冲突:每个中断向量独立,避免INTx的线竞争。

- 数据一致性:MSI写操作与数据TLP遵从PCIe事务顺序规则(同TC/VC路径下保证先后顺序)。

- 扩展能力:

- MSI:支持32个连续中断向量

- MSI-X:支持2048个非连续向量,适用多队列设备(如NVMe SSD、25G网卡)。

-

配置与实现

- Capability结构:通过PCIe配置空间的MSI/MSI-X Capability寄存器配置地址与数据。

- TLP格式约束:

- Length=1 DW,First BE=1111b,Last BE=0000b

- No Snoop 和 Relaxed Ordering 必须置0。

- 驱动使能:Linux中调用

pci_enable_msi()或pci_enable_msix()激活。

⚖️ 三、INTx与MSI/MSI-X关键对比

| 特性 | INTx | MSI/MSI-X |

|---|---|---|

| 触发方式 | 电平信号/消息模拟 | 内存写入TLP |

| 共享性 | 是(易冲突) | 否(独占向量) |

| 最大中断数 | 4(INTA#~INTD#) | MSI: 32; MSI-X: 2048 |

| 延迟敏感性 | 高(需等待共享线释放) | 低(直通内存写入) |

| 配置空间依赖 | Interrupt Pin/Line寄存器 | MSI Capability结构 |

| 适用场景 | 兼容旧系统或驱动 | 高性能设备(GPU/高速网卡) |

⚠️ 四、设计注意事项与优化实践

-

INTx的局限性

- 虚拟线映射复杂性:PCIe交换机需按设备号转换INTx消息类型(如Dev1的INTA#可能映射为上游INTB#)。

- 电平保持问题:中断服务程序需手动读取状态寄存器确认中断,易因异步信号导致竞争。

-

MSI/MSI-X最佳实践

- 中断聚合(Coalescing):合并多次事件触发单次中断,减少CPU负载(如网卡收包场景)。

- 多核负载均衡:MSI-X支持向量绑定不同CPU核心,结合

irqbalance优化响应延迟。 - 错误恢复:MSI丢失时检查 Pending Bits 状态,结合AER(Advanced Error Reporting)捕获ECRC错误。

-

系统兼容性

- 混合模式风险:同时启用INTx和MSI可能导致未定义行为,建议驱动中显式禁用INTx。

- 虚拟化支持:MSI-X的向量隔离特性更适配虚拟化环境(如SR-IOV),避免VM间中断干扰。