宏汇编以及浮点程序设计实验

实验要求

- 利用重复宏定义实现1、2、3¼9数据的定义;

- 编写程序,上机验证结果的正确性

实验分析

(1)使用重复宏伪指令对数据1、2、3、4、5、6、7、8、9进行定义。

(2)先求出L×C的结果,使用FSQRT算术运算指令对其开平方根,乘2后使用FLDPI置π指令实现π的存储,然后其与前面的结果相乘。使用FLD ONE将堆栈寄存器ST(0)置1完成数字1的存储,最后使用FDIVR实现实数反除指令完成第二部分的计算。

(3)最后就是将第一部分的和值和第二部分相乘。

程序设计

- 编写重复宏程序,定义了9个初值分别为1,2,3,4...9的字节单元,Table为这些字节单元的首地址,程序如下:

.data

Table EQU THIS BYTE;宏定义 定义了9个初值分别为1,2,3,4...9的字节单元,Table为这些字节单元的首地址

COUNT = 1

REPT 9

DB COUNT

COUNT = COUNT + 1

ENDM

- 数据部分:

RESULT REAL4 ?

ADDSUM REAL4

T DW ? ; 临时变量Temp,用于存放1+2+3...+9的值,并从整形转换成实数类型的跳板

L1 REAL4 0.000001

C1 REAL4 0.000001

TWO REAL4 2.0

ONE REAL4 1.0

ZERO REAL4 0.0

_size DW 80

- 代码段:

.code

start:

MOV CX, 9;设置循环次数

FLD ZERO;给栈顶置零

LEA ESI, Table;把DS:Table的偏移地址给ESI,用于寄存器间接寻址

sum:

CMP CX, 0

JE calculation ;如果CX为零则跳转到calculation段

MOV AX, 0

MOV AL, [ESI]

MOV T, AX

FILD T;FILD指令将16位 32位或者64位有符号整数源操作数转换为双精度浮点数,并加载到ST(0)。源操作数符号保留。FILD支持的内存操作数类型和MOV一致

FADD

ADD ESI, 1

LOOP sum

calculation:

FSTP ADDSUM

FLD L1 ; 将L1入栈

FMUL C1 ; ST < -(C1) * (ST)

FSQRT ; ST < -sqrt(ST)

FMUL TWO ; ST < -(TWO) * (ST)

FLDPI ; ST < -PI

FMUL ;ST<-ST(1)*ST

FLD ONE ;ST <- 1

FDIVR ;ST <- ST/ST(1)

FMUL

FSTP RESULT ; RESULT <-ST

invoke ExitProcess,NULL

end start

查看浮点计数器进行调试。

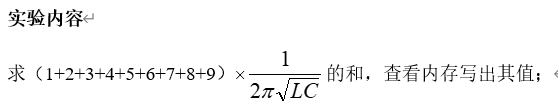

通过循环1+2+3+…+9求和,求和后的结果保存在自定义变量ADDSUM中。

图1 1+2+……+9保存在ADDSUM中

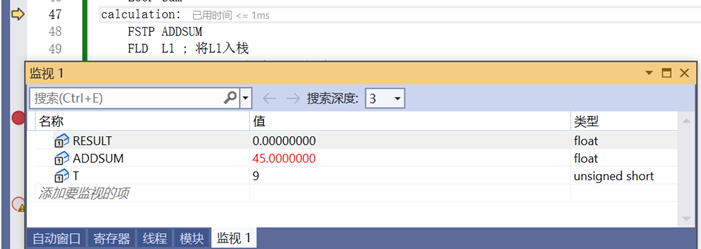

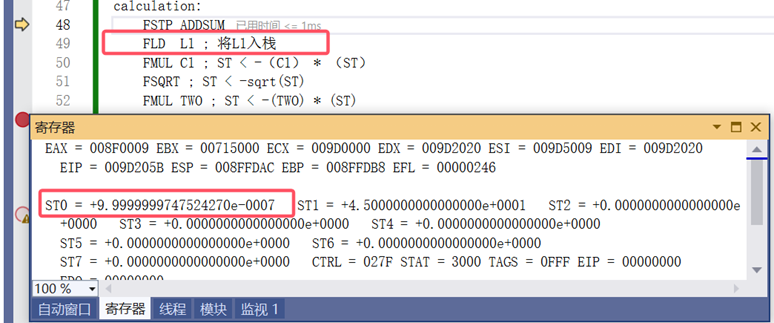

图2 L1入栈

……

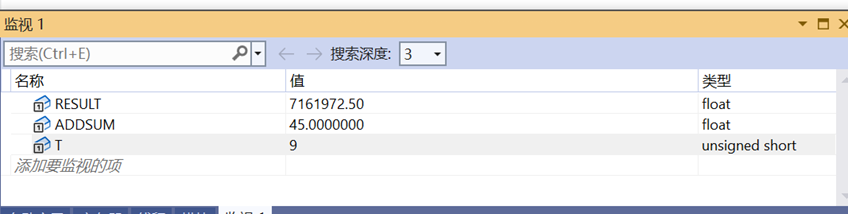

最终,运算结果保存在自定义变量RESULT中,即RESULT = ST0,然后ST0弹栈。

图11 结果

如果对你有帮助的话,请给我点个赞吧❤