论文阅读--Logical quantum processor based on reconfigurable atom arrays

论文主要内容

-

研究背景与目标:

论文提出了一种基于可重构中性原子阵列的逻辑量子处理器,旨在通过量子纠错(QEC)和逻辑量子比特编码,解决物理量子比特的噪声限制问题。该处理器结合高保真度逻辑门操作、任意连接性和实时反馈,展示了早期容错量子计算的可行性。

-

核心架构:

-

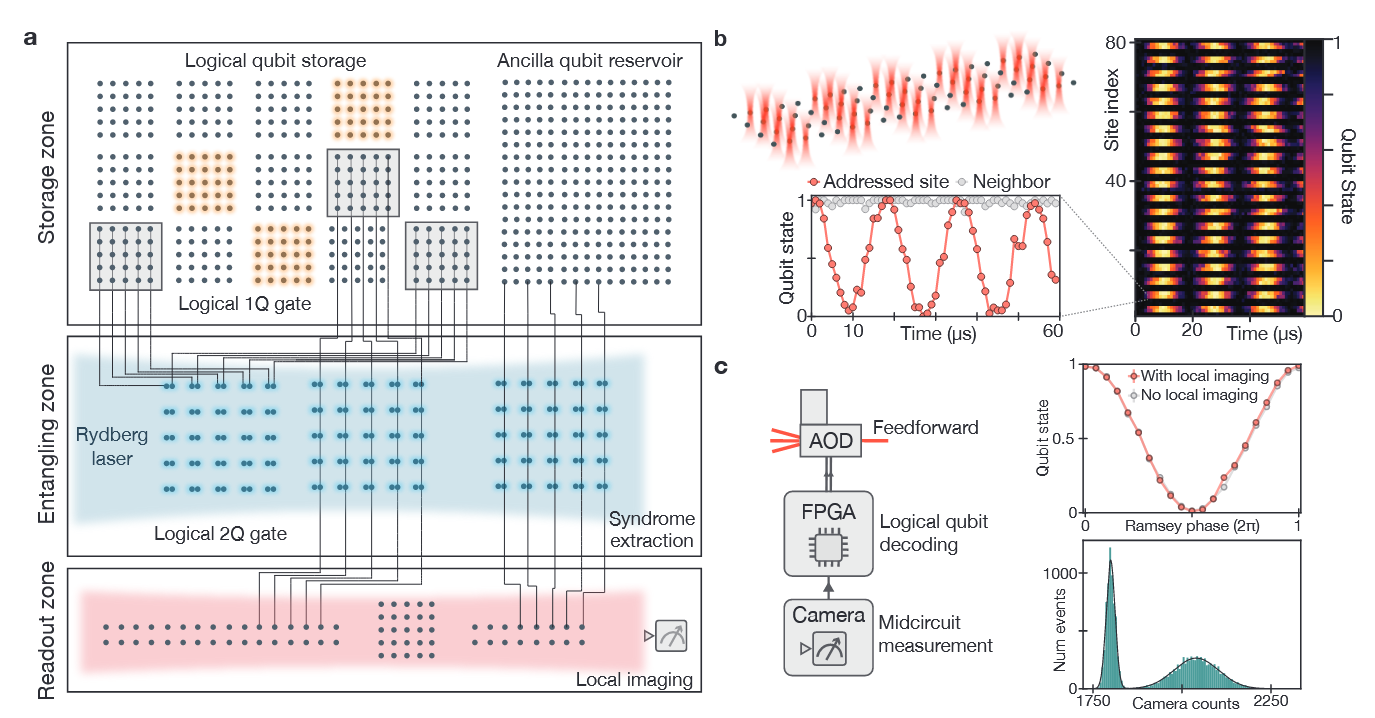

分区设计:处理器分为三个功能区域:

-

存储区:通过光学镊子稳定存储量子态,避免纠缠门干扰,相干时间超过1秒。

-

纠缠区:通过全局里德伯激发脉冲实现并行逻辑门操作(如横向CNOT)。

-

读取区:支持高保真度中途测量,不影响其他量子比特的相干性。

-

-

-

-

-

物理实现:

-

使用⁸⁷Rb原子的超精细基态编码物理量子比特,通过声光偏转器(AOD)实现动态重构和并行控制。

-

单量子比特旋转通过拉曼激光实现,双量子比特门利用里德伯阻塞效应,保真度达99.5%。

-

-

-

关键实验验证:

-

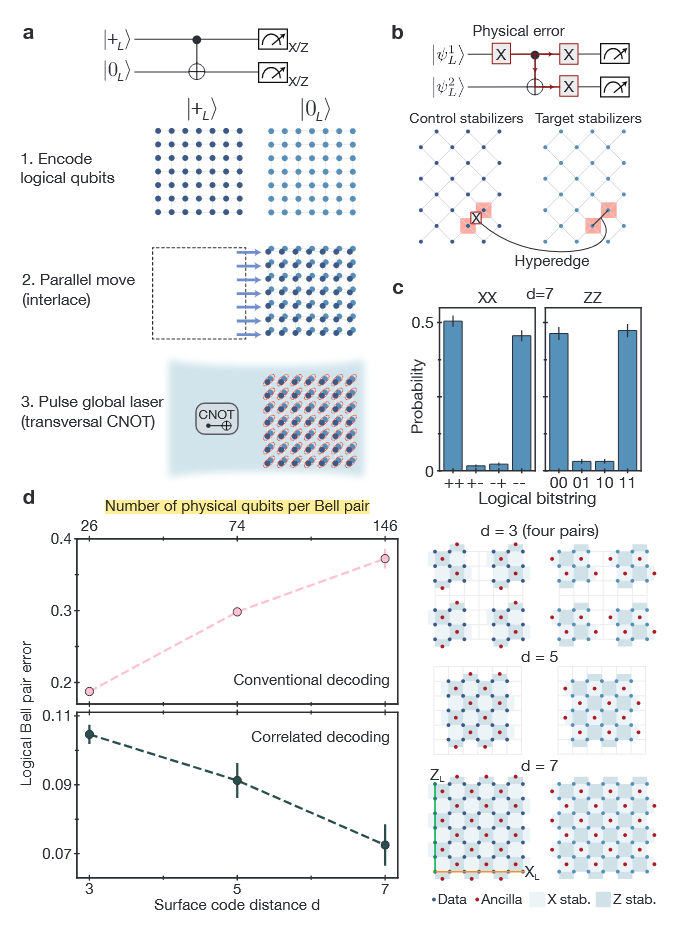

表面码逻辑纠缠门:通过增大码距(�=3d=3到�=7d=7),逻辑贝尔态保真度显著提升,验证了量子纠错的阈值效应。

-

容错逻辑算法:基于颜色码实现了10逻辑量子比特的GHZ态制备,保真度达72%,通过错误检测后提升至99.85%。

-

复杂非克利福德电路:利用三维[[8,3,2]]码实现48逻辑量子比特的快速扰乱(scrambling)电路,包含228个逻辑双量子比特门和48个逻辑CCZ门,跨熵基准(XEB)显著优于物理量子比特。

-

量子模拟应用:通过双拷贝测量技术提取纠缠熵和“魔力”(magic),验证了逻辑量子比特在模拟复杂量子系统(如黑洞扰乱)中的潜力。

-

创新点

-

硬件高效的控制架构:

-

通过分区设计和AOD技术,实现了逻辑量子比特的并行操作,减少控制线路复杂度。

-

横向逻辑门(如CNOT)通过原子网格交错和单次全局脉冲实现,兼具高效性和容错性。

-

-

码距扩展与联合解码:

-

实验验证了表面码逻辑纠缠门性能随码距增大而提升,并通过联合解码(correlated decoding)抑制物理错误传播,克服非容错态制备的局限。

-

-

三维编码与非克利福德门:

-

利用三维[[8,3,2]]码实现横向CCZ门,支持高效非克利福德电路,为经典难解问题(如IQP电路采样)提供指数加速潜力。

-

-

隐私与扩展性优势:

-

逻辑编码仅需O(logMN)次量子数据库访问,保护数据隐私;

-

分区架构支持模块化扩展,理论可扩展至数万个物理量子比特。

-

方法

-

逻辑量子比特编码:

-

表面码与颜色码:分别用于验证码距效应和容错算法,通过稳定子测量和软件纠错实现逻辑态保护。

-

三维[[8,3,2]]码:支持横向CCZ和CNOT门,通过物理比特置换和相位操作实现复杂电路。

-

-

错误检测与纠正:

-

滑动尺度错误检测:根据稳定子错误数量动态调节数据接受阈值,平衡保真度与采样效率。

-

零噪声外推:通过纯度测量外推无噪声条件下的期望值,提升模拟精度。

-

-

实验技术:

-

中途读取与反馈:通过局部成像和FPGA实时处理,实现逻辑态的条件操作(如GHZ态后选择)。

-

双拷贝测量:利用贝尔基测量提取纠缠熵和魔力,验证量子态复杂度。

-

优点

-

理论优势:

-

逻辑编码显著降低算法错误率,表面码贝尔态保真度随码距指数提升。

-

非克利福德门的横向实现突破传统拓扑码限制,支持通用量子计算。

-

-

技术突破:

-

可重构原子阵列与分区设计简化控制,支持大规模并行操作。

-

高保真度中途读取(99.8%)和实时反馈为深度电路提供关键支持。

-

-

应用潜力:

-

复杂采样电路的XEB优于物理量子比特,逼近量子优势临界点;

-

量子模拟工具(如纠缠熵测量)为研究量子多体系统提供新手段。

-

缺点与挑战

-

硬件限制:

-

当前逻辑量子比特规模有限(如40个颜色码),距离实用化仍需扩展;

-

qRAM和原子重装载技术尚未成熟,限制持续运算能力。

-

-

算法局限:

-

容错态制备依赖后选择,采样效率较低(如GHZ态需丢弃50%数据);

-

三维码的纠错能力较弱(d=2),需进一步优化编码方案。

-

-

理论挑战:

-

绝热量子算法性能依赖能隙假设,实际演化速度与温度影响未被充分讨论;

-

复杂电路的经典验证(如48逻辑量子比特)依赖高效模拟方法,限制结果的可解释性。

-