芯片生态链深度解析(二):基础设备篇——人类精密制造的“巅峰对决”

【开篇:设备——芯片工业的“剑与盾”】

当ASML的EUV光刻机以每秒5万次激光脉冲在硅片上雕刻出0.13nm精度的电路(相当于在月球表面精准定位一枚二维码),当国产28nm光刻机在华虹产线实现“从0到1”的突破,这场精密制造的全球博弈早已超越技术竞赛,成为国家科技实力的终极试炼场。据SEMI预测,2025年全球半导体设备市场规模将达1200亿美元,其中光刻机、蚀刻机、薄膜沉积与检测设备四巨头垄断超70%份额——每台售价过亿的设备背后,是材料科学、算法优化与光学工程的生死较量,更是全球产业链重构的缩影。

【系列导览】

在《芯片生态链深度解析》系列中,首篇《基础材料篇》揭开了硅片、光刻胶的“地基”密码。本文将聚焦产业链中技术壁垒最高、资本密度最大的环节——基础设备,从“卡脖子”最严重的光刻机,到国产化率不足5%的检测设备,从蚀刻机的等离子体控制到薄膜沉积的原子级工艺,解析四大核心设备的技术攻坚与突围路径。

1光刻机:芯片制造的“皇冠”

1.1 作用

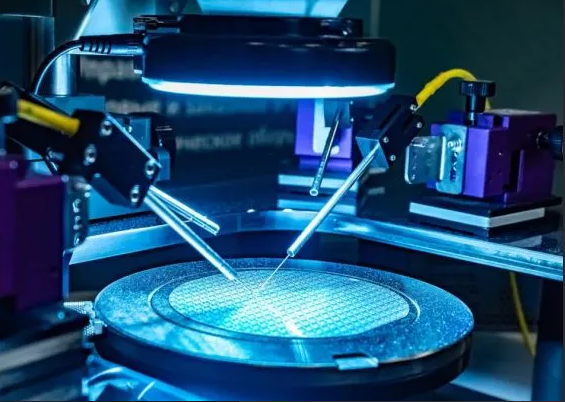

光刻机是芯片制造的核心设备,其作用类似于“纳米级雕刻大师”,将电路图案以极高的精度投射到硅片上。

-

精度要求:在7nm以下制程中,光刻机需刻画比人类头发丝小5000倍的线条(相当于在月球表面雕刻二维码),误差控制在原子级别。

-

工艺地位:芯片制造需经历20-30次光刻步骤,耗时占整个生产流程的50%,成本占比达1/3,是半导体产业链的“卡脖子”环节。

1.2 核心技术

EUV光刻技术——“纳米级手术刀”

-

原理:使用波长仅13.5nm的极紫外光(比头发丝短5万倍),通过60个高精度反射镜组成的光学系统,将电路图案缩小至8nm分辨率。

-

技术难度:EUV光会被所有材料吸收,需在真空环境中运行;反射镜表面粗糙度需控制在0.12nm以内(相当于在北京到上海的地表起伏不超过5cm)。

-

标杆产品:ASML的TWINSCAN NXE:3600D机型,每小时可处理185片晶圆,单台售价超1.2亿美元(约9亿元人民币),是工业皇冠上的明珠。

双工件台系统——“分身术”提升效率

-

原理:通过两个独立控制的工件台(一个曝光、一个测量),实现“曝光-测量”同步进行,将套刻精度提升至1.1nm(相当于在上海到北京的距离上误差不超过1毫米)。

-

意义:大幅提升生产效率,避免传统单工件台“停顿-启动”的时间损耗。

光源技术——“光刻机的心脏”

-

ASML的突破:EUV光源功率达500W(相当于将10万瓦灯泡的能量压缩到1平方厘米),可支持3nm以下制程。

-

国产差距:中国EUV光源功率仍停留在10W量级,差距约50倍,是国产化的最大瓶颈之一。

1.3 全球竞争格局

ASML的垄断地位

-

市场占比:占据全球75%光刻机市场,EUV设备100%垄断,2024年营收达235亿美元。

-

技术壁垒:供应链整合德国蔡司(光学镜片)、美国Cymer(光源)、日本东京电子(镀膜)等全球顶级厂商,形成难以复制的生态闭环。

日本企业的“中低端突围”

-

尼康、佳能:凭借i-line(365nm)、KrF(248nm)设备在成熟制程(如车载芯片)领域占据一席之地,但ArF(193nm)以上高端市场几乎归零。

-

优势领域:在面板显示、封装光刻机等细分市场仍有竞争力。

中国的“破局之路”

-

28nm突破:上海微电子SSA600/20曝光机通过中芯国际验证,实现国产替代。

-

EUV研发:中科院与上海微电子合作推进LPP(激光等离子体)光源技术,光源收集效率达15%(ASML方案为30%),预计2030年前后实现工程化。

-

政策支持:国家“十四五”规划将EUV光刻列为重点攻关领域,大基金二期投入超200亿元。

1.4 国产化挑战

技术封锁:瓦森纳协定的阴影

-

限制条款:《瓦森纳协定》禁止向中国出口14nm以下制程的光刻设备,EUV技术受严格管控。

-

影响:中芯国际7nm工艺曾因无法获得EUV设备,被迫采用多重曝光(LELE+SAQP)替代方案,成本增加30%。

零部件依赖:全球供应链的“卡脖子”

-

光源:美国Cymer垄断EUV光源,国产替代率不足5%。

-

物镜:德国蔡司主导高端光学镜片,表面粗糙度控制在0.12nm以内(相当于地球表面起伏不超过5米)。

-

工作台:德国PI(普旭)垄断超精密运动平台,定位精度达0.5nm(相当于飞机飞行1000公里误差不超过5cm)。

人才缺口:全球“抢人大战”

-

顶级人才稀缺:全球顶尖光刻机工程师不足2000人,中国相关领域博士培养量仅为美国的1/5。

-

解决路径:清华大学、中科院等机构设立“光刻专项”,联合HW、中芯国际定向培养复合型人才(光学、材料、算法跨学科)。

1.5 未来展望

-

技术路线:

-

EUV国产化:2030年前后实现LPP光源工程化,突破500W功率瓶颈。

-

计算光刻:通过AI算法优化掩模设计,降低对物理设备的依赖(参考ASML的SMO技术)。

-

纳米压印:中科院探索NIL(纳米压印光刻)技术,成本仅为EUV的1/3,适用于存储芯片领域。

-

-

产业协同:HW与上海微电子共建实验室,推动光刻机与芯片工艺的适配。

2蚀刻机:芯片制造的“雕刻刀”

2蚀刻机:芯片制造的“雕刻刀”

2.1 作用

蚀刻机是芯片制造的核心工艺设备,其作用类似于“纳米级雕刻大师”,通过等离子体或化学溶液,将光刻胶未覆盖区域的材料精准去除,形成立体电路结构。

-

3D NAND挑战:在170层以上的垂直雕刻中,需实现每层误差不超过0.5nm,相当于“在头发丝上建摩天大楼”。

-

工艺地位:芯片制造需经历20-50次蚀刻步骤,耗时占整个生产流程的30%,成本占比达15%,是半导体产业链的“关键节点”。

2.2 核心技术

等离子体控制——“原子级手术刀”

-

原理:通过射频电源激发气体产生高能等离子体(温度超1万℃),利用离子轰击和化学反应去除材料。

-

技术难度:需在亚微米尺度控制离子能量分布,避免过度损伤底层结构。应用材料的Centris Sym3系统可实现0.3nm级精度(相当于DNA双螺旋结构的1/10宽度)。

-

国产突破:中微半导体的CCp介质蚀刻机在5nm节点实现99.99%的选择比(仅去除目标材料,不损伤其他层),打破国际垄断。

多腔体协同——“流水线式雕刻工坊”

-

原理:通过多个独立反应腔(PM腔)并行作业,提升生产效率。Lam Research的Kiyo系列采用8个腔体同步作业,将晶圆处理速度提升3倍。

-

国产进展:中微刻蚀机实验室精度达0.02nm(原子级),单台设备可同时处理4片12英寸晶圆,良率超99.9%。

选择性蚀刻——“精准识别材料的“侦探”

-

技术核心:通过调节蚀刻气体或化学溶液配比,实现对特定材料的高效去除。例如,在5G射频芯片中,需对氮化镓(GaN)和二氧化硅(SiO₂)进行差异化蚀刻。

-

应用场景:3D NAND堆叠层数突破500层后,需依赖选择性蚀刻技术确保每层通孔对齐误差<1nm。

2.3 全球竞争格局

美企主导:应用材料与泛林的双寡头格局

-

市场占比:应用材料(AMAT)、泛林半导体(Lam Research)占据全球47%蚀刻机市场,尤其在介质蚀刻、导体蚀刻领域形成技术壁垒。

-

技术优势:应用材料的Centris平台支持5nm以下制程,泛林的Kiyo系列在3D NAND领域市占率超60%。

中国突破:从“跟跑”到“并跑”

-

中微半导体:5nm蚀刻机进入台积电供应链,CCp介质蚀刻机良率超99.9%,单台售价约2000万美元(仅为ASML光刻机的1/5)。

-

北方华创:硅通孔蚀刻机在长江存储、合肥长鑫产线实现批量应用,市占率达12%。

-

政策支持:国家大基金二期向蚀刻机领域注资超30亿元,重点支持12英寸设备研发。

日本力量:东京电子的“细分赛道”

-

技术优势:在12英寸硅片刻蚀领域保持领先,设备兼容性强,可适配28nm-7nm全制程。

-

市场份额:受中美竞争影响,日本蚀刻机全球份额不足8%,但在车载芯片领域仍有竞争力。

2.4 国产化进展

技术突破:中微的“零的突破”

-

CCp介质蚀刻机:通过台积电5nm认证,关键指标(选择比、均匀性)达国际先进水平,单台设备可替代3台进口设备。

-

陶瓷部件国产化:中微自主研发的静电吸盘、聚焦环等陶瓷部件,耐等离子体腐蚀性能提升50%,成本降低30%。

产能爬坡:长江存储的“国产化试验田”

-

采购数据:长江存储二期产线采购的200台蚀刻机中,国产设备占比从5%提升至18%,预计2025年达30%。

-

协同创新:中微与HW共建联合实验室,针对3nm GAA晶体管结构开发新型蚀刻工艺。

政策红利:大基金与地方补贴双轮驱动

-

大基金二期:注资30亿元支持12英寸蚀刻机研发,重点突破原子层蚀刻(ALE)技术。

-

地方补贴:上海临港、深圳光明科学城等地对蚀刻机企业给予15%-20%研发投入返还。

2.5 未来展望

-

技术路线:

-

原子层蚀刻(ALE):中微与中科院合作推进ALE技术,可在1nm以下节点实现单原子层去除。

-

混合蚀刻:结合干法(等离子体)与湿法(BOE蚀刻液)工艺,提升3D NAND深孔结构加工效率。

-

AI控制:应用材料已推出Enlight光学监测系统,通过实时反馈优化蚀刻参数,国产设备正加速跟进。

-

-

产业协同:HW与中微共建实验室,推动蚀刻机与芯片工艺的适配。

3薄膜沉积设备:芯片制造的“涂装师”

3.1 作用

薄膜沉积设备是芯片制造的核心工艺设备,其作用类似于“纳米级贴膜师”,在硅片表面沉积金属、绝缘体等薄膜材料,构建芯片的“骨架”与“血管”。

-

工艺需求:在3nm芯片中,需沉积超100层薄膜(较90nm制程翻倍),总厚度不足人类头发直径的1/10(约5μm),每层误差需控制在0.1nm以内。

-

产业地位:薄膜沉积设备占晶圆制造设备成本的22%,2023年全球市场规模达211亿美元,预计2025年将突破300亿美元。

-

技术演进:从2D NAND到3D NAND(层数超170层),薄膜沉积需求激增;FinFET晶体管结构的复杂化进一步推动设备需求增长。

3.2 核心技术

原子层沉积(ALD)——“原子级画师”

-

原理:通过脉冲式通入气相前驱体,在基底表面发生饱和化学反应,逐层沉积单原子层薄膜。每层厚度约0.1nm(10次镀膜≈1nm)。

-

技术难度:需实现表面饱和反应控制、高均匀性(深宽比>100:1的结构仍能均匀覆盖)、低污染(杂质含量<1ppm)。

-

标杆产品:ASM International的Navigator ALD设备,单层沉积精度达0.1nm,应用于3D NAND字线、钨插塞等关键工艺,良率超99.9%。

-

国产进展:微导纳米开发的PEALD设备在5nm逻辑芯片实现氧化铝(Al₂O₃)沉积,均匀性误差<0.5%。

化学气相沉积(CVD)——“高温熔炉”

-

原理:通过高温(800-1200℃)使气态前驱体在硅片表面发生化学反应,生成固态薄膜(如二氧化硅、氮化硅)。

-

细分领域:

-

PECVD(等离子体增强CVD):在300-400℃低温下成膜,占全球CVD市场30%(2023年约63亿美元),应用如STI浅槽隔离、金属层间介质。

-

HDPCVD(高密度等离子体CVD):通过磁场约束等离子体,实现高深宽比(>8:1)结构填充,泛林半导体的Centura平台市占率超40%。

-

-

标杆产品:应用材料的Producer PECVD系统支持12英寸晶圆沉积,产能达200片/小时,介质膜致密度达2.2g/cm³。

-

国产突破:拓荆科技的PECVD 2800设备通过中芯国际28nm验证,氧化硅(SiO₂)沉积速率较进口设备提升15%。

物理气相沉积(PVD)——“原子级溅射枪”

-

原理:利用高能离子轰击金属靶材,溅射出原子并沉积在硅片表面,形成金属导电层(如铜、钴)。

-

技术难点:需平衡薄膜附着力(>50MPa)、均匀性(误差<2%)、高深宽比结构填充能力。

-

细分领域:

-

溅射PVD:占PVD市场70%,爱发科(Ulvac)的Magnetron溅射设备在铜互联领域市占率超70%。

-

ECD(电化学沉积):用于铜大马士革工艺,应用材料的Electra系统实现3nm节点铜填充,电阻率<1.8μΩ·cm。

-

-

国产进展:北方华创的Hermes PVD设备在长江存储3D NAND产线实现钴硬掩膜沉积,市占率突破5%。

3.3 全球竞争格局

欧美日垄断:应用材料、ASM、爱发科的“铁三角”

-

市场集中度:CR3(应用材料、ASM、东京电子)市占率达72%。应用材料以43%份额居首,ASM在ALD领域占46%。

-

技术壁垒:应用材料垄断PECVD高端市场(80%以上逻辑芯片产线),ASM的SACVD(选择性CVD)设备在苹果A系列芯片封装中市占率100%。

中国追赶:拓荆、北方华创的“双雄战略”

-

拓荆科技:CVD设备龙头,2023年营收28亿元,PECVD 2800进入中芯国际28nm产线,氧化硅沉积均匀性达±1.5%。

-

北方华创:PVD设备领跑者,Hermes PVD在长江存储3D NAND产线替代东京电子设备,单台售价约800万美元。

-

政策支持:国家大基金二期向拓荆科技注资12亿元,重点支持ALD设备研发。

日韩力量:东京电子、SEMES的“细分赛道”

-

东京电子:在LPCVD(低压CVD)领域市占率36%,设备兼容28nm-7nm全制程,但受中美竞争影响,全球份额不足11%。

-

韩国SEMES:专注半导体显示设备,CVD设备在OLED面板领域市占率超60%。

3.4 国产化挑战

技术封锁:瓦森纳协定的阴影

-

限制条款:禁止向中国出口14nm以下制程的ALD、PECVD设备,拓荆科技14nm设备曾因无法获取美国射频电源被迫延期交付。

-

应对策略:中科院联合拓荆开发国产射频电源,功率稳定性达±0.1%

3.4 未来展望

-

需求驱动:5G、AI、存储芯片堆叠层数提升(3D NAND超170层),薄膜沉积工序翻倍。

-

产业协同:设备厂商与晶圆厂(如中芯国际、长江存储)深度绑定,加速工艺适配。

-

智能化升级:AI优化沉积参数,良率提升至99.9%以上。

4检测设备:芯片制造的“质检员”

4.1 作用

检测设备是芯片制造过程中控制良率的关键环节,通过光学、电子束等技术实现纳米级缺陷识别。在先进制程(如3nm及以下)中,设备需满足:

-

超高速扫描:单台设备每秒完成超10万次扫描(如KLA-Tencor的Hercules检测系统)。

-

超高精度:缺陷识别能力达亚纳米级(0.5-1nm),确保晶圆良率稳定在99.99%以上。

-

全流程覆盖:涵盖薄膜厚度、关键尺寸(CD)、表面缺陷等200余项参数检测。

4.2 核心技术

-

电子束检测:KLA-Tencor的eDR7380系统分辨率达0.8nm,可检测出单个原子级别的缺陷。

-

光学检测:Onto Innovation的UVision系统通过深紫外光实现3D形貌重建,检测速度达8000片/小时。

-

AI质检:中科飞测将深度学习应用于缺陷分类,误报率从5%降至0.5%。

4.3 全球竞争格局

-

美国主导:KLA-Tencor占据全球54%检测设备市场,在电子束、光学检测领域形成双垄断。

-

中国突破:上海精测半导体前道检测设备进入华虹宏力12英寸产线,中科飞测AI质检系统商业化落地。

-

日本力量:日立高新在CD-SEM领域保持技术优势,但市场份额不足10%。

4.4 国产化挑战

-

核心部件依赖:电子束检测的高亮度灯丝(依赖FEI)、光学系统的超低畸变镜头(蔡司垄断)仍需进口。

-

工艺适配性:GAA晶体管三维结构检测需突破多角度照明、偏振光分析等关键技术。

4.5 未来方向

-

混合检测技术:结合电子束与光学检测优势(如KLA的Surfscan+eScan系统),兼顾速度与精度。

-

智能化升级:AI预测性维护(如应用材料的Enlight AI系统)降低设备停机时间,国产厂商正开发类似技术。

-

绿色制造:低能耗电子束源、无汞紫外光源等环保工艺将成为行业标准。

【未来展望:设备突围的“三大战役”】

-

EUV光刻机攻坚:

-

中科院联合企业启动“EUV光源攻关计划”,目标2030年实现500W功率突破。

-

纳米压印技术(NIL)成本仅为EUV的1/3,或成存储芯片领域替代方案。

-

-

产业链协同创新:

-

中芯国际联合北方华创、中微半导体成立“先进制程设备联盟”,加速设备与工艺适配。

-

HW与拓荆科技合作开发ALD+CVD混合沉积工艺,目标3nm GAA晶体管。

-

-

智能化与绿色制造:

-

AI优化沉积参数(如应用材料Enlight系统),良率提升至99.9%以上。

-

低能耗电子束源、无汞紫外光源成为环保标准。

-

结语:设备革命即未来

从EUV光刻机的13.5nm光源到蚀刻机的等离子体控制,从ALD原子层沉积到AI驱动的缺陷检测,芯片设备正以超越摩尔定律的速度进化。当ASML的EUV设备需40艘集装箱运输,而国产28nm光刻机实现“从0到1”的突破时,我们愈发确信:芯片战争的本质是设备战争。这场战争不仅关乎光刻机的精度、检测设备的智能,更是一场材料科学、精密制造与算法生态的全面较量。设备革命的终点,将是人类制造能力的边界——而中国,正在这条边界上刻下自己的坐标。

系列预告:芯片设计篇——从EDA到架构的“智慧博弈”

下期《芯片生态链深度解析(三):芯片设计篇》

我们将聚焦芯片产业的“大脑”——设计环节,揭秘:

-

EDA软件:如何通过算法优化决定芯片性能的90%?国产工具(如华大九天)能否突破Synopsys垄断?

-

RISC-V架构:开源生态如何挑战ARM的移动市场霸权?阿里平头哥倚天710、HW鲲鹏的“去ARM化”路径分析。

-

架构创新:存算一体、光子计算等颠覆性设计如何重塑AI芯片格局?寒武纪、壁仞科技的突围案例。