[IMX] 02.GPIO 寄存器

目录

手册对应章节

1.GPIO 复用(引脚功能选择)- IOMUXC_SW_MUX_CTL_PAD_xxx

2.GPIO 电气特性 - IOMUXC_SW_PAD_CTL_PAD_xxx

3.GPIO 数据与控制寄存器

3.1.数据 - DR

3.2.输入/输出选择 - GDIR

3.3.状态 - PSR

3.4.中断触发控制 - ICR

3.5.中断使能 - IMR

3.6.中断状态 - ISR

3.7.边沿中断 - EDGE_SEL

手册对应章节

// GPIO:28 General Purpose Input/Output (GPIO)

// IOMUX:32 IOMUX Controller (IOMUXC)IMX 提供了多个 GPIO 组,每个 GPIO 组包含多个 GPIO 接口(IO0~IOx),这些接口用于连接 Ethernet、SPI 等

IO 接口可以用于不同的模块,但其数量有限,因此不可避免的需要进行 IO 复用,即多个设备通过 PAD 连接在一个 IO 接口上,IMX 通过 IOMUXC(IOMUX Controller)控制 GPIO 复用

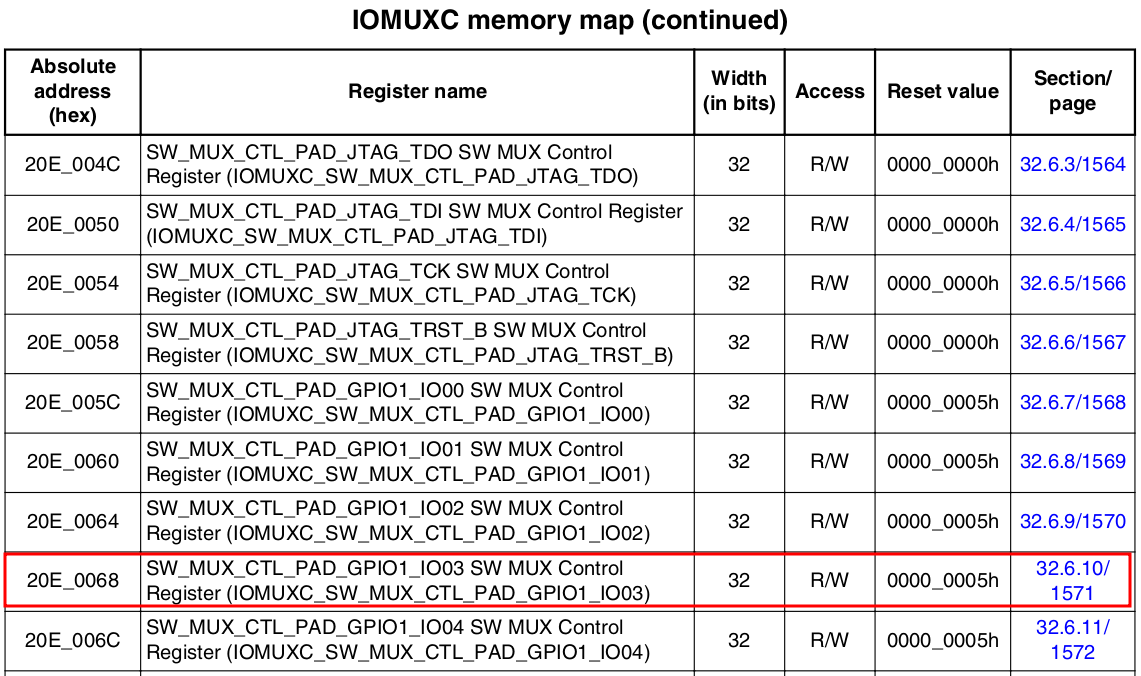

1.GPIO 复用(引脚功能选择)- IOMUXC_SW_MUX_CTL_PAD_xxx

以 GPIO1 组中的 IO03 为例:

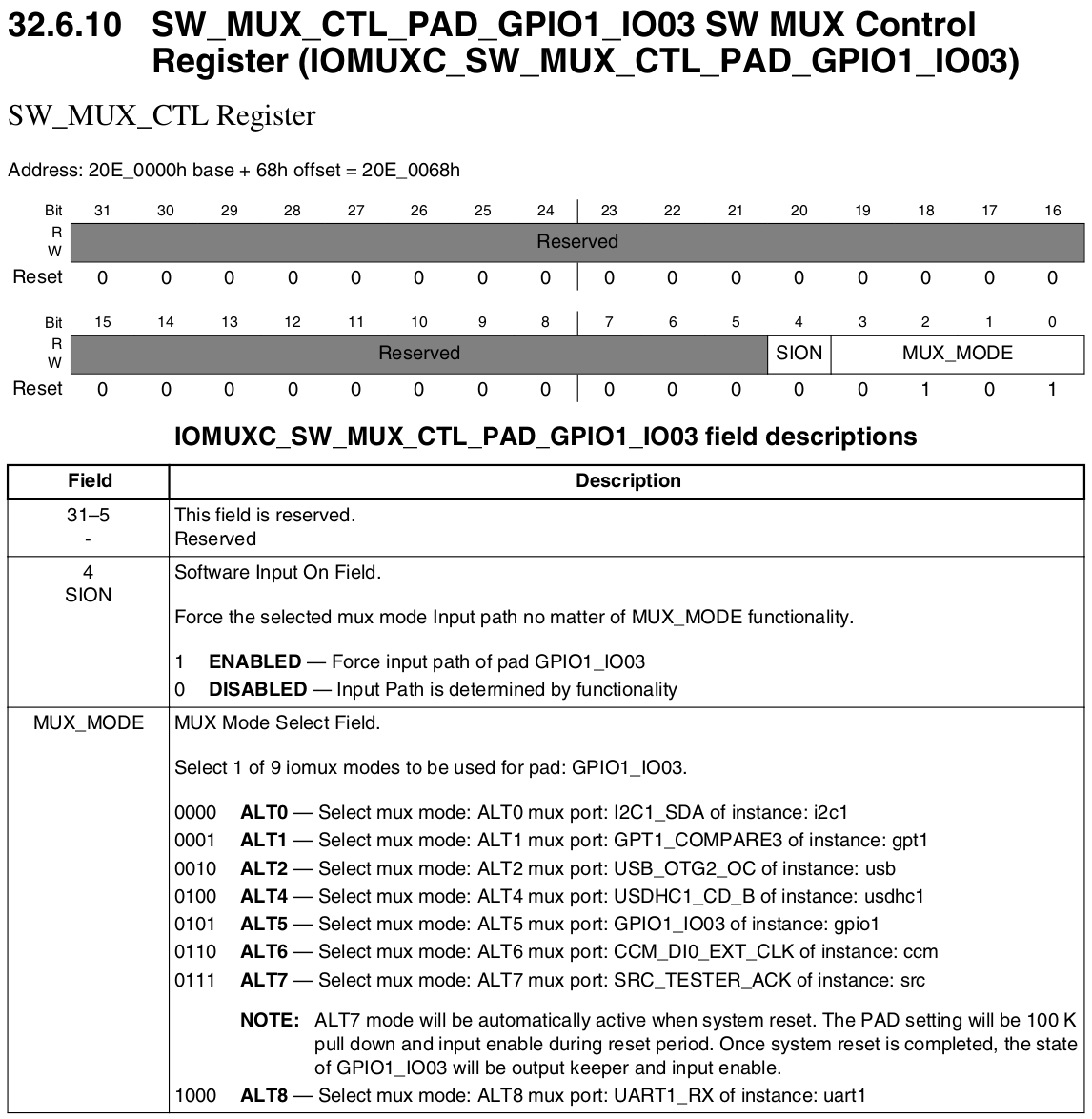

IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO03 寄存器控制 GPIO1_IO03 引脚的功能复用:

该寄存器包含两个字段,其功能如下:

-

SION[4]:Software Input On,强制引脚功能为 GPIO1_IO03(可通过软件设置,忽略该引脚的功能复用):

-

1:使能,引脚功能强制为 GPIO1_IO03,从而忽略 MUX_MODE 配置的功能复用;

-

0:禁用,引脚功能由 MUX_MODE 字段定义;

-

-

MUX_MODE[3:0]:MUX Mode Select,设置引脚功能:

-

0b0000:ALT0,i2c1 模块的 I2C1_SDA 引脚;

-

0b0001:ALT1,gpt1 模块的 GPT1_COMPARE3 引脚;

-

0b0010:ALT2,usb 模块的 USB_OTG2_OC 引脚;

-

0b0100:ALT4,usdhc1 模块的 USDHC1_CD_B 引脚;

-

0b0101:ALT5,gpio1 模块的 GPIO1_IO03 引脚;

-

0b0110:ALT6,ccm 模块的 CCM_DI0_EXT_CLK 引脚;

-

0b0111:ALT7,src 模块的 SRC_TESTER_ACK 引脚;

-

0b1000:ALT8,uart1 模块的 UART1_RX 引脚;

-

注意:当 SION 位置 1 后,引脚功能会被强行设置为 GPIO1_IO03,此时通过 MUX_MODE 设置引脚功能无效

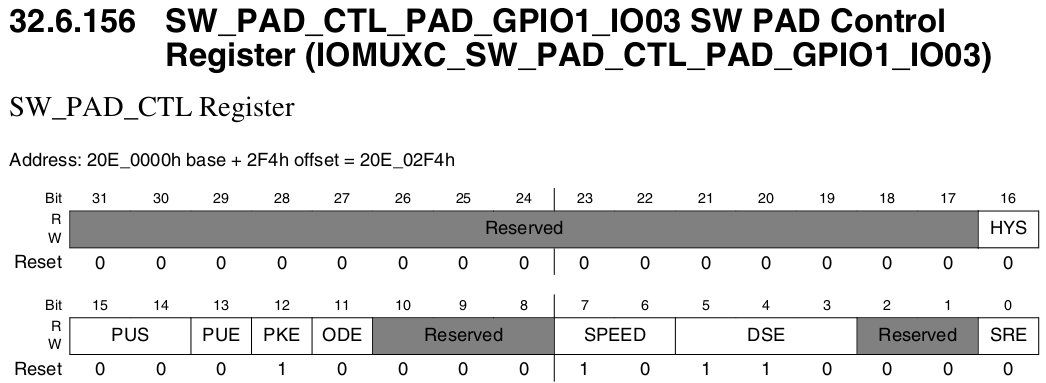

2.GPIO 电气特性 - IOMUXC_SW_PAD_CTL_PAD_xxx

IOMUXC_SW_PAD_CTL_PAD_xxx 寄存器控制引脚的电气特性,以 IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO03 为例:

寄存器中各字段的含义如下:

-

HYS[16]:Hyst. Enable,使能迟滞比较器,当 IO 作为输入功能时有效,用于设置输入接收器的施密特触发器是否使能,如果需要对输入波形进行整形可以使能此位:

-

1:HYS_0_Hysteresis_Disabled,禁用施密特触发器;

-

0:HYS_1_Hysteresis_Enabled,使能施密特触发器;

-

-

PUS[15:14]:Pull Up / Down Config,上拉/下拉电阻设置:

-

00:PUS_0_100K_Ohm_Pull_Down,100K 下拉;

-

01:PUS_1_47K_Ohm_Pull_Up,47K 上拉;

-

10:PUS_2_100K_Ohm_Pull_Up,100K 上拉;

-

11:PUS_3_22K_Ohm_Pull_Up,22K 下拉;

-

-

PUE[13]:Pull / Keep Select,上拉/下拉 or 状态保持器,当 IO 作为输入时,用于设置 IO 使用上拉/下拉还是状态保持器控制引脚:

-

0:PUE_0_Keeper,状态保持器;

-

1:PUE_1_Pull,上拉/下拉;

-

注意:状态保持器在 IO 作为输入时有效,当外部电路断电后此 IO 口可以保持住以前的状态;

-

-

PKE[12]:Pull / Keep Enable,是否使能状态保持器:

-

0:PKE_0_Pull_Keeper_Disabled,禁用;

-

1:PKE_1_Pull_Keeper_Enabled,使能;

-

状态保持器的作用是持续输出设定的电平,而非脉冲信号,例如,引脚配置输出高电平,同时使用了状态保持器,触发引脚输出后,引脚将持续输出高电平,而非一个高电平脉冲;

-

-

ODE[11]:Open Drain Enable,开漏输出使能:

-

0:ODE_0_Open_Drain_Disabled,禁用开漏输出;

-

1:ODE_1_Open_Drain_Enabled,使能开漏输出;

-

-

SPEED[7:6]:Speed,设置 IO 口的速率:

-

00:SPEED_0_low_50MHz_,低速率 50MHz;

-

01:SPEED_1_medium_100MHz_,中等速率 100MHz;

-

10:SPEED_2_medium_100MHz_,中等速率 100MHz;

-

11:SPEED_3_max_200MHz_,高速率 200MHz;

-

-

DSE[5:3]:Drive Strength,设置 IO 口的驱动能力:

-

000:DSE_0_output_driver_disabled_,禁用输出驱动;

-

001:DSE_1_R0_260_Ohm___3_3V__150_Ohm_1_8V__240_Ohm_for_DDR_,3.3V 下 R0 是 260Ω,R0,1.8V 时 R0 为 150Ω,接 DDR 时 R0 为 240Ω;

-

010:DSE_2_R0_2,R0/2;

-

011:DSE_3_R0_3,R0/3;

-

100:DSE_4_R0_4,R0/4;

-

101:DSE_5_R0_5,R0/5;

-

110:DSE_6_R0_6,R0/6;

-

111:DSE_7_R0_7,R0/7;

-

-

SRE[0]:Slew Rate,设置压摆率,压摆率就是 IO 电平跳变所需的时间,比如从 0 到 1 需要多少时间,时间越小波形越陡,说明压摆率越高,反之,时间越大波形越缓,压摆率越低,如果产品要过 EMC 则可以使用较低的压摆率,因为波形缓和,如果使用 IO 做高速通信则可以使用高压摆率:

-

0:SRE_0_Slow_Slew_Rate,低压摆率;

-

1:SRE_1_Fast_Slew_Rate,高压摆率;

-

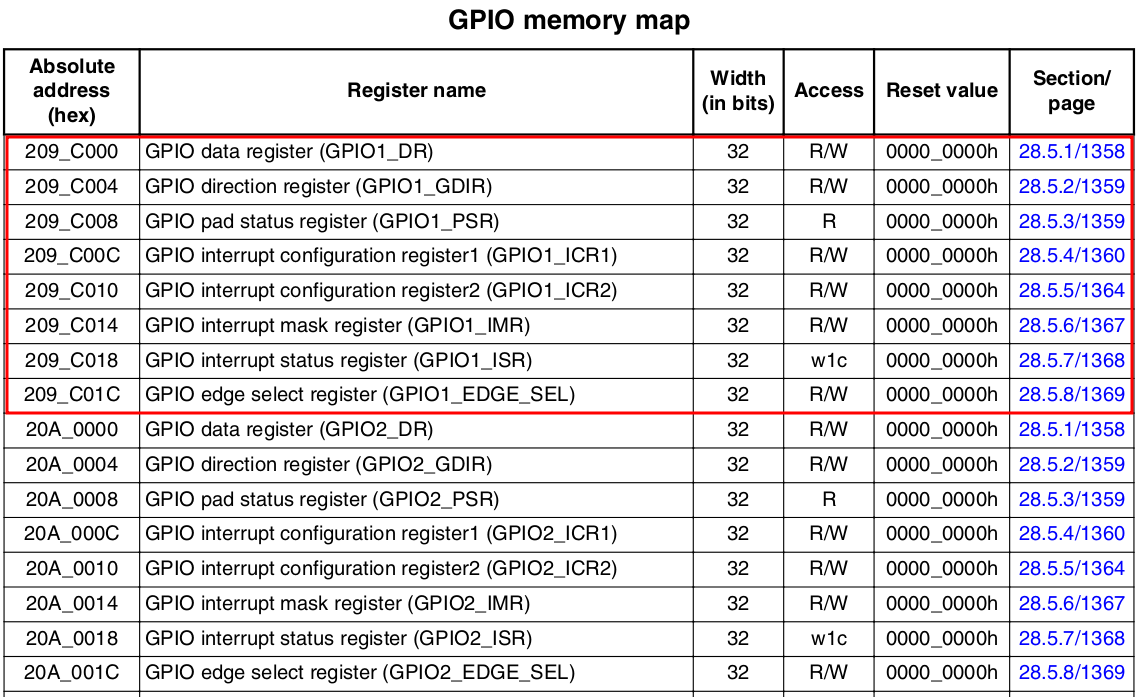

3.GPIO 数据与控制寄存器

每个 GPIO 组都有对应的数据和控制寄存器,用于操作该 GPIO 组内的每个 GPIO 引脚,以 GPIO1 组为例:

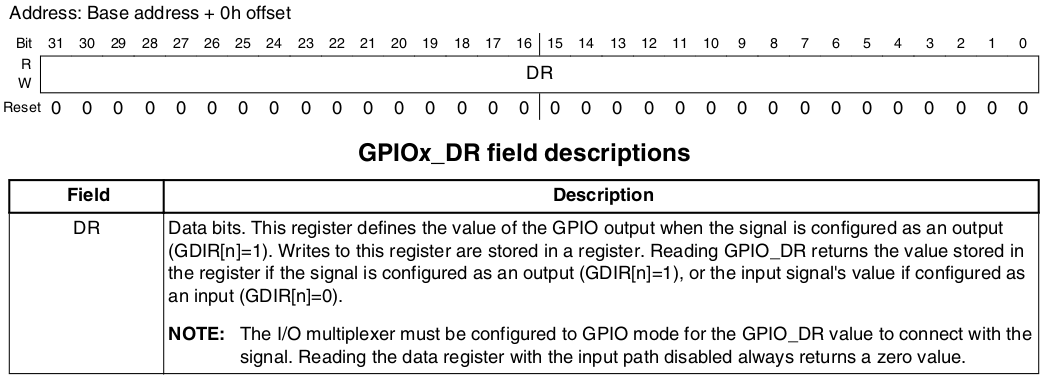

3.1.数据 - DR

其中,GPIOx_DR 寄存器用于控制该 GPIO 组内具体引脚的输出值、以及该 GPIO 组内引脚读取到的输入值:

每个 GPIO 组最多可拥有 32 个引脚,这些引脚可以配置为输入引脚或输出引脚

GPIOx_DR 寄存器的每一位都对应于该 GPIO 组内的一个引脚,当引脚配置为输出模式后,向对应的位写 1 就可以控制该引脚输出高/低电平,当引脚被配置为输入模式后,读取对应的位即可获得该引脚读取到的电平值,例如,要设置 GPIO1_IO03 输出高电平,则需要设置 GPIO1.DR = 0x8,当 GPIO1_IO03 引脚接地的话,则 GPIO1.DR 寄存器 bit-4 的值为 0,若 GPIO1_IO03 配置为输入引脚,则读取 GPIO1.DR 寄存器的 bit-4 即可获取该引脚目前的电平

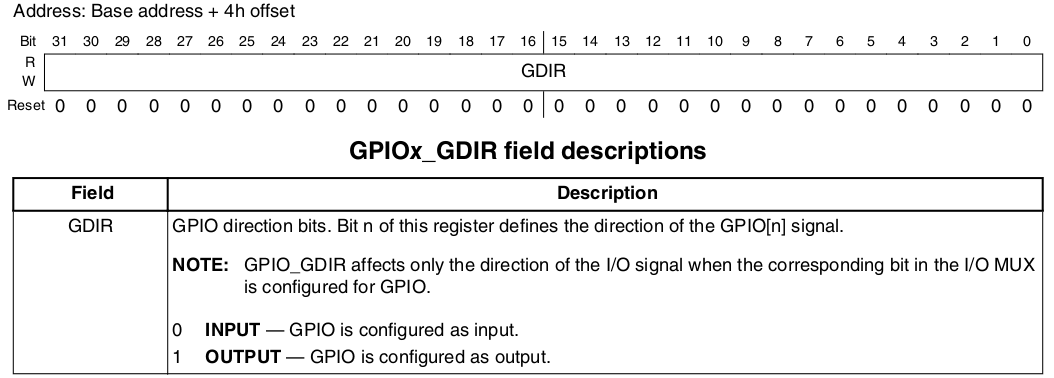

3.2.输入/输出选择 - GDIR

当 GPIO 组中某个引脚的功能选择为通用 GPIO 后(通过 IOMUX Controller),通过 GPIOx_GDIR 寄存器设置该 GPIO 组中,各引脚为输入模式还是输出模式:

-

0:INPUT,引脚配置为输入引脚;

-

1:OUTPUT,引脚配置为输出引脚;

同样的,GPIOx_GDIR 寄存器中的每一位对应该 GPIO 组内的一个引脚,例如,GPIO1_GDIR 的 bit-4 对应 GPIO1_IO03

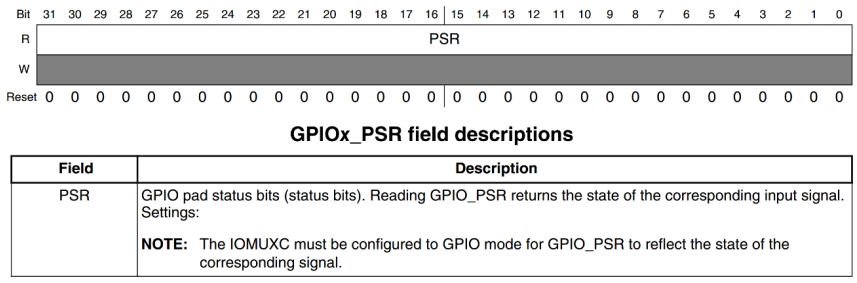

3.3.状态 - PSR

GPIOx_PSR 寄存器为只读寄存器,其每个位对应该 GPIO 组内的一个引脚:

读取对应的位即读取该引脚当前的电平状态,其功能与 GPIOx_DR 读取输入引脚的功能一样,其区别在于,GPIOx_PSR 只会在访问该寄存器时才会读取引脚的输入值

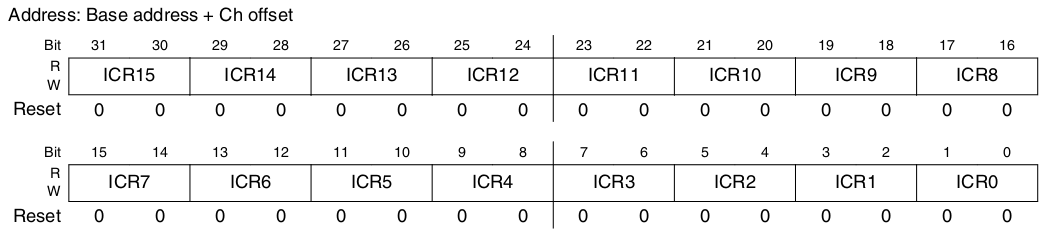

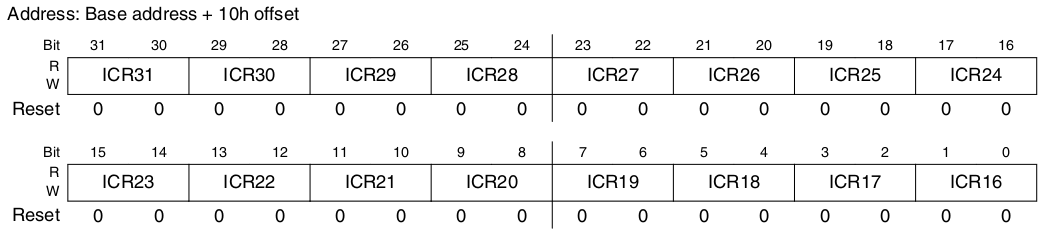

3.4.中断触发控制 - ICR

GPIOx_ICR1 寄存器控制 GPIO 组内 0~15 引脚的中断触发信号:

GPIOx_ICR2 寄存器控制 GPIO 组内 16~31 引脚的中断触发信号:

每个引脚对应两个位,控制中断为高/低电平、上升沿/下降沿触发:

-

00:LOW_LEVEL,低电平触发;

-

01:HIGH_LEVEL,高电平触发;

-

10:RISING_EDGE,上升沿触发;

-

11:FALLING_EDGE,下降沿触发;

以 GPIO1_IO15 为例,如果要设置 GPIO1_IO15 为上升沿触发中断,则应该设置 GPIO1.ICR1 = 2 << 30, 如果要设置 GPIO1 的 IO16~31 则需要设置 ICR2 寄存器

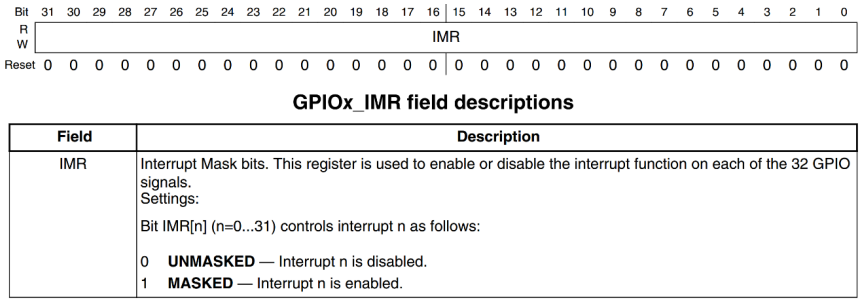

3.5.中断使能 - IMR

GPIOx_IMR 寄存器控制对应引脚的中断是否使能:

-

0:MASKED,禁止该引脚触发中断;

-

1:UNMASKED,允许该引脚触发中断;

例如,要使能 GPIO1_IO00 的中断,则应该设置 GPIO1.MIR |= 0x1

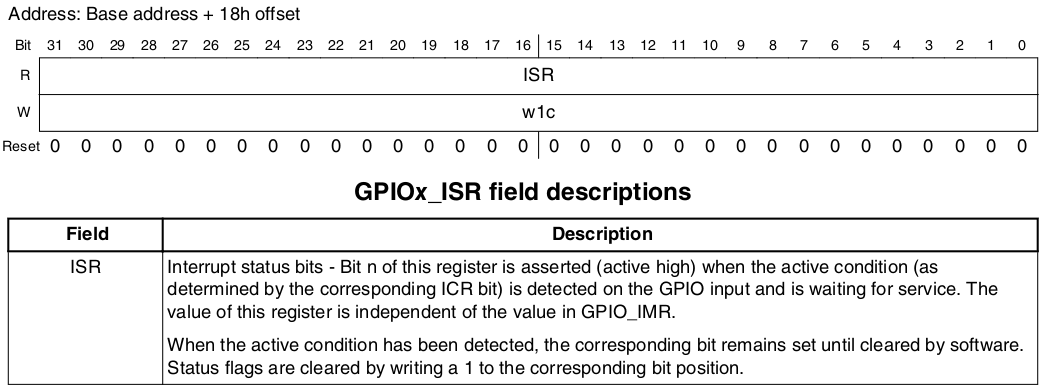

3.6.中断状态 - ISR

中断状态寄存器 GPIOx_ISR 指示对应引脚是否产生了中断请求:

例如,如果 GPIO1_ISR 寄存器的 bit-4 为 1,则表示 GPIO1_IO03 产生了中断信号(中断请求)

处理完中断后必须清除中断标志位,清除方法是向 ISR 寄存器中相应的位写 1(即写 1 清零)

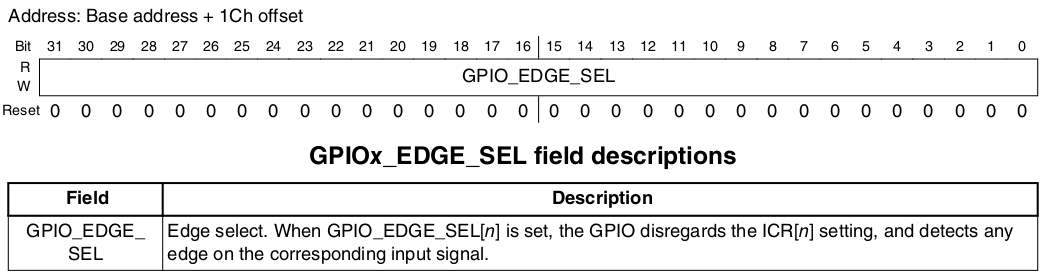

3.7.边沿中断 - EDGE_SEL

该寄存器的每一位对应该 GPIO 组内的一个引脚:

对应位置 1 后,该引脚的上升沿和下降沿(双边沿)均会触发中断请求,该寄存器中的设置会覆盖引脚对应的 ICR 寄存器中的设置