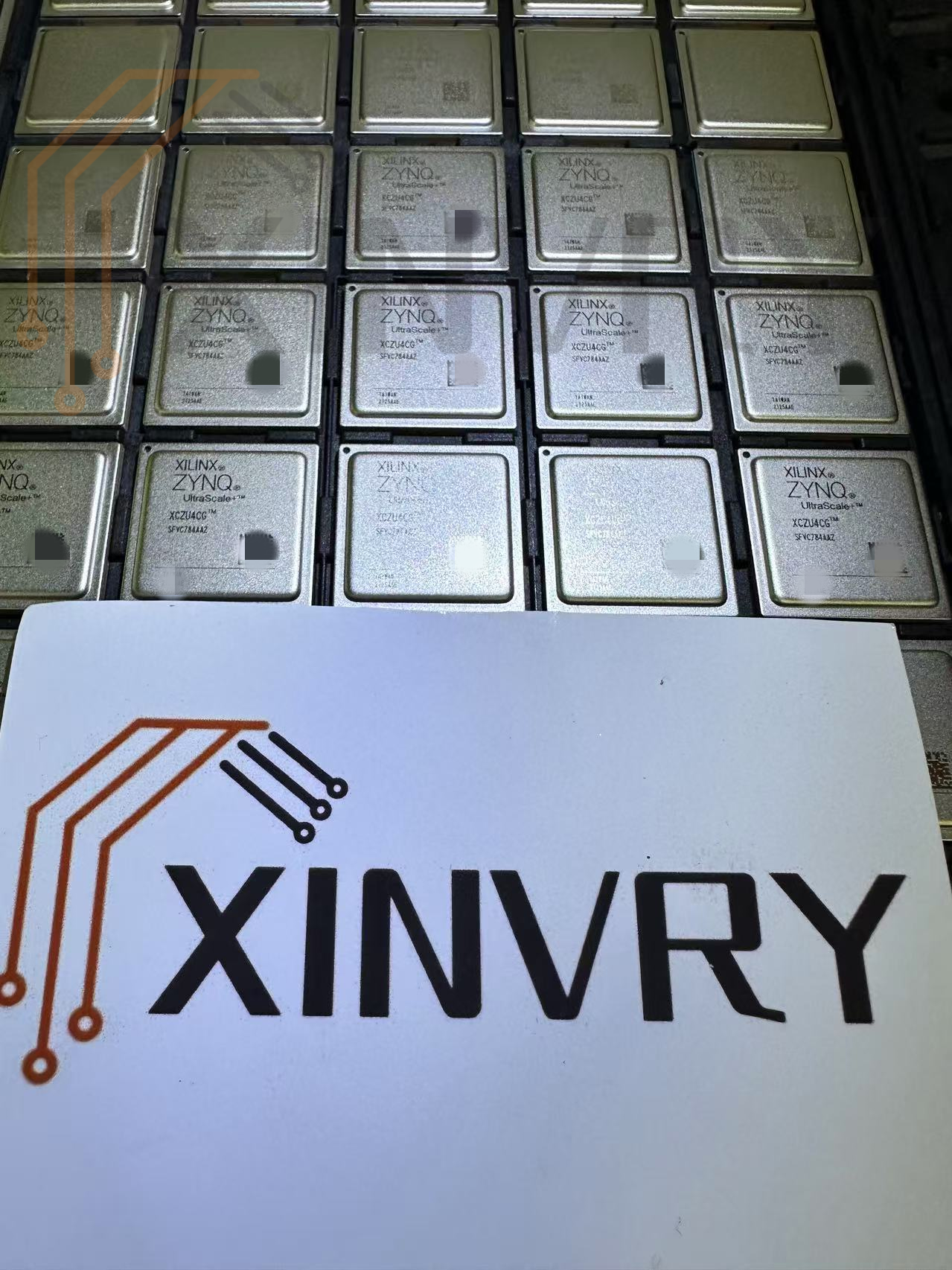

XCZU4CG‑2SFVC784I 赛灵思 FPGA XilinxZynq UltraScale+ MPSoC

XCZU4CG‑2SFVC784I 是 AMD Xilinx Zynq UltraScale+ MPSoC CG 系列中的入门级高性能 SoC FPGA,集成了双核 Arm Cortex‑A53 通用处理器与双核 Arm Cortex‑R5F 实时处理器,以及可编程逻辑(PL)资源。

异构处理系统 (PS)

应用处理器:Dual‑core Arm® Cortex®‑A53 MPCore™,最高 1.3 GHz;

实时处理器:Dual‑core Arm® Cortex®‑R5F MPCore™,最高 533 MHz;

缓存与安全:每核配备 L1/L2 缓存,支持 CoreSight™ 调试与跟踪;

外设接口:原生支持 DDR4/LPDDR4/DDR3/LPDDR3 存储器接口、PCIe® Gen2、USB 3.0、SATA 3.1、DisplayPort™、千兆以太网、CANbus、SPI、I²C、UART/USART 等

可编程逻辑 (PL) 资源

系统逻辑单元:约 192 K Logic Cells;

DSP 切片:728 个 DSP48E1,用于高吞吐量滤波、FFT 与 AI 加速,峰值可达数万亿次乘加运算;

片上存储:总计 20.6 Mb(包含 Block RAM、UltraRAM 与分布式 RAM),满足大规模数据缓存需求;

分布式 RAM:LUT 可配置为低延迟小容量存储或移位寄存器

高速串行收发器与 I/O

串行收发器:16 条 16.3 Gb/s GTH 通道,支持 PCIe、100 GbE、CPRI、DisplayPort、Aurora 等协议;

用户 I/O:252 条可编程引脚,支持 LVTTL、LVCMOS(1.2–3.3 V)、SSTL‑2/‑3、HSTL 等标准,通过 SelectIO™ 实现混合电压与可编程终端电阻;

I/O 带宽:总 I/O 带宽可达数 Tb/s,满足高速数据传输需求

制造工艺与封装

工艺节点:TSMC 16 nm FinFET+,相比 28 nm 代工功耗降低 2–5 倍,信号完整性与性能大幅提升;

封装形式:784‑ball FCBGA(23 × 23 mm,1.0 mm 球间距),提供优异的热性能与可靠性;

功耗优化:多电源域设计与深度睡眠模式(最低 180 nW),适合能耗敏感系统

时钟管理与时序

时钟管理:PL 部分内置 MMCM 和 PLL,可实现倍频、分频、相位对齐及抖动清除;

全局时钟网络:多条低偏斜全局时钟线,支持多时钟域设计;

性能:PL 逻辑频率可达 500 MHz 以上,满足高性能计算与数据流处理需求

配置方式与安全

配置模式:Master/Slave SPI、SelectMAP 并行 (x8/16/32)、JTAG、MultiBoot;

安全特性:支持 AES‑256 位流加密与 CRC 校验,保护 IP 安全并支持远程升级;

动态重配置:可通过 ICAP/DRP 实现部分重配置与多启动管理,提升系统灵活性