一个电平转换电路导致MCU/FPGA通讯波形失真的原因分析

文章目录

- 前言

- 一、问题描述

- 二、原因分析

- 三、 仿真分析

- 四、 尝试的解决方案

- 总结

前言

一、问题描述

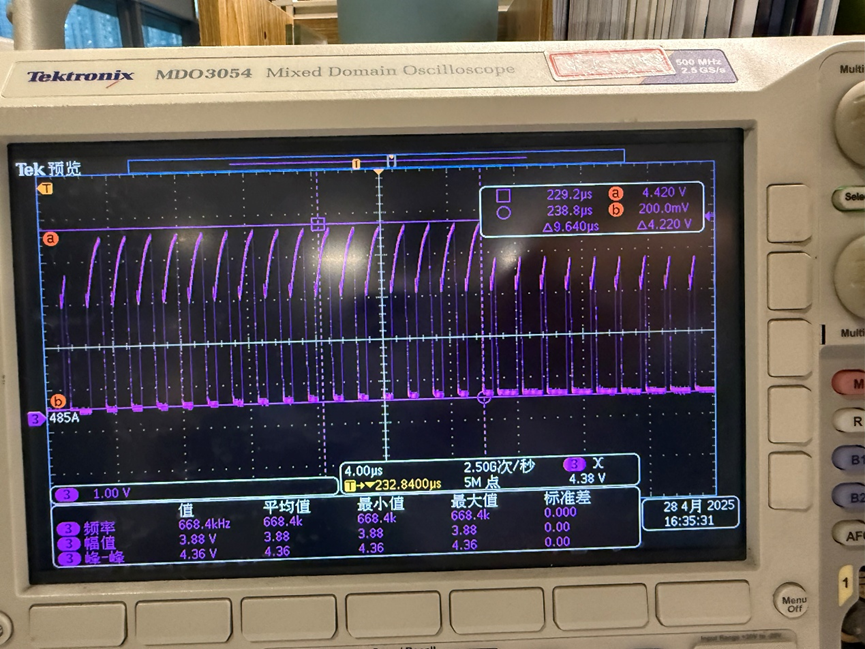

一个电平转换电路,800kHz的通讯速率上不去,波形失真,需要分析具体原因。输出波形如下,1码(占空比75%)低于5V,0码(占空比25%)低于4V。,严重失真。

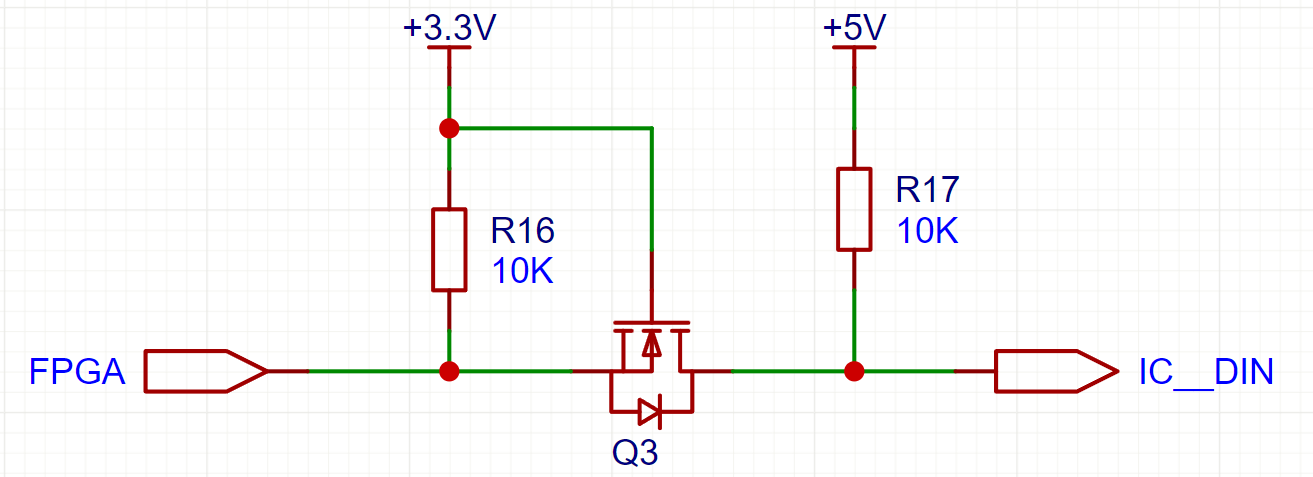

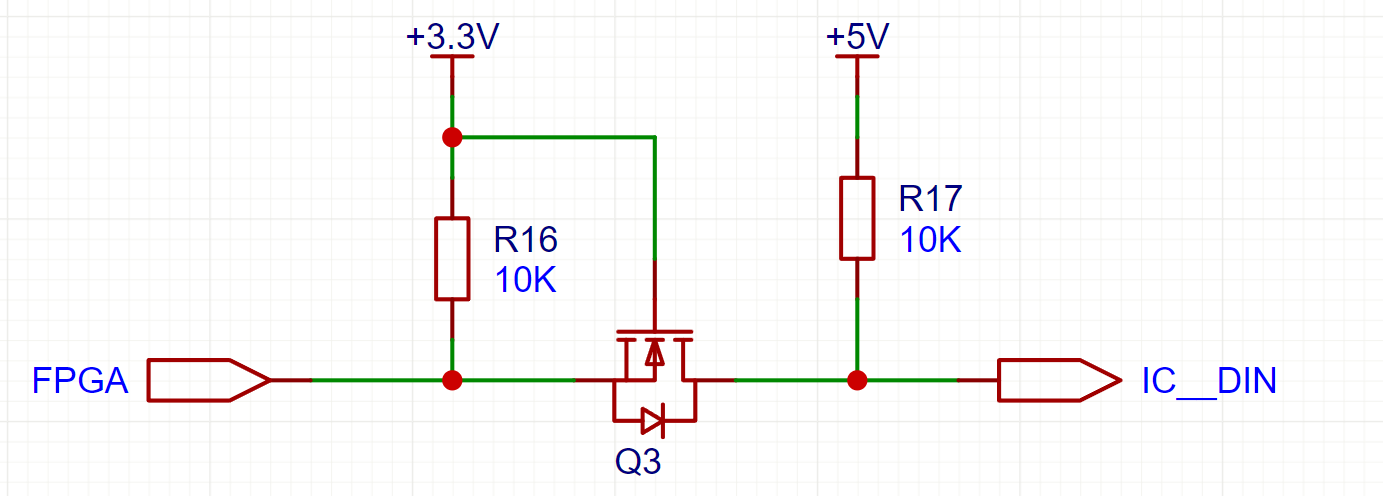

电平转换电路很简单,MOS管采用的是NMOS

对于单向的转换,有两种情况

1、 当FPGA输出高电平3.3V时:MOS管的Vgs = 0,MOS管关闭,IC_DIN被电阻R17上拉到5V。

2、当FPGA输出低电平时:MOS管的Vgs = 3.3V,大于导通电压VGS(th)=1.8V,MOS管导通,IC_DIN通过MOS管被拉到低电平。

二、原因分析

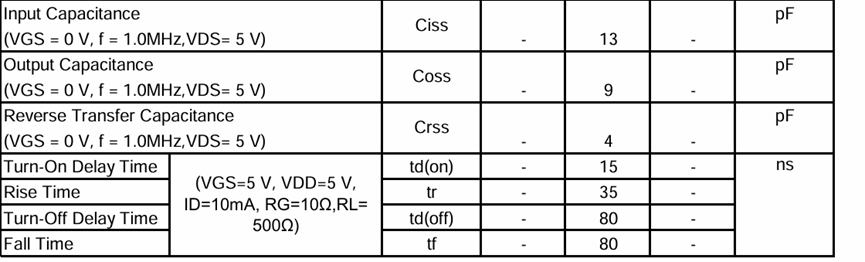

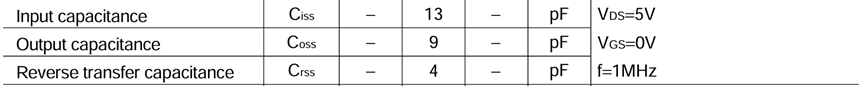

怀疑是MOS管的问题。根据提供的MOS管资料,查到如下寄生电容参数

规格书中最大的输入电容才13pF,可以说是相当优秀了,但实际真的能达到吗?

型号1的寄生参数

型号2的寄生参数

MOS管寄生参数

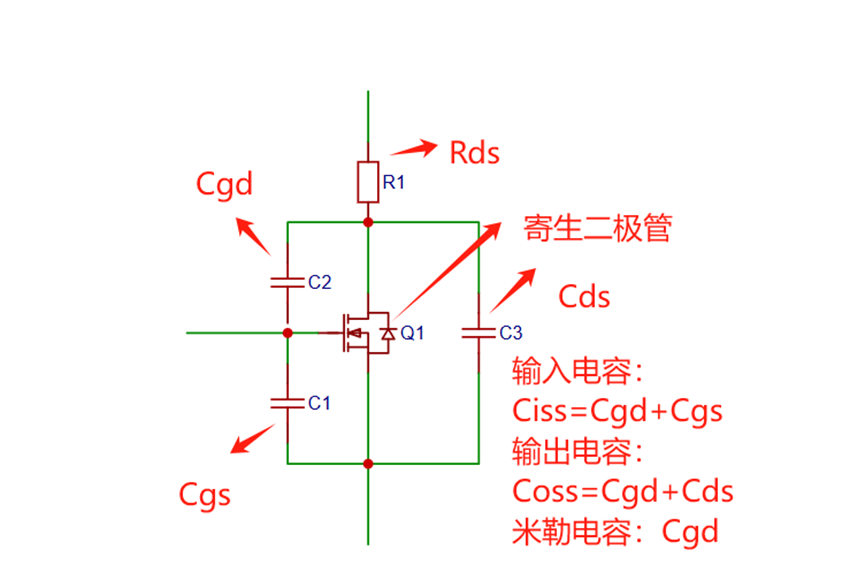

MOS管的这三个电容参数分别对应不同极间电容,其定义和应用如下:

1. 输入电容&