【DC】buffer详解

最近在跑综合,发现DC在一些扇出(fanout)较大的信号后插了不少buffer,对此我有些疑惑,为何插入buffer就能增强驱动能力?所以收集了一些资料,记录一下相关知识点。

什么是buffer?

buffer是一种常见的器件缓冲器,这种器件不仅在时钟树上,在数据路径上也有着大量的应用。

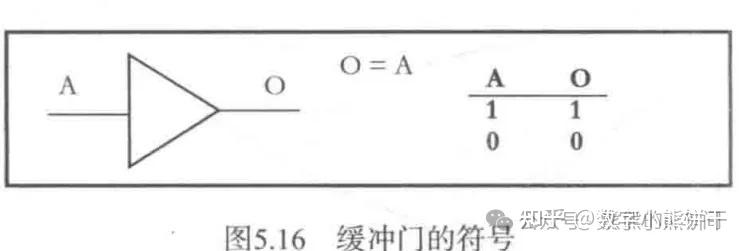

buffer的结构一般是偶数个反相器的级联或者是类似结构的电路,buffer的一个特点是其输出的信号和输入的信号是相同的,不会改变逻辑值。如下面的真值表所示:

buffer的功能

既然buffer不会改变信号的逻辑值,那么其作用到底是什么呢?事实上buffer的功能主要有以下两点:

- 提高驱动能力。

- 优化时序。

这里的驱动能力指的是:前级电路的输出信号可以在规定时间内被后级电路有效响应。

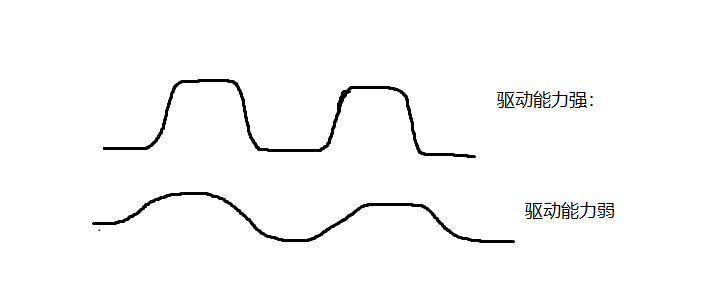

如果电路的负载过大,将导致其输出电流不够,输出信号上下边沿不够陡峭。

而在插入buffer后,由于buffer的驱动能力比较强,最终输出的信号会是上面那种。这种信号的边沿陡峭程度可由转换时间(transition time)进行定量描述,信号的转换时间越短,代表着该单元内部电路的驱动能力越强,延时就越短。

buffer的应用

由于buffer的种种特性,在芯片中的时钟树以及各种路径上有着非常重要的应用。

buffer在时钟树上的应用

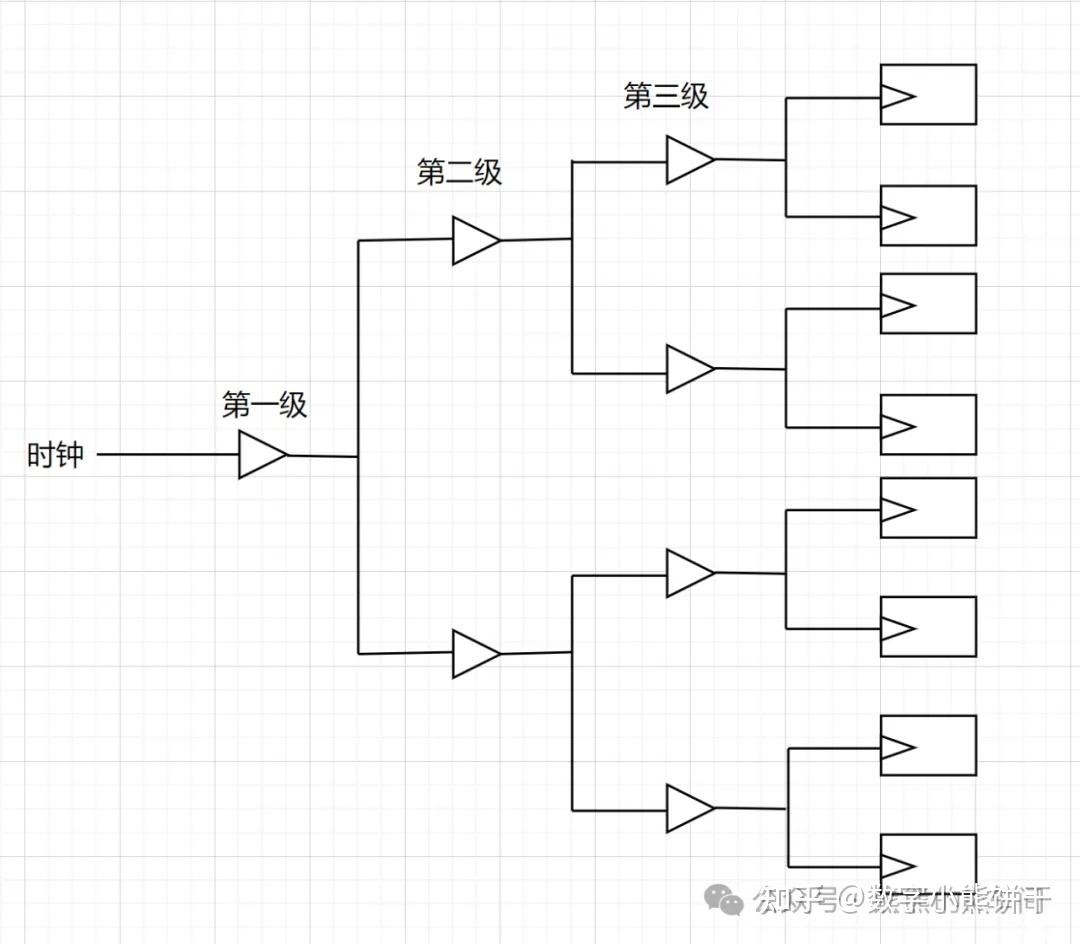

在芯片中,时钟源输出的时钟信号需要驱动大量的寄存器,单独依靠时钟源的信号驱动能力明显是不够支撑其如此之大的扇出。因此,正确的做法是添加大量时钟buffer,由这些buffer一级一级串行级联下去组成时钟树,每一个分结点就化分成一级新的分支,如下图所示:

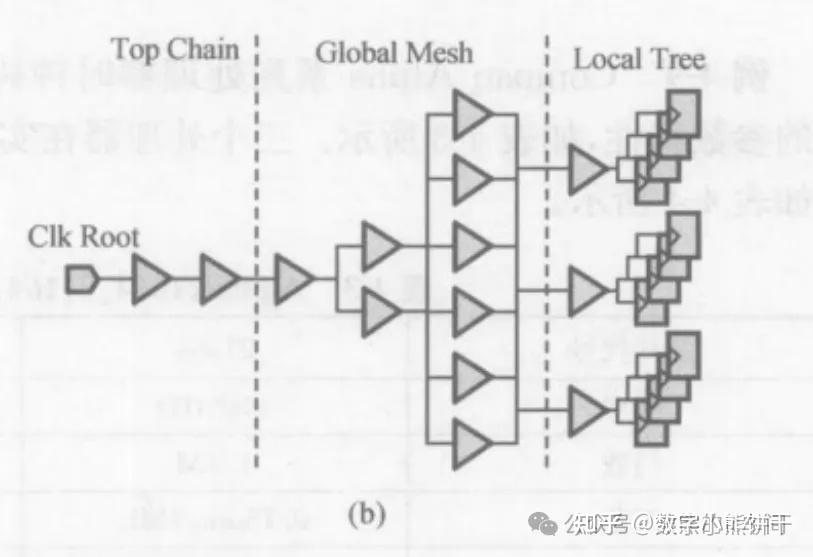

在组成了时钟树后,时钟直接驱动buffer,由buffer驱动后面的寄存器,这就相当于通过插入buffer减少了时钟树各个分支的负载数量,因此各个时钟树分支的驱动能力就会比较强,从而使得时钟的的传播延迟和时钟的转换时间变得比较小。下图展示了一种时钟树的例子,该时钟树分为3节结构:

- 第一节是从时钟的根节点(clock root)后的一长串缓冲器链组成;

- 第二节是时钟网格(global clock mesh),这种时钟网格最显著的特点是使用多个缓冲器进行驱动;

- 第三节是连接各个触发器的局部时钟树。

由于时钟的根节点到达每个寄存器的时钟端的路径不同,因此到达的时间也会不同,即存在时钟偏移(clock skew)。根据建立时间和保持时间裕量的计算方式:

- Tsetupslack=Tclk+Tskew-Tco-Tcomb-Tsu>=0

- Tholdslack=Tco+Tcomb-Tskew-Thd>=0

从上面的公式可以看出:

- 对于建立时间来说,时钟偏移越大越有利满足建立时间(即时钟到达目标触发器的时间与源触发器之间的时间差越大越好);

- 对于保持时间来说,时钟偏移越少,越有利于满足保持时间(即时钟到达目标触发器的时间与源触发器之间的时间差越小越好)。

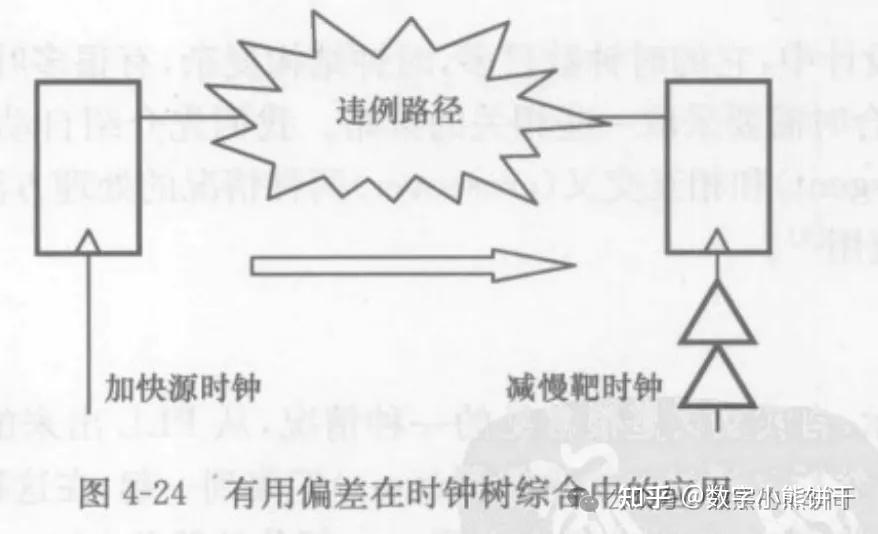

因此,我们可以利用buffer来对时钟偏移加以控制,使其处于一个能够满足建立时间和保持时间的合理值。比如在下图的例子中,由于组合逻辑的延时过大,而导致了建立时间违例,因此我们可以通过增加第二个目标触发器的时钟路径延时,使得时钟偏移变大,从而避免时序违例:

大家观察上图可以发现,在图中的第二个触发器的时钟端是通过加buffer来增加延迟的,这似乎是与我们之前说的加入buffer可以增加驱动能力以及优化时序相矛盾,实际上,buffer本身便有延时,如果插入buffer前的路径上的驱动能力已经足够强,信号的转换时间也比较小,那么再插入buffer也起不到优化的作用,反而会带来更多的延时,上图中就是利用buffer的这种特性来增大时钟偏移的。

buffer在数据路径的应用

在芯片内部,触发器之间通过导线连接,通常来说导线的延迟是和其长度的平方成正比,如果某条路径很长的话,那么导线本身的负载电容就不容忽视,会导致很大的延时。

这种情况下,可以等间距插入N个buffer,原本的路径分为N+1段,其中每一段buffer驱动的负载电容较少,在给定相同的电压时,由于电路的负载电容减少,自然对电容的充电速度变得更快了,这就使得信号的上升沿变得更加陡峭;同理,当电容放电时,由于负载电容变少,因此放电的速度也会变快,这也就使得信号的下降沿也变得更加陡峭。

因此由于信号的转换时间变小,路径的延迟也随着变小。所以即使buffer本身也会带来延时,但是插buffer减少的延时大于buffer自身带来的延时,仍然可以实现对时序的优化。

问题汇总

- 问题1:在时序路径中插入buffer到底是减缓了数据传输呢还是加快了呢?(在时钟树综合过程中,会在clock root pin和cells’ clk pin之间插入buffer产生延时,以求最小的skew;然而,我们又知道在时序路径中“断点插buffer”,目的是加快该路径上的信号传输速度。)

- 解答:如果这个地方有transition 比较大,插buff会改善transition,加入buffer本身所带来的delay远远小于插入这个buffer所减小的delay,所以delay 变小;如果插之前之后都不存在transition问题,加入buffer本身所带来的delay远远大于插入这个buffer所减小的delay的时候,那么就是增加delay。

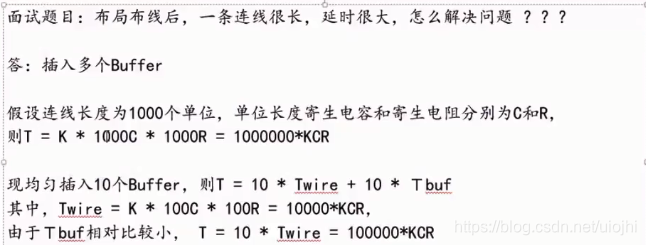

- 问题2:数学计算说明transition较大,插入buffer如何减小延时?

参考资料

https://zhuanlan.zhihu.com/p/699931719

基本知识储备概述-Design Compiler(一)_dc 中的buffer结构-CSDN博客

为什么插入buffer能够增加驱动能力?_时钟buffer原理-CSDN博客