【读文献】Buffer和level shift的偏置电压设计

[1] J. Heel, et al., “A 12.8-GS/s Time-Interleaved Sub-Sampling ADC Front End With 38-GHz Input Bandwidth and >39-dB SNDR for 1–32 GHz in 22-nm FDSOI,” IEEE Journal of Solid-State Circuits, 2025.

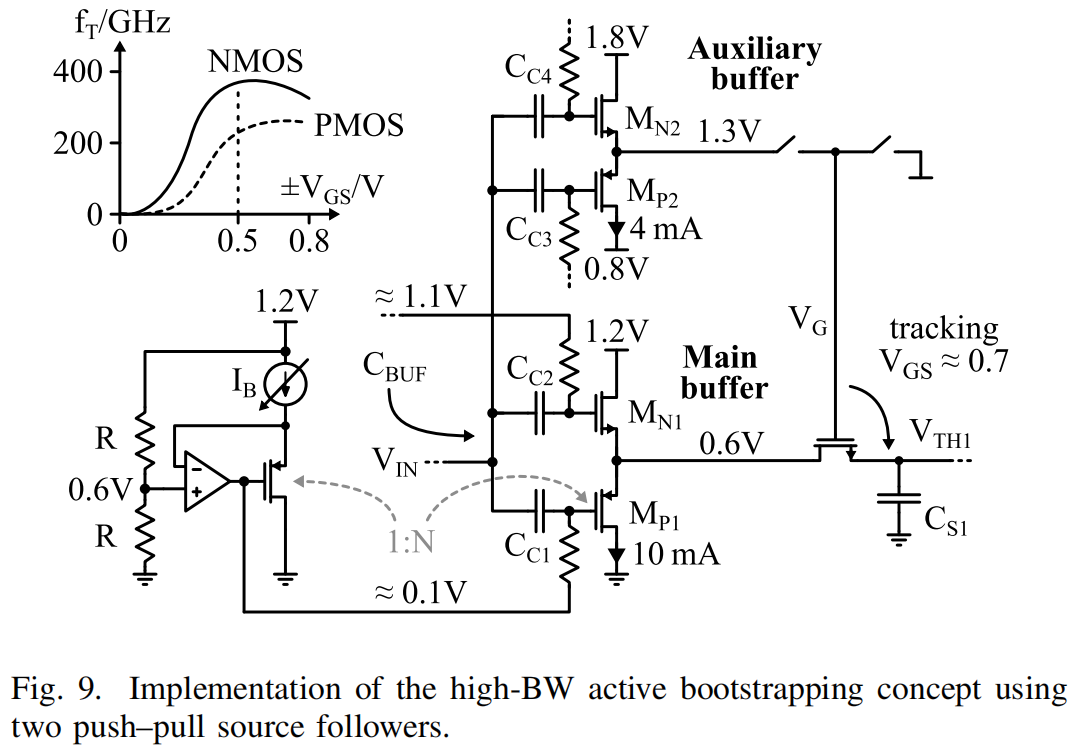

一篇用Buffer和level shift实现栅压自举开关的文章。在设计buffer的时候是这样取值的:

主缓冲器连接0 V和1.2 V电源轨,VTH1的直流偏置为0.5 V(典型值),信号摆幅 ±200 mV(单端)。

辅助缓冲器连接0.8 V和1.8 V电源轨。VG的直流偏置为1.2 V(0.8V + 0.4V),信号摆幅与主缓冲器同步。

电源域差异(1.8V vs 1.2V)天然产生0.6 V 电位差,叠加器件偏置设计,最终使 VG比 VTH1高 0.7 V(满足 NMOS 开关 VGS需求)。

Q:这两个buffer的电源轨电压和Vth、Vg的直流偏置是怎么确定的,怎么算出来的?

A:22nm FDSOI工艺下的设计约束:包括器件工作点优化(fT峰值)、电压裕度分配(可靠性)、功耗平衡等。

以下是针对主缓冲器(Main Buffer)和辅助缓冲器(Auxiliary Buffer)的电源轨电压、直流偏置设计原理的详细解析,结合工艺约束、性能目标及电路仿真进行说明:

一、设计目标与约束

- 带宽要求:>35 GHz(目标38 GHz)

- 线性度要求:HD3 < -50 dB(30 GHz输入)

- 工艺特性:22nm FDSOI的超低阈值电压(SLVT)器件,最优 fTf_TfT在 VGS≈0.5 VV_{GS} \approx 0.5 \, \text{V}VGS≈0.5V 附近

- 可靠性限制:VDS≤0.8 VV_{DS} \leq 0.8 \, \text{V}VDS≤0.8V,VGS≤0.7 VV_{GS} \leq 0.7 \, \text{V}VGS≤0.7V(避免栅氧击穿)

二、主缓冲器(Main Buffer)设计

1. 电源轨电压:0 V / 1.2 V

- 推导逻辑:

- SLVT器件在 VGS=0.5 VV_{GS} = 0.5 \, \text{V}VGS=0.5V 时 fTf_TfT 最高 → 需留出 VGSV_{GS}VGS 空间。

- 输入摆幅:400 mVPP,SE(单端) → 瞬时 VGSV_{GS}VGS 波动 ±200 mV。

- 裕度计算:

- 最小 VGS=0.5−0.2=0.3 VV_{GS} = 0.5 - 0.2 = 0.3 \, \text{V}VGS=0.5−0.2=0.3V(保证导通);

- 最大 VGS=0.5+0.2=0.7 VV_{GS} = 0.5 + 0.2 = 0.7 \, \text{V}VGS=0.5+0.2=0.7V(符合可靠性)。

- 输出电平 VTH1≈0.5 VV_{TH1} \approx 0.5 \, \text{V}VTH1≈0.5V:源极跟随器输出比输入低 ∣VGS∣|V_{GS}|∣VGS∣,需直流偏置补偿。

2. 偏置点验证

- 当输入 VIN=0 VV_{IN} = 0 \, \text{V}VIN=0V(共模)时:

- MN1M_{N1}MN1 的 VGS≈0.5 VV_{GS} \approx 0.5 \, \text{V}VGS≈0.5V,VDS≈0.5 VV_{DS} \approx 0.5 \, \text{V}VDS≈0.5V(1.2V供电下);

- MP1M_{P1}MP1 的 ∣VGS∣≈0.5 V|V_{GS}| \approx 0.5 \, \text{V}∣VGS∣≈0.5V,∣VDS∣≈0.5 V|V_{DS}| \approx 0.5 \, \text{V}∣VDS∣≈0.5V。

- 结果:所有器件 VDS≤0.8 VV_{DS} \leq 0.8 \, \text{V}VDS≤0.8V,满足可靠性(图12c)。

三、辅助缓冲器(Auxiliary Buffer)设计

1. 电源轨电压:0.8 V / 1.8 V

- 电平移位需求:采样开关 MN3/MN4M_{N3}/M_{N4}MN3/MN4 需 VG−VTH1≈0.7 VV_G - V_{TH1} \approx 0.7 \, \text{V}VG−VTH1≈0.7V(恒定 VGSV_{GS}VGS)。

- 实现原理:

- 主缓冲器输出 VTH1V_{TH1}VTH1 偏置 0.5 V;

- 辅助缓冲器输出 VGV_GVG 需偏置 0.5 + 0.7 = 1.2 V。

- 电源域选择:

- 若用 0–1.2V域:输出最大仅1.2V,无法覆盖1.2V偏置+摆幅;

- 0.8–1.8V域:输出范围 0.8–1.8V → 中心点 1.3V(接近1.2V目标)。

2. 偏置点优化

- 直流偏置 VG≈1.2 VV_G \approx 1.2 \, \text{V}VG≈1.2V:

- 通过电阻分压或电流源设定 MN2/MP2M_{N2}/M_{P2}MN2/MP2 栅极电压,使静态 VG=1.2 VV_G = 1.2 \, \text{V}VG=1.2V。

- 裕度验证:

- 输入摆幅同步主缓冲器(±200 mV)→ VGV_GVG 波动范围 1.0–1.4 V;

- MN2/MP2M_{N2}/M_{P2}MN2/MP2 的 VDSV_{DS}VDS:

- MN2M_{N2}MN2:最大 VDS=1.8−1.0=0.8 VV_{DS} = 1.8 - 1.0 = 0.8 \, \text{V}VDS=1.8−1.0=0.8V;

- MP2M_{P2}MP2:最大 ∣VDS∣=1.4−0.8=0.6 V|V_{DS}| = 1.4 - 0.8 = 0.6 \, \text{V}∣VDS∣=1.4−0.8=0.6V → 均安全。

Q:Vin输入buffer能不能满摆幅输入呢?

四、关键设计权衡

-

电源域分离的代价

- 优势:省去专用电平移位器,减少寄生电容(带宽↑)。

- 代价:需额外 0.8V/1.8V 电源轨(增加供电复杂度)。

-

耦合电容 CCC_CCC 的作用

- 值设定:在带宽(寄生↓)与信号衰减(0.4 dB)间权衡(图10)。

- 仿真依据:AC分析显示 CC=60 fFC_C = 60 \, \text{fF}CC=60fF 时路径匹配最优(图11)。

-

功耗分配

- 主缓冲器:10 mA × 1.2 V = 12 mW(驱动大电容 CS1C_{S1}CS1);

- 辅助缓冲器:4 mA × (1.8–0.8 V) = 4 mW(负载较轻)。