分频电路设计

文章目录

- 偶分频

- 1. D触发器级联, 支持2,4,8。。分频

- 2. 计数器

- 奇分频

- 1. 占空比非50%的奇数分频

- 用Moore状态机实现

- 用计数器实现

- 2. 占空比50%的奇数分频

- 3. 利用基本逻辑单元直接搭建占空比为50%的奇数分频电路

- 小数分频

- 总结

- 文章来源

偶分频

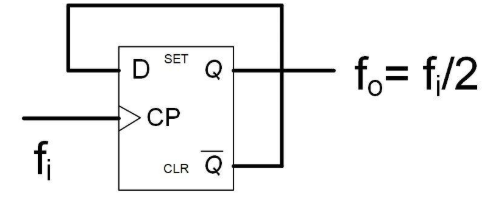

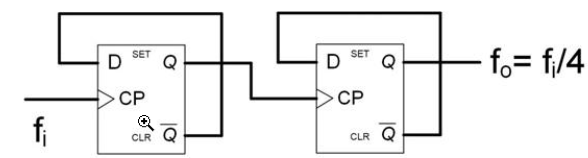

1. D触发器级联, 支持2,4,8。。分频

将主时钟以2为幂次进行分割可以得到同步偶数分频时钟,即21,22,23…分频。电路上可采用D触发器实现,n个触发器可以构成2n次偶数分频。如图1所示,为2分频、4分频电路设计及波形。

2. 计数器

用D触发器级联搭建分频电路只能实现2,4,8,16等分频,对于一般的偶数分频,可以通过计数器实现:若要实现N分频(N为偶数),只需将计数器在待分频时钟上升沿触发下循环计数,从0计数到(N/2 -1)后将输出时钟翻转即可实现

奇分频

1. 占空比非50%的奇数分频

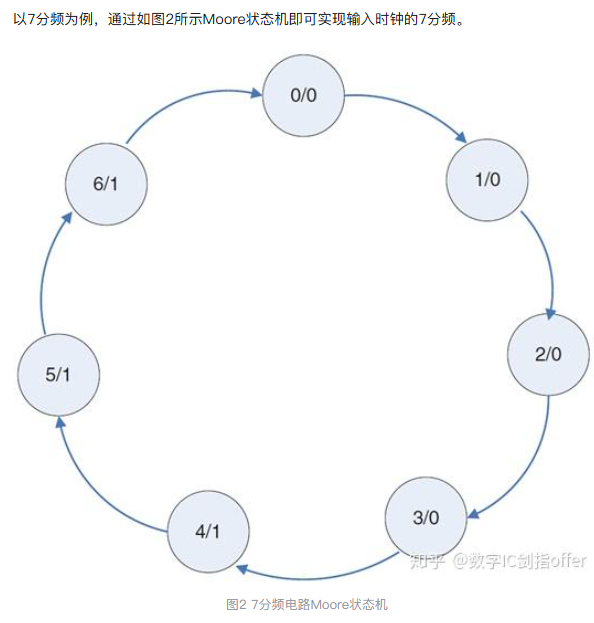

用Moore状态机实现

//N分频器,N为奇数,奇数分频,占空比非50%

module Odd_Freq_Div_N ( input clk_in,input rst_n,output clk_out);parameter State_0 = 3'b000;

parameter State_1 = 3'b001;

parameter State_2 = 3'b010;

parameter State_3 = 3'b011;

parameter State_4 = 3'b100;

parameter State_5 = 3'b101;

parameter State_6 = 3'b110;reg [2:0] CS,NS;always @(posedge clk_in or negedge rst_n)

beginif(!rst_n)CS <= State_0;elseCS <= NS;

endalways @(*)

beginif(!rstn)NS = State_0;elsebegincase(CS)State_0: NS = State_1;State_1: NS = State_2;State_2: NS = State_3;State_3: NS = State_4;State_4: NS = State_5;State_5: NS = State_6;State_6: NS = State_0;default: NS = State_0;endcaseend

endalways @(posedge clk_in or negedge rst_n)

beginif(!rst_n)clk_out <= 1'b0;elsebegincase(NS)State_0: clk_out <= 1'b0;State_1: clk_out <= 1'b0;State_2: clk_out <= 1'b0;State_3: clk_out <= 1'b0;State_4: clk_out <= 1'b1;State_5: clk_out <= 1'b1;State_6: clk_out <= 1'b1;default: clk_out <= 1'b0;endcaseend

endendmodule

用计数器实现

其实用状态机实现占空比非50%的分频电路还是比较麻烦的,可以采用计数器的方法:若要实现N分频(N为奇数),只需将计数器在待分频时钟上升沿触发下循环计数,从0计数到(N-1)后计数器清零。当计数到(N-1)/2后将输出时钟翻转,计数到0后再次翻转即可实现。7分频的Verilog代码如下:

//N分频器,N为奇数,奇数分频,占空比非50%

module Odd_Freq_Div_N ( input clk_in,input rst_n,output clk_out);parameter N = 7;reg [2:0] cnt_p;

reg clk_p;always @(posedge clk_in or negedge rst_n)

beginif(!rst_n)cnt_p <= 3'b000;else if (cnt_p == N-1)cnt_p <= 3'b000;elsecnt_p <= cnt_p + 1'b1;

endalways @(posedge clk_in or negedge rst_n)

beginif(!rst_n)clk_p <= 1'b0;else if (cnt_p == (N-1)/2)clk_p <= ~clk_p;else if (cnt_p <= 3'b000)clk_p <= ~clk_p;elseclk_p <= clk_p;

endendmodule

不管是用状态机实现,还是用计数器实现,本质上都是控制输出时钟在每N个待分频时钟周期内完成一次周期性输出。

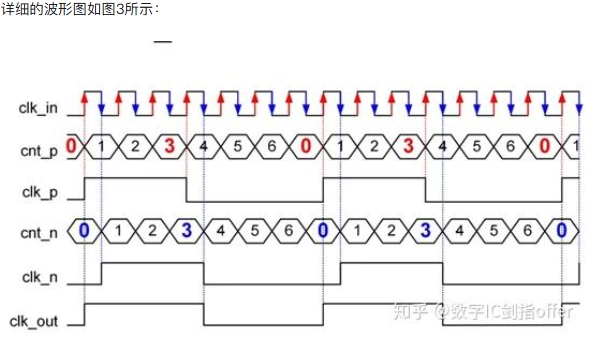

2. 占空比50%的奇数分频

分别利用待分频时钟的上升沿触发生成一个时钟,然后用下降沿触发生成另一个时钟,然后将两个时钟信号进行或/与运算得到占空比为50%的奇数分频。

① 设计2个分别用上升、下降沿触发的计数器

② 利用上升、下降沿计数器生成两个分频时钟clk_p和clk_n(依然在0,(N-1)/2翻转)

③ 利用clk_p和clk_n通过逻辑运算生成占空比为50%的分频时钟

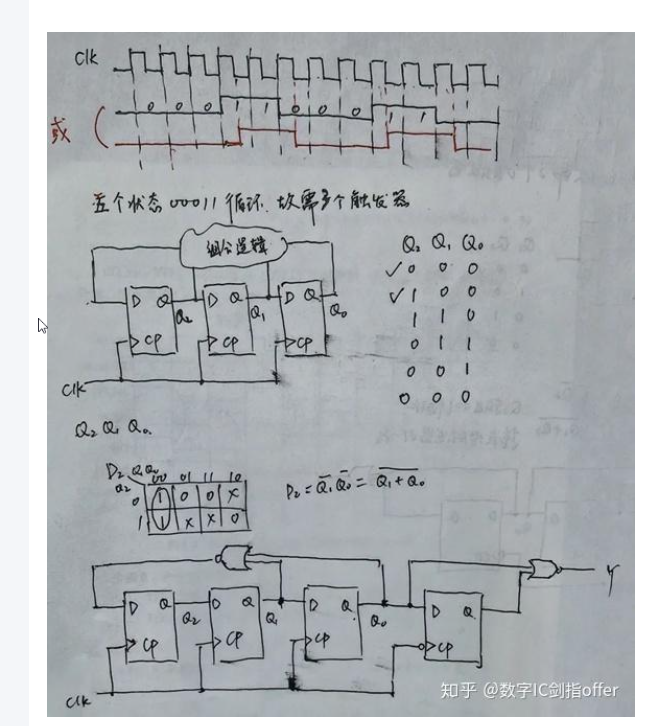

3. 利用基本逻辑单元直接搭建占空比为50%的奇数分频电路

首先思考如何用D触发器和组合逻辑实现占空比为50%的三分频电路?

思路:先使用触发器构成序列生成器,输出001循环脉冲,实现占空比非50%的三分频,然后用负沿触发器打一拍,再相或。由于001循环共三个状态,故需2个D触发器。通过列状态表、画卡诺图,得到由两个D触发器及逻辑门构成的001序列生成器,后接负沿触发器打一拍并将其输出与序列生成器的输出相或,即得到占空比为50%的三分频电路。

小数分频

小数分频电路可以转化为特定分频比电路设计问题。如19/9分频,意味着在输入时钟clk_in的19个周期内,输出需产生9个脉冲。因为19/9 = 2.11…, 因此可以用2分频和3分频配合实现,设待分频时钟的19个周期内共有x个二分频时钟周期,y个三分频时钟周期,则有:

x+y=9

2x+3y=19

解得x=8,y=1。即只要在待分频时钟的19个周期内控制输出8个二分频时钟周期和1个三分频时钟周期即可。具体代码思路:

1)首先一个总的计数器,在0-18循环;

2)其次设计两个分别生成2分频和3分频的计数器,根据总计数器的数值范围分别在0-1和0-2循环;

3)最后是波形生成逻辑,根据总计数器和2、3分频计数器的数值控制输出脉冲翻转生成期望分频比的时钟。

// M/N小数分频,M为分子,N为分母

module Dec_Freq_Div_M_N(input clk,input rstn,output clk_out

);reg [5:0] cnt;

reg [3:0] cnt_a;

reg [3:0] cnt_b;

reg clk_out_reg;

assign clk_out = clk_out_reg;// div_a和div_b分别为根据前述公式计算出来的基准分频系数

// change为2、3分频时钟的切换点

parameter M = 6'd19;

parameter change = 6'd16;

parameter div_a = 5'd2;

parameter div_b = 5'd3;//总计数器

always @(posedge clk or negedge rstn) beginif(!rstn)cnt <= 6'b0;else beginif(cnt == M - 1'b1)cnt <= 6'b0;elsecnt <= cnt + 1'b1;end

end //产生2、3分频的计数器

always @(posedge clk or negedge rstn) begin if(!rstn) begincnt_a <= 4'b0;cnt_b <= 4'b0;end else if(cnt<=change-1'b1) begincnt_b <= 4'd0;if(cnt_a == div_a - 1'b1)cnt_a <= 4'd0;elsecnt_a <= cnt_a + 1'b1;end else if(cnt>change-1'b1) begincnt_a <= 4'd0;if(cnt_b == div_b - 1'b1)cnt_b <= 4'd0;elsecnt_b <= cnt_b + 1'b1;end//输出时钟产生逻辑

always @(posedge clk or negedge rstn) beginif(!rstn)clk_out_reg <= 1'b0;else if(cnt<change) beginif(cnt_a == 4'd0 || cnt_a == div_a/2)clk_out_reg <= ~clk_out_reg;elseclk_out_reg <= clk_out_reg;end else if(cnt>=change) beginif(cnt_b == 4'd0 || cnt_b == (div_b - 1'b1)/2)clk_out_reg <= ~clk_out_reg;elseclk_out_reg <= clk_out_reg;end

end endmodule

总结

- 时序电路设计通用方法

- 也可以使用序列生成器的同样设计方法, 一个移位寄存器和一个各触发器反馈构成的反馈电路, 列出反馈真值表就可以设计D0

- 对于计数器分频方法的理解,对于N分频, 那么计数器从0记到N-1, 一个计数循环是时钟周期的N倍,这就是N分频信号的周期, 接下来我们做的是划分占空比, 最简单的就是在计数器中间翻转一次, 对于偶分频,在(N/2-1)翻转, 刚好50占空比; 对于奇分频,N为奇数, 因此在(N-1)/2翻转,而且必须额外翻转一次, 选择在读0时翻转即可

文章来源

常用电路设计——“分频电路” - 数字IC剑指offer的文章 - 知乎

https://zhuanlan.zhihu.com/p/295000552