AMBA-AHB总线的基本操作和基本传输类型

总线操作概述

一般来说在AMBA AHB总线协议中,请求总线使用权的实体是AHB总线上的主设备Master,而非其他系统总线(如APB或ASB)。

(1)请求与仲裁机制

-

请求主体:

AHB总线上的主设备(如CPU、DMA控制器等)通过HBUSREQx信号向仲裁器(Arbiter)发起总线访问请求。例如,CPU需要读写内存时,会主动向仲裁器发送请求信号。 -

仲裁逻辑:

仲裁器根据优先级算法(如固定优先级或循环优先级)决定授权哪个主设备使用总线,并通过HGRANTx信号通知主设备。AHB协议规定,同一时刻仅允许一个主设备占用总线。

(2)总线层级与交互

-

AHB总线作为单一系统总线:

AHB总线本身是系统内的高性能主干总线,负责连接主设备、从设备及仲裁器。主设备直接通过AHB总线向仲裁器发送请求,无需经过其他总线(如APB或ASB)。 -

其他总线的角色:

例如APB总线用于低速外设,需通过AHB-APB桥与AHB总线连接,但桥接器本身作为AHB从设备存在,不参与总线仲裁请求。

一个典型场景示例:主设备竞争总线

当多个主设备(如CPU和DMA)同时请求总线时,仲裁器通过采样HBUSREQx信号,优先授权高优先级主设备。例如,DMA突发传输可能打断CPU的普通读写,但若CPU使用HLOCKx信号锁定总线,仲裁器会维持其控制权直至传输完成。

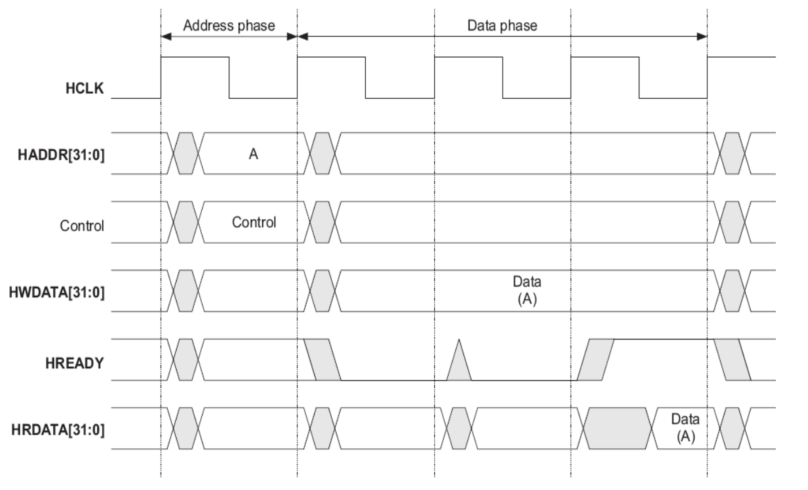

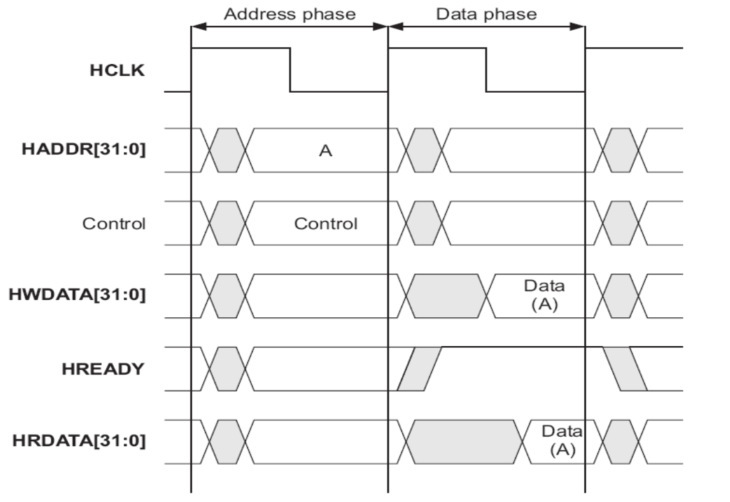

基本传输

由上述可以知道一笔传输由如下两部分组成: 地址段,一个周期; 数据段,一个或多个周期,可以由 HREADY 发出请求延长一个周期。

简单例子

对AHB总线流水线特征的理解

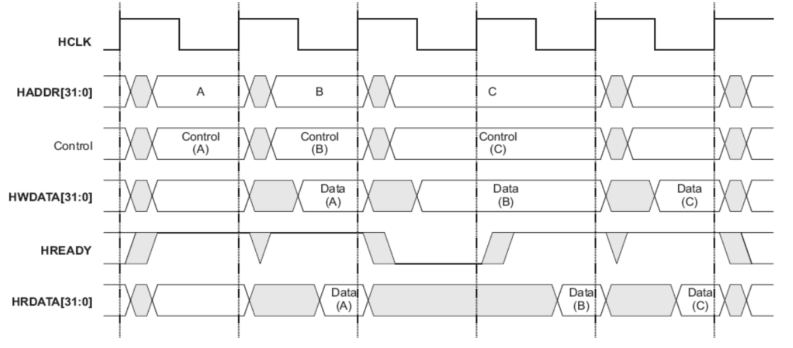

在AHB总线协议中,流水线特征通过地址段与数据段的时间交叠实现高吞吐量和时序优化,其核心原理是隐藏延迟并利用总线空闲时段。以下从技术原理、典型场景和实例分析三个角度展开说明:

(1)流水线化的时序交叠

AHB总线的传输分为两个阶段(地址段+数据段),每个阶段占用至少1个时钟周期。通过将当前传输的数据段与下一传输的地址段在时间上重叠,形成类似工厂装配线的流水线结构。例如:

- 周期1:Master发出地址A(地址段开始)。

- 周期2:Slave采样地址A,Master同时发出地址B(地址段B与数据段A交叠)。

- 周期3:Slave返回数据A,Master接收数据A并处理,同时Slave开始处理地址B的数据段。

(2)隐藏延迟的关键作用

- Slave响应时间优化:Slave在地址段采样后,可利用后续周期处理数据操作(如内存读写),而无需等待当前传输完成。例如,若Slave需要2个周期准备数据,可通过延长数据段(HREADY拉低)隐藏延迟,而总线仍可并行处理下一地址段。

- 总线带宽利用率提升:地址与数据通道独立控制,避免总线空闲。例如,当Master连续发起写操作时,地址1的数据传输(周期3)与地址2的地址传输(周期2)并行进行。

(3)案例:AHB总线连续写操作

假设Master需要向Slave连续写入两个32位数据(Data1和Data2),时序如下:

- 周期1:

- Master驱动地址Addr1和控制信号(写操作)。

- 周期2:

- Slave采样Addr1,启动内部写操作(如存储到缓冲区)。

- 同时,Master驱动下一地址Addr2(流水线交叠)。

- 周期3:

- Slave完成Data1写入,返回HREADY高电平。

- Master在周期3的上升沿采样HREADY,确认Data1写入成功。

- 同时,Slave开始处理Addr2的Data2写入,而Master可能已发起第三个地址Addr3。

(4)效果:

- 传统非流水线总线:3周期完成1次写操作(地址1周期 + 数据1周期 + 响应1周期),带宽为1/3数据/周期。

- 流水线总线:3周期完成2次写操作(地址1+数据1与地址2+数据2交叠),带宽提升至2/3数据/周期。

(5)与非流水线总线的差异

| 特性 | 流水线总线(AHB) | 非流水线总线 |

|---|---|---|

| 时序结构 | 地址与数据段交叠 | 串行处理地址和数据段 |

| 吞吐量 | 高(隐藏Slave延迟) | 低(需等待Slave响应) |

| 适用场景 | 高速、多主设备系统 | 简单、低速设备 |

NOTE:扩展:CPU指令流水线

类似总线流水线,CPU指令流水线将指令执行分为取指、译码、执行等阶段。例如:

- 周期1:取指阶段获取指令A。

- 周期2:译码指令A,同时取指阶段获取指令B。

- 通过阶段交叠,指令吞吐量显著提升。