【集成电路】集成电路导论知识点

西安电子科技大学电子工程学院(西电电院)

- 基本概念—第1、2、3、4、5章。

摩尔定理:

集成电路上可以容纳的晶体管数目大约每经过18个月就会增加一倍,性能也会增加一倍。微处理器性能每隔18个月提高一倍,价格下降一倍。

简述版图设计规则包括了那些内容;

λ设计规则:λ![]() 大小一般是工艺最小尺度的一半,也就是说大部分的尺寸都按照 λ

大小一般是工艺最小尺度的一半,也就是说大部分的尺寸都按照 λ![]() 的整数倍来计。

的整数倍来计。

SCMOS设计规则:美国的MOSIS推出SCMOSLIB标准单元库

3μm绝对单位制规则: 以绝对单位制定规则,以μm为单位,不以λ为单位

特征尺寸:器件中最小线条宽度

微米级(M)—1.0μm以上

亚微米级(SM)—0.6μm左右

深亚微米级(DSM)—0.35μm以下

超深亚微米级(VDSM)—0.18μm以下

- ASIC(专用集成电路);

1.ASIC/SOC设计发展趋势:ASIC/SOC设计正经历 着一个从常规设计向高难度设计发展的过程,其发展趋势为:高密度、高I/O引脚数、小摆幅逻辑、高系统时钟频率、低功耗、先进封装。

2.ASIC设计流程:版图设计、RC/LVS检查、参数的提取LPE、布局后的模拟、用于制造的掩模数据输出、测试

3.ASIC设计工艺:

1.CMOS工艺:能在同一芯片上制作NMOS和PMOS器件的工艺

优点:集成度高,静态功耗低

不足:噪声较大,匹配性不如Bipolar工艺好

应用:适用于大规模集成电路和低功耗设计

2.TTL/ECL工艺:采用双极型工艺制造,具有高速度低功耗和品种多等特点

TTL数字IC:门电路、译码器/驱动器、触发器、计数器、移位寄存器、单稳双稳电路和多谐振荡器、加法器乘法器、奇偶校验器、码制转换器、线驱动器/线接收器、多路开关

ECL电路:主要特点是速度极快(延迟时间仅1ns左右),工作频率很高(几百兆赫至1.5GHz),输出能力强、噪 声低,可广泛用于数字通信、雷达等领域。

缺点:功耗高、噪声容限低, 价格昂贵。

3.BiCMOS工艺:将双极器件的线性和速度与 CMOS的低耗用功率、低热兼容。集优异的线性度、噪声性能和 高度的器件集成特性于一体,能够工作于极宽的频段范围。 2000MHz至3900MHz

4.GaAs工艺:水平布里奇曼法HB、液态密封法LEC、LEP

5.BCD工艺:在同一芯片 上制作双极管bipolar,CMOS和DMOS 器件,称为BCD工艺

4.ASIC设计方法:

全定制ASIC:利用各种EDA工具,从每个半导体器件的图形、尺寸开始设计,直至整个版图的布局、布线等的完成。

半定制ASIC:对一批芯片作“单独处理”,即单独设计和制作接触 孔和连线以完成特定的电路要求。适用于要求设计成本较低、设计周期较短而生产批量比较小的芯片设计。 周期缩短,设计和制造成本下降 。但门阵列的门利用率较低,芯片面积比起全定制设计的芯片要大 。

可编程逻辑器件(PLD):根据布尔理论,即任何的组合逻辑都可以由“与”和“或”来实现。PLD是一种已完成了全部工艺制造的、可以直接从市场上购得的产品,刚购来时它不具有任何逻辑功能,但一经编程就可在该器件上实现设计人员所要求的逻辑功能。降低了设计和制造成本,缩短了设计周期。

现场可编程门阵列(FPGA):利用各种 EDA工具,绘制出实现用户逻辑的电路图或布尔方程,经过编译、自动布局布 线,仿真等,最后生成二进制文件,装入EPROM,对FPGA器件初始化,实现满足用户要求的专用集成电路芯片,真正达到由用户自行设计、研制和生产。

-

- IC(集成电路):

- 氧化:制备SiO2层(SiO2是一种十分理想的电绝缘材料,它的化学性质非常稳定,室温下它只与氢氟酸发生化学反应)

SiO2的主要作用:

MOS电路中作为MOS器件的绝缘栅介质,器件的组成部分

1.扩散时的掩蔽层,离子注入的(有时与光刻胶、Si3N4层一起使用)阻挡层

2.作为集成电路的隔离介质材料

3.作为电容器的绝缘介质材料

4.作为多层金属互连层之间的介质材料

5.作为对器件和电路进行钝化的钝化层材料

SiO2的制备方法

热氧化法

化学气相淀积法(CVD): 通过气态物质的化学反应在衬底上淀积一层薄膜材料的过程

热分解淀积法:在真空系统,中金属原子获得足够的能量后便可以脱离金属表面的束缚成为蒸汽原子,淀积在晶片上。按照能量来源的不同,有灯丝加热蒸发和电子束蒸发两种

溅射法:真空系统中充入惰性气体,在高压电场作用下,气体放电形成的离子被强电场加速,轰击靶材料,使靶原子逸出并被溅射到晶片上

光刻:光刻三要素:光刻胶、掩膜版和光刻机 (通过光化学反应,将光刻板上的图形转移到光刻胶上)

光刻胶又叫光致抗蚀剂,它是由光敏化合物、基体树脂和有机溶剂等混合而成的胶状液体

光刻胶受到特定波长光线的作用后,导致其化学结构发生变化,使光刻胶在某种特定溶液中的溶解特性改变

正胶:分辨率高,在超大规模集成电路工艺中,一般只采用正胶(曝光后可溶)

负胶:分辨率差,适于加工线宽≥3mm的线条(曝光后不可溶)

几种常见的光刻方法:

接触式光刻:分辨率较高,但是容易造成掩 膜版和光刻胶膜的损伤。

接近式曝光:在硅片和掩膜版之间有一个很 小的间隙(10~25mm),可以大大减小掩膜版的 损伤,分辨率较低。

投影式曝光:利用透镜或反射镜将掩膜版上 的图形投影到衬底上的曝光方法,目前用的最多的曝光方式。

扩散:衬底杂质与外延层杂质相互扩散,导致界面处杂质再分布

1. 替位式扩散:杂质离子占据硅原子的位(N\P)

2. 间隙式扩散:杂质离子位于晶格间隙(Na、K、Fe)

淀积:淀积氧化层

-

- 深亚微米集成电路(90nm工艺):

- IC版图格式:

CIF格式: 是用一组文本命令来表示掩模分层和版图图形, 可读性强,具有无二义性的语法。由于采用字符格式,CIF格式可以独立于具体 机器,可移植性强

GDSП格式; GDSⅡ格式可以表示版图的几何图形、拓扑关系和结构、层次以及其它属性。作为一种二进制格式文件,它占用的空间较少,但无法进行编辑,可读性较差。同一设计的GDSⅡ文件比CIF文件长。 GDSⅡ不包括圆的定义,一个圆用64多边形近似。

PG格式

-

- 版图验证与检查:

DRC:设计规则检查:检查版图中各掩膜层图形的各种尺寸是否合乎设计规则的要求。

ERC:电学规则检查

LPE; 版图寄生参数提取

LVS:版图与电路图一致性检查 (LVS)是把从版图中根据对器件与节点识别提取出的电路网表同原设计的电路网表进行对比检查,要求二者的节点与器件皆能一一配对。

-

- PN 结

MOS电容:C=ε0εSio2Asdi (ε0=8.85e-6PFμm εSio2=3.9 As电容器面积 dj SiO2厚度

(ε0=8.85e-6PFμm εSio2=3.9 As电容器面积 dj SiO2厚度 )

)

-

- 方块电阻:结深为Xj

的一个正方形扩散层的薄层电阻R=ρLXjW

的一个正方形扩散层的薄层电阻R=ρLXjW

- 方块电阻:结深为Xj

Xj![]() 扩散区结深(pn结的几何位置与扩散层表面的距离)

扩散区结深(pn结的几何位置与扩散层表面的距离)

ρ![]() 扩散层平均电阻率

扩散层平均电阻率

-

- CMOS噪声容限:

高电平噪声容限:NMH=VOH min-VIH min![]()

低电平噪声容限: NML=VIL max-VOL max![]()

-

- CMOS反向器的功耗:

静态功耗:Ps=ID*VDD=0![]()

动态功耗: 交流开关损耗PD1:当反相器的输入为理想阶跃时,对负载电容CL充 放电所消耗的功耗PD1。PD1=CLfCVOH-VOLVDD=CLfCVDD2![]()

直流开关损耗PD2 Ø 当反相器的输入为非理想阶跃时,在处于输入波上升沿或下降沿的的瞬间,存在 P管和N管同时导通区,由此而引起的功耗称为直流开关功耗。 PD2=12IDMVDDfC(Tr+Tf)

反相器总功耗:P=Ps+PD1+PD2![]()

功耗周期延迟积:PT=CLVDD2![]()

-

- Digital(数字)IC设计过程:

-

-

-

-

- 确定项目需求:指定芯片具体指标

- 系统级设计:用系统建模语言对各个模块进行描述

- 前端设计:RTL设计、RTL仿真、硬件原型验证、电路综合

- 后端设计:版图设计、物理验证、后仿真

-

-

-

-

- Digital(数字)IC设计过程:

Analog IC设计过程(属于全定制设计):

- 电路图编辑

- 电路仿真

- 版图编辑

- 版图验证与后仿真

SOC IC设计过程:包括系统结构设计(也称为架构设计),软件结构设计和ASIC设计(硬件设计)

二、集成电路工艺按制作工艺主要分为哪几大类,并简述各工艺的主要特点及应用范围:

1.双极工艺(主要是TTL):工作速度高,易于做成大规模集成电路,功耗低

2.CMOS工艺:有P阱与N阱两种,N阱的比P阱的CMOS性能好

1.CMOS是场效应管构成,TTL为双极晶体管构成

2.CMOS的逻辑电平范围比较大(5~15V),TTL只能在5V下工作

3.CMOS的高低电平之间相差比较大、抗干扰性强,TTL则相差小,抗干扰能力差

4.CMOS功耗很小,TTL功耗较大(1~5mA/门)

5.CMOS的工作频率较TTL略低,但是高速CMOS速度与TTL差不多相当。

3.深亚微米工艺:面积小、速度高、功耗低

三、画出双极晶体管(NPN、横向PNP及纵向PNP)的剖面图、版图及给出

简化的标准双极工艺流程:

埋层扩散、外延生成、隔离扩散、硼扩散(即基区扩散)、磷扩散(发射区扩散)、刻蚀(铝线的形成过程)、钝化(生长保护膜的过程)

六、选择工艺的主要依据是什么:

集成度和功耗

速度(门传播延迟)

驱动能力

成本造价

有无IP库和设计继承性

七、集成电路中常用的电阻类型及其特点;电容类型;

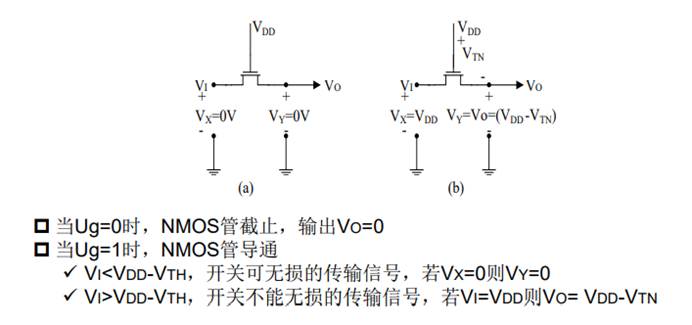

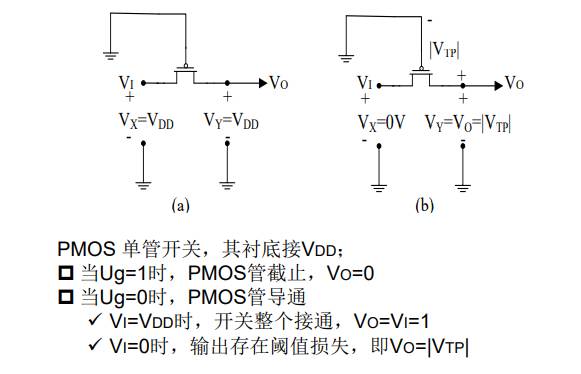

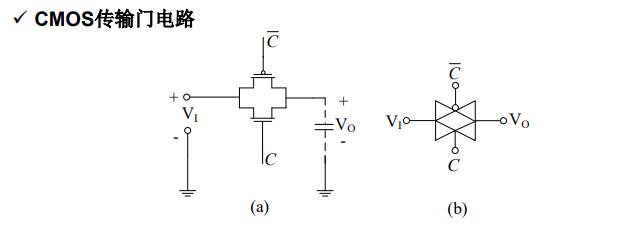

八、单管MOS开关及CMOS传输门的特点;并画出CMOS传输门的电路结构。

CMOS传输门特点:

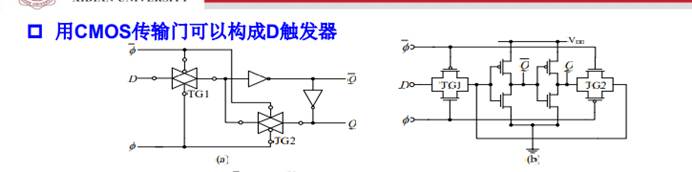

CMOS传输门是由一PMOS和一NMOS相并联而成,所以它可以成功的实现互补的传输关系。当传输高电平时,虽然NMOS开关管传输弱逻辑“1”,PMOS开关管却传输强逻辑“1”;传输低电平时,虽然PMOS开关管传输弱逻辑“0”,但NMOS开关管却能传输强逻辑“0”。 故CMOS传输门可传输整个0-VDD电压范围。消除了仅当采用一个MOS管做开关管时所存在的一个阈值电压逻辑摆幅损失的问题

CMOS传输门电路结构:

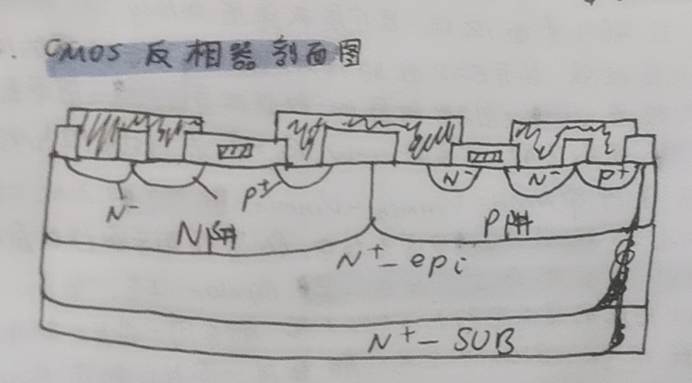

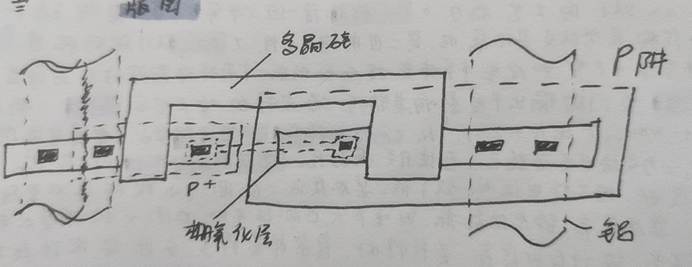

九、画出CMOS反相器的剖面图和版图。

十、用你自己的话解释微电子学、集成电路、ASIC的概念,并列举出你见到的、想到的不同类型的 集成电路及其主要作用

十一、集成电路设计的一般流程

十二、简述反向器的上升时间、下降时间、延迟时间。

上升时间Tr为输出电压Vo从0.1 VDD上升到0.9 VDD所需的时间

下降时间Tf为输出电压Vo从0.9 VDD上升到0.1 VDD所需的时间

延时时间Td为输出电压Vo从0上升到0.5 VDD所需的时间

Tr=2.2RpCL![]()

Tf=2.2RNCL![]()

Td=Tr+Tf4

十三、采用传输门构成D触发器的电路结构

十四、恒流源的电路结构及特点

十五、集成运算放大器电路结构及基本的跨导运算放大器电路

十六 每讲或章节后的思考题

十七、上机作业

必做题目:(1)自己设计一个简单的数字电路,如D触发器或全加器。要求用S-edit画图、Ledit/SPR自动布局布线、T-spice功能仿真。

(2)手工画出CMOS结构Nand2或Nor2版图

选做题目:(1)对一个模拟电路如差分对完成S-edit画图、T-spice功能仿真、Ledit手工画出版图。

(3)必须交上机试验报告(也为一道考题),可以是手写的。包括详细设计过程、电路图、仿真波形示意图及工作原理和结果分析。不需要当场交,各班班长于上机结束后三天内收齐交老师,过期不候。