汽车功能安全--TC3xx MBIST设计要点

英飞凌针对硬件潜伏故障的自测,提供了四种机制:PBIST、LBIST、MONBIST和MBIST。

LBIST和MONBIST我们已经聊过了,今天就快速介绍下MBIST。

MBIST,全程Memory Built-in Self Test,用于检测SRAM数据单元的完整性。

在26262中,SRAM cell出现错误被认为是潜伏故障,而潜伏故障要求至少一个上电周期要完成一次检测,因此MBIST的使用时机就完全取决于使用者,可以是上电检测、也可以是下电检测、甚至可以在程序运行时检测。

虽然时机随心所欲,但是做MBIST的时候还需要考虑两个前置条件:(1)测试前SRAM需要完成初始化,有正确的ECC;(2)SRAM在测试时不允许被访问。

因此,这就引出了今天的话题,如何测试内核相关的memory。

1. 单核和多核

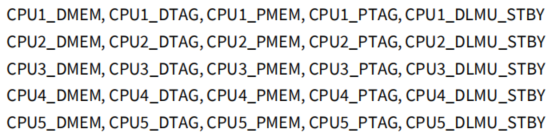

根据芯片手册,TC3xx CPU有如下几类SRAM可供使用:

- P\DSPR:Program\Data Scratch Pad SRAM,类比ARM内核的TCM;

- P\DCACHE:Progaram\Data Cache

- P\DTAG:Cache相关的Tag SRAM

为了提升效率,我们用到的最多肯定就是PSPR、DSPR等,常规用法:PSPR存放性能要求或者是特定场景的函数,DSPR用于堆栈、CSA或者其他自定义等数据存放;但做mbist的时候被测memory又不能被访问,这就要求相关memory的CPU需要停下来。

因此,我们需要分多核和单核情况。

多核相对好解决一点,cpu0最先启动,在它释放其他core时让cpu0去测试其他core的memory,如下:

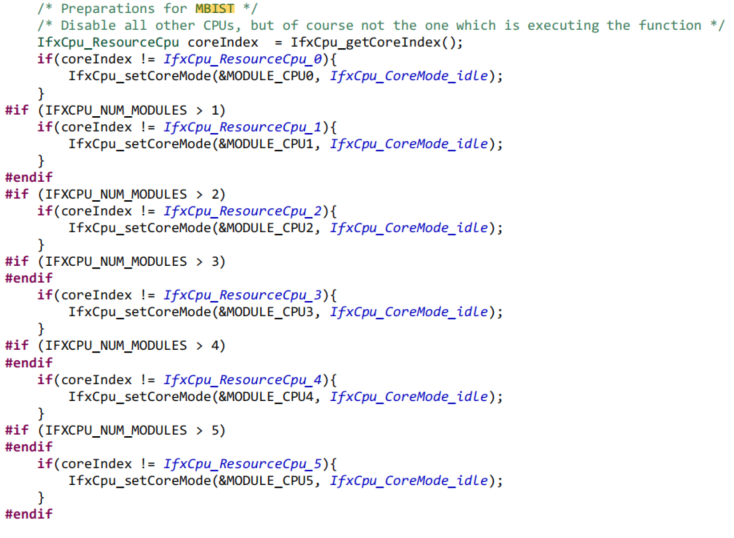

其他core去测cpu0时,让cpu0进入ilde即可。代码如下:

单核的情况说起来也简单,就是让CPU在执行测试期间不访问DSPR和PSPR,在英飞凌的MTU设计中,当我们使能了SRAM的SSH后该SRAM就不能访问了,

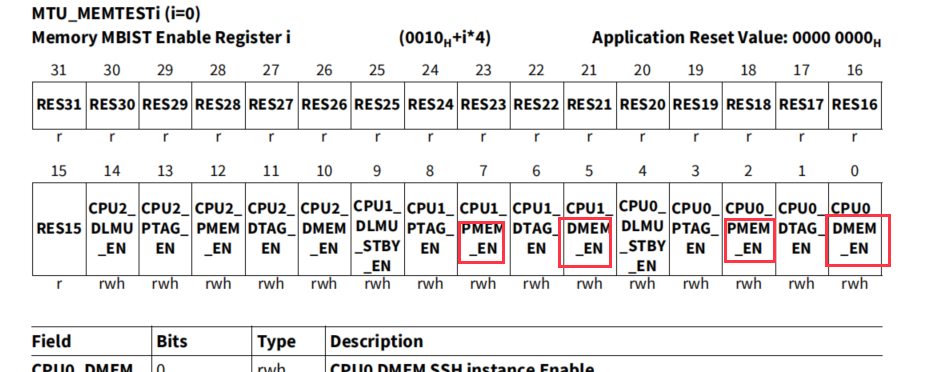

(代码示例MTU_MEMTEST0.B.CPU0_DMEM_EN = 1;)

这就需要我们在设计链接文件的时候要了解DSPR和PSPR具体包含了啥内容,并且在执行上述代码后就不调用PSPR的函数,也不要使用stack、csa,只用cpu相关寄存器,参考代码如下:

此外,为防止cache访问,P\D Cache在被测试的时候都需要关闭,参考CPU寄存器PMAxx。

2.MTU中PMEM的特殊处理

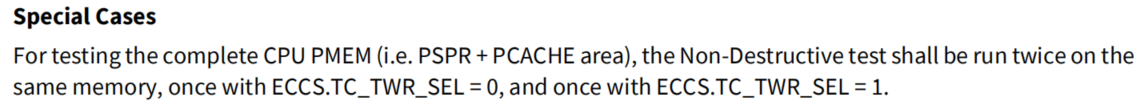

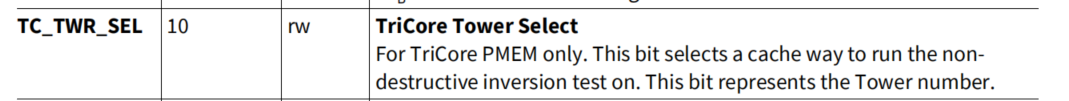

在手册里,有一点我没有特别想明白,但也是比较关键的地方,就是关于PMEM的特殊处理,原文如下:

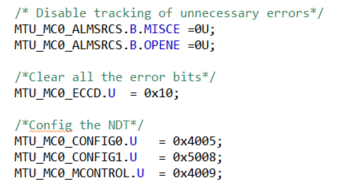

要完整测试PMEM,就需要执行两次NDT测试,由寄存器TCCS.TC_TWR_SEL进行管理,如下:

那代码中处理也比较方便,伪代码如下:

if(E_OK == CheckPmem(SramInstanceID))

{MTU_MCx.ECCS.TC_TWR_SEL = 0;triggerTest(SramInstanceID);MTU_MCx.ECCS.TC_TWR_SEL = 1;triggerTest(SramInstanceID);

}但有一点一直没想明白,PMEM包含了PCache和PSPR,DMEM同样也包含了DCache和DSPR,为啥PEME要特殊对待,DSPR就不用呢?

从MTUTEST寄存器看没有什么差别呀:

神奇,属实神奇。

差不多就到这,拜拜。