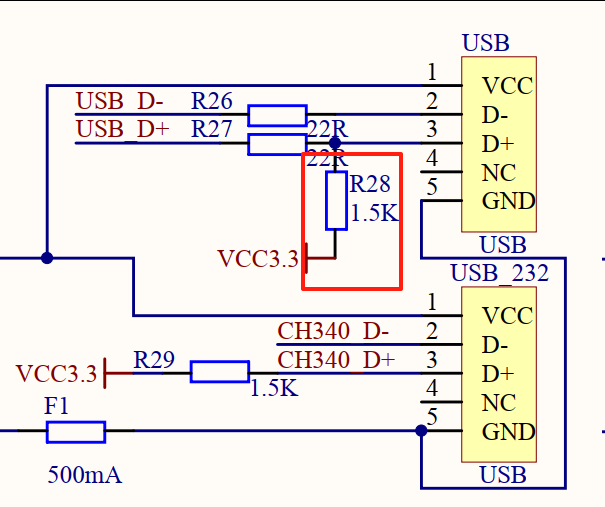

STM32F103RC的USB上拉电阻1.5K

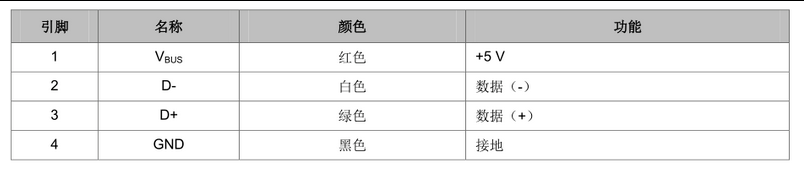

1.USB标准的连接器引脚分布

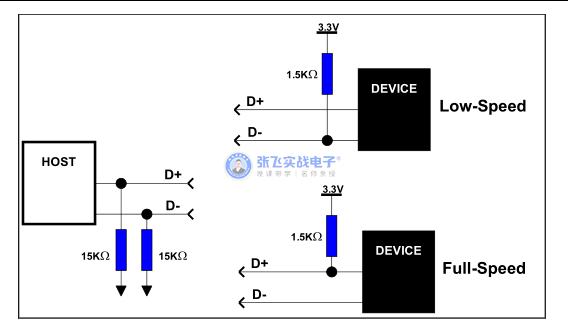

2.USB主机检测设备插入的原理

USB集线器的每个下游端口在D+和D-线上均连接了15kΩ的下拉电阻到地。当集线器的端口悬空没有设备插入时,这两条信号线被下拉至低电平,主机检测到稳定的逻辑低电平,判断端口空闲。

2.1设备插入时的电平变化

USB设备端在D+或D-线上连接了1.5kΩ的上拉电阻至3.3V电源。上拉电阻的位置取决于设备的速度:

全速/高速设备: 上拉电阻连接至D+线,插入后D+被拉高至逻辑高电平,D-保持低电平。

低速设备: 上拉电阻连接至D-线,插入后D-被拉高至逻辑高电平,D+保持低电平。

2.2主机识别过程

主机通过检测D+或D-线的电平变化判断设备插入及速度:

全速/高速设备: D+高电平(D-低电平)触发全速/高速模式识别。

低速设备: D-高电平(D+低电平)触发低速模式识别。

无设备: D+和D-均为低电平,端口视为空闲状态。

3.STM32的USB通信

根据DP/DM引脚的不同状态工作在主机或设备模式。在设备模式下,只支持高速或全速,不支持低速。OTG模式下,MCU通过VBUS和ID引脚判断角色,ID=0为HOST,DP/DM下拉;ID=1且VBUS有电则为Device,DP自动上拉。STM32内置的DP有上拉电阻,表明不支持低速设备模式。

补充: F1系列肯定不支持内嵌的上下拉,后来新出的系列基本都支持了。OTG模块的DM DP支持软件动态配置上下拉。集成了上拉/下拉电阻,意味着外部不需要上下拉电阻,通过软件功能就可以自动控制了。

4.STM32F103RC的USB电路设计

F1系列MCU电路设计上需要加入上拉电阻1.5k,不然识别不到usb设备。