计算机组成原理第4章 指令系统(竟成)

第 4 章 指令系统

【考纲内容】

1.指令系统的基本概念

2.指令格式

3.寻址方式

4.数据的对齐和大 / 小端存放方式

5.CISC 和 RISC 的基本概念

6.高级语言程序与机器级代码之间的对应

(1)编译器、汇编器和链接器的基本概念

(2)选择结构语句的机器级表示

(3)循环结构语句的机器级表示

(4)过程(函数)调用对应的机器级表示

【考情统计】

年份

题数及分值 考点

单选题数

综合题数

总分值

2009

2

0

4

寻址方式、CISC 和 RISC 的基本概念

2010

0

1

11

指令格式、寻址方式

2011

2

0

4

寻址方式

2012

1

0

2

数据的对齐和大 / 小端存放方式

2013

1

1

16

寻址方式

2014

1

1

14

指令格式、寻址方式、高级语言程序与机器级代码之间的对应

2015

1

1

12

指令格式、寻址方式、高级语言程序与机器级代码之间的对应

2016

1

0

2

寻址方式

2017

2

1

11

指令格式、寻址方式、CISC 和 RISC 的基本概念、高级语言程序与机器级代码之间的对应(x86)

2018

2

0

4

大 / 小端存放方式、寻址方式

2019

1

1

18

大 / 小端存放方式、寻址方式、高级语言程序与机器级代码之间的对应(x86)

2020

2

0

4

指令格式、数据的对齐和大 / 小端存放方式、寻址方式

2021

0

1

15

指令格式、寻址方式、高级语言程序与机器级代码之间的对应(MIPS)

2022

3

0

6

指令格式、高级语言程序与机器级代码之间的对应

2023

1

1

7

寻址方式

2024

0

1

10

指令系统相关综合应用题

【考点解读】

指令系统是计算机组成原理的基础和重点章节,自从考纲将高级语言程序与机器级代码之间的对应加入到本章节之后,本章节的学习难度也增加了不少,需要考生花费一定的时间去认真学习。本章节通常会有两道选择题和一道大题,分值大约占 10 分,选择题通常会考查指令格式、数据寻址和大/小端存放方式等知识点,大题既根据该章节单独命过题(有结合 MIPS 或者 x86 相关代码考查过),也和中央处理器、存储器等知识点联合考查过。

【复习建议】

本章的重点是指令的寻址方式,其中最常考的是三大偏移寻址 (基址寻址,变址寻址和相对寻址)。此外,还要掌握指令的编码方式和数据对齐的方法,了解大/小端存放方式这两种字节存储模式以及 CISC 与 RISC 的特点与区别。高级语言与机器级代码之间的对应是大纲新增加的内容,但其实真题早就对此进行过考查,而且在考查时通常会给出必要的说明,因此学习的目标是能够看懂真题中的汇编语言。汇编语言通过一个或几个英文单词的缩写精准地描述了这条指令的含义,考生无需对其有畏惧情绪,因为每一条汇编指令都只是完成一件很简单的事情,认真阅读每一行代码后是不难理解的。在汇编指令中,过程调用所对应的机器级代码表示是难点,需要进一步理解堆栈操作以及对一些寄存器的处理。本章和 CPU 这个章节关系紧密,考生在学习到 CPU 中的指令执行过程和数据通路时可以与本章知识点结合学习。

请考生在学习过程中思考如下问题:

1.什么是指令?什么是指令系统?指令的结构是怎样的?

2.程序中对数组的操作可以用什么寻址方式实现?为什么相对寻址便于程序浮动?

3.过程调用中为什么要使用栈?

4.1 指令系统的基本概念

机器语言是不需要经过翻译就可以被机器所理解的语言,也是计算机唯一能够识别的语言,本质上是计算机能够识别的二进制代码。它由一条条语句构成,每一条语句就是一条机器指令。机器的指令系统是指一台计算机的所有机器指令的集合。一条机器指令执行一个基本操作,如传送数据、加法运算。从这个角度来看,程序就是由一系列有序的指令构成的。高级语言要在机器上执行,需要转换为机器语言程序。

一个完善的指令系统应具备以下特征:

1.完备性:要求指令种类丰富、功能齐全、数目足够使用。

2.高效性:要求利用该指令系统所编写的程序所占据存储空间小、执行速度快。

3.规整性:主要体现在对称性、匀齐性、指令格式和数据格式的一致性三个方面。

1.对称性:要求所有的寄存器和存储器单元都可被同等对待,所有的指令都可使用各种寻址方式。

2.匀齐性:要求可以支持各种数据类型。

3.指令格式和数据格式的一致性:通常要求指令长度和数据长度是字节的整数倍,以方便处理和存取。

4.兼容性:系列机各机种之间具有相同的基本结构和共同的基本指令集,使得在老旧型号的机器上运行的软件也可以在新型号的机器上运行。

4.2 指令格式

一条指令必须明显或者隐含地包括操作码、源操作数或其地址、结果地址、下条指令地址等信息,其中下条指令地址通常不需要明显给出,它隐含在 PC 中。因此一条指令通常由两部分组成:操作码字段和地址码字段。其本质是一串有意义的二进制数字。基本格式如图4.1所示:

指令字长就是一条指令所占用的存储空间的大小,即操作码字段的位数和地址码字段的位数之和。因为主存一般是按字节编址(有些题目是按字进行编址的,这点需要格外注意),所以设计指令系统的时候,指令字长往往设计成字节的整数倍。指令字长和机器字长没有固定的关系!但如果某指令的长度等于机器字长,则称该指令为单字长指令;如果是机器字长的两倍,则称为双字长指令;如果是机器字长的一半,则称半字长指令。

提示:机器字长是指计算机进行一次整数运算所能处理的二进制数据的位数。它通常和 CPU 内部数据通道的宽度相同并且会影响计算机的运算精度和运算速度。

4.2.1 操作码

操作码表示指令操作的性质及功能,比如加法、移位、转移等。操作码通常有两种,一种是定长的,即操作码的位数是固定不变的,另一种是不定长(或者称为变长)的,即操作码的位数是可以改变的。对于定长操作码,其位数则决定了该指令系统指令种类的最大数目。比如系统的操作码位数是 5 位,那么该指令系统指令的数目最多不超过 2^5=32 条。采用定长操作码指令格式的指令系统,其优点是硬件设计更简单,指令译码用时更短。

4.2.2 地址码

地址码包含了操作过程中所需的地址信息(可以是立即数,寄存器编号,主存地址或者 I/O 设备地址 )。指令中的地址可以指源操作数地址、结果存放的地址(有些题目会称之为目标操作数地址)以及下一条要执行指令的地址。然而在实际的指令中,某些地址字段是可以省略的。比如可以利用程序计数器 PC 来省略掉地址码中的下一条指令地址这个部分(因为程序计数器本来就可以存放下一条指令所在单元的地址 )。根据地址码字段中地址的数目,通常可以将指令分为四地址指令、三地址指令、二地址指令、一地址指令和零地址指令五种。

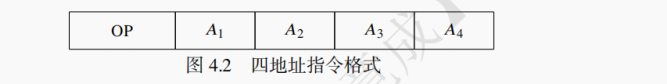

1. 四地址指令

地址码字段中有四个地址的指令。如图4.2所示:

其中,A1,A2 是两个源操作数的地址,A3 是存放结果的地址,A4 是下一条指令的地址。

这类指令执行的操作是 (A1)OP(A2)→A3,A4 = 下一条要执行指令的地址。提示:本书中使用符号 “→” 表示赋值的意思,A1 是地址,带括号的 (A1) 是取地址为 A1 的值。上面操作的意思是取 A1 和 A2 地址中的值进行 OP 操作,将所得的结果存至地址 A3 中,并把 A4 置为下一条要执行指令的地址。

现在有一个 32 位的指令,假如操作码字段是 8 位,那么地址码字段则为 24 位,因为有 4 个地址,因此每个地址平均占 6 位(4 个地址不一定是等长的,这里暂时考虑等长的情况 ),这 6 位二进制一共有 26=64 种组合,所以该类指令直接寻址的范围是 26=64。

假如 4 个地址均为主存地址,那么执行该指令需要有四次访存:取指令一次(指令是存在主存中的 ),取两个操作数两次,将操作后的结果存入主存中一次。

提示:分析访存次数的时候,要注意指令是单字长指令还是双字长指令,因为这将影响到取指令这个操作。如果是双字长指令,那么取出一条指令需要经过两次访存,才能完整地取出来,因此访存次数会相应地增加一次。下文在分析访存次数的时候,默认是在单字长指令这个条件下进行分析的。2. 三地址指令

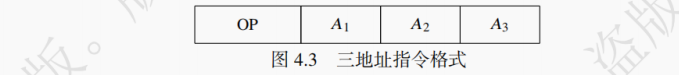

省略掉四地址指令中的 A4 便得到了三地址指令,其格式如图4.3所示:

上图中,A1,A2 是两个操作数的地址,A3 是存放结果的地址。

这类指令完成的操作是 (A1)OP(A2)→A3;(PC)+1→PC。

使用 PC 的自增形成下一条指令的地址来省略 A4 地址,对同样长度的操作码,分配给每个地址的位数变得更多,即每个地址的直接寻址范围变得更大。

提示:(PC)+1 操作是将 PC 置为下一条要执行指令的地址。PC 自增的大小和指令字长、编址方式相关。例如:指令字长是 32 位,按字节编址,这种情况下应为 (PC)+4;指令字长是 32 位,按字编址,字长是 16 位,这种情况下则为 (PC)+2。现在仍有一个操作码占 8 位,指令字长为 32 位的指令,若采用三地址指令格式,则每个地址平均占 8 位,那么每个地址的直接寻址范围扩大至 28=256。同样,若 3 个地址都是主存地址,那么执行该指令仍需要四次访存:取指令一次,取两个操作数两次,将操作后的结果存入主存中一次。

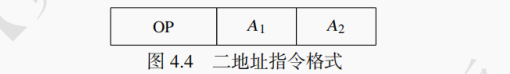

3. 二地址指令

计算机在运行的过程中,有时候可以将结果存入某个源操作数的地址中,而不是存入地址 A3 中,在这种情况下,便省略了三地址指令中 A3 字段,得到二地址指令。其格式如图4.4所示:

上图中,A1 和 A2 是两个操作数地址。

该类型指令可以完成 (A1)OP(A2)→A1;(PC)+1→PC 的操作。其中 A1 既是源操作数地址,又是操作后所得结果的地址(目标操作数地址 )。若 A1、A2 均是主存地址,那么完成该指令仍然需要四次访存:取指令一次,取两个操作数两次,将结果存回 A1 一次。

若将操作后所得的结果存放到 ACC 寄存器中,则该类型的指令还可以完成 (A1)OP(A2)→ACC;(PC)+1→PC 的操作。在这种情况下,若 A1、A2 均是主存地址,那么完成该指令仅需要三次访存:取指令一次,取两个操作数两次。现在仍有一个操作码占 8 位,指令字长为 32 位的指令,若采用二地址指令格式,则每个地址分到的位数是 12 位,那么每个地址的直接寻址范围扩大至 2^12=4K。

提示:对于二地址指令,根据其操作数的存储位置,可以细分为三种类型:寄存器 - 寄存器(RR)型指令、寄存器 - 存储器(RS)型指令、存储器 - 存储器(SS)型指令。RR 型指令的源操作数存储在寄存器中,操作后所得的结果存至寄存器中;RS 型指令的两个操作数来源不同,指令执行过程中既涉及对寄存器的访问又涉及对存储器的访问;SS 型指令的源操作数存储在存储器中,操作后所得的结果存至存储器中。4. 一地址指令

如果将一个源操作数隐含在累加器 ACC 中,那么就可以省略一个地址字段,形成一地址指令,其格式如图4.5所示。图4.5中,A1指操作数地址。

该类指令可以完成类似 (ACC)OP(A1)→ACC;(PC)+1→PC 的操作,其中 ACC 累加器既存放要参与运算的一个操作数,又临时存放操作后所得的结果。该类指令也可以完成类似 OP(A1)→A1;(PC)+1→PC 的操作,其中 A1 既存放源地址操作数,又是存放操作后所得的结果。

自增指令 INC 就是一种一地址指令,INC A1 指令的意思是将主存地址 A1 中的值 +1,然后将所得的结果存回 A1(考生可尝试分析一下访存次数 )。

分析访存次数的时候,一定要注意操作数地址代表的是主存地址、寄存器地址还是立即数。比如完成操作 OP(A1)→ACC(A1 是主存地址 ),只需要两次访存(取指令一次,取操作数 A1 一次 );若完成操作 OP(A1)→A1(A1 是主存地址 ),则需要三次访存(取指令一次,取操作数一次,将操作后的结果存到 A1 中一次 )。因为地址字段中只有一个地址,所以该类指令可进行直接寻址的范围将大大增加。现在仍有一个操作码占 8 位,指令字长为 32 位的指令,若采用一地址指令格式,则有 24 位留给地址码字段。这种情况下,直接寻址的范围扩大至 224=16M。

5. 零地址指令

在指令系统中,零地址指令是一类特殊的指令,它不需要任何的地址字段,只需要有操作码即可。其格式如图4.6所示:

零地址指令通常有两类:一种是无需操作数的指令,比如空操作指令、停机指令、关中断指令;另一种是操作数地址隐含的指令,比如在堆栈计算机中进栈(PUSH)、出栈(POP)的操作,其操作数地址隐含在堆栈指针 SP 中。