【ARM AMBA AHB 入门 3 -- AHB 总线介绍】

请阅读【ARM AMBA 总线 文章专栏导读】

文章目录

- AHB Bus 简介

- AHB Bus 构成

- AHB BUS 工作机制

- AHB 传输阶段

- AHB Interfaces

- AHB仲裁信号

- AHB 数据访问

- 零等待传输(no waitstatetransfer)

- 等待传输(transfers with wait states)

- 多重传送(multipletransfer)--Pipeline

- AHB 控制信号

AHB Bus 简介

AHB 总线的强大之处在于它可以将微控制器(CPU)、高带宽的片上RAM、高带宽的外部存储器接口、DMA总线Master、各种拥有AHB接口的控制器等等连接起来构成一个独立的完整的SOC系统,不仅如此,还可以通过AHB-APB桥来连接APB总线系统

AHB 可以成为一个完整独立的SOC芯片的骨架。

AHB Bus 构成

完整的 AHB 总线由四个部分组成:

- AHB 主设备 Master: 发起一次读/写操作;某一时刻只允许一个主设备使用总线

- AHB 从设备 Slave: 响应一次读/写操作;通过地址映射来选择使用哪一个从设备;

- AHB 仲裁器 Arbiter: 允许某一个主设备控制总线;

- AHB 译码器 Decoder: 通过地址译码来决定选择哪一个从设备。

AHB BUS 可以分为三组

- 写数据总线(HWDATA)

- 读数据总线(HRDATA)

- 地址控制总线(HADDR)

AHB BUS 工作机制

有需要占用总线的 Master向 Arbiter 发出请求, Arbiter授权给指定的Master。任一时间周期只有一个 Master 可以接入总线,对其指定的 Slave 进行读写操作。

获得总线授权的 Master开始 AHB 传输, 首先发出地址和控制信号, 提供地址信息、传输方向、带宽和burst类型。总线统一规划 Slave 的地址, 译码器根据地址和控制信号确定哪个 Slave 与Master进行数据通信。数据传输通过数据总线完成。

为避免出现三态总线 AHB 将读写总线分开, 写数据总线用于从 Master 到 Slave 的数据传输, 读数据总线用于从 Slave 到 Master 的数据传输。

每笔传输包括一个地址和控制周期, 一个或多个数据周期。地址和控制周期不能被扩展, 因此 Slave 必须在一个周期内采样地址信号。

数据周期可以通过 HREADY 信号扩展, 但 HREADY 为低时给传输加入一个等待状态以使 Slave获得额外的时间来提供或采样数据, 另外 Slave 通过响应信号 HRESP 反映传输状态。

AHB支 持批量式数据传送, 可以自动递增地址。递增地址方式分为: 持续递增与回绕传送。

一般情况下 Master 完成完整的 burst 传输, Arbiter 才会授权给其他的 Master 接入总线, 然而为避免过大的判决延迟, Arbiter也可能打断断burst传输。在这种情况下Master 必须再次接入总线以进行中断的 burst 剩余部分的传输。

AHB 传输阶段

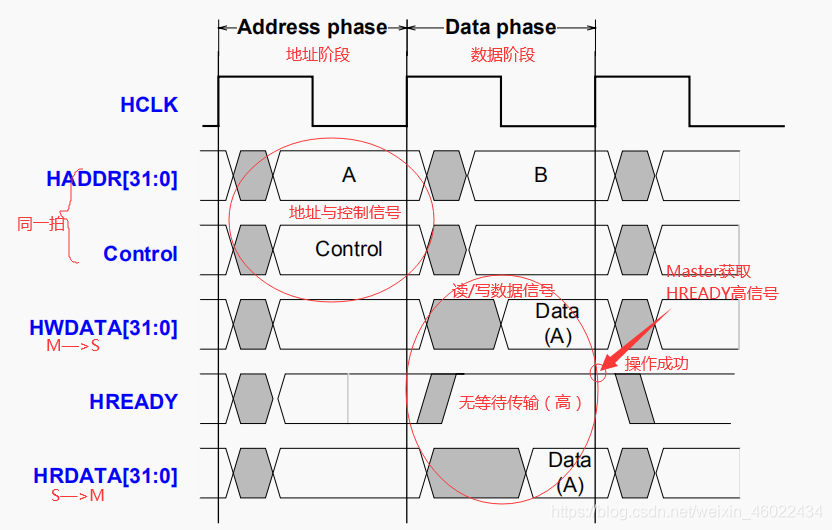

AHB的传送模式包含二个阶段。第一阶段为地址的传递, 另一阶段为数据的传递。

- 地址传输阶段: (address phase):一个时钟周期

- 数据传输阶段: (data phase):一个或多个时钟周期(以HREADY信号控制周期数目)

AHB Interfaces

在实际的传输过程中,一般作为 AHB 总线的 Slave 设备都有 2 根 hrready信号, 一个为 input 类型(hready_in), 另一个为 outpute 型 (hready_out)。在 AHB 总线协议中,如果 Master 设备发起读写操作的时候,Slave设备不能及时响应的话,由Slave设备把 hready_out 信号拉低来拖延 Data Phaze 周期。

但是在Pipeline操作的时候,本次操作 data phaze是下一次操作的 address phaze, 所以作为 Slave设备在响应Master设备的时候, 必须先判断一下Master设备对上一次其它Slave设备的操作是否已经完成。如果完成,则响应主设备的操作;如果没有有完成,则等待完成, 然后才响应操作。hready_in 就是 Slave 设备用来判断Masteer设备是否对其它Slave设备的操作已经完成的信号。

AHB仲裁信号

AHB 数据访问

零等待传输(no waitstatetransfer)

- 第一个周期的上升沿, master 驱动地址和控制信号;

- 第二个周期的上升沿, slave 采样地址和控制信号,并将 HREADY 拉高;

- 如果是写操作, master 会在第二个周期的上升沿传输要写入的数据;

- 如果是读操作, slave 会在 HREADY 信号拉高后将读取的数据写写入总线;

- 第三个周期的上升沿,

- 如果是写操作, master获取 HREADY 高信号,表明slave已成功接收数据,操作成功;

- 如果是读操作, master 获取 HREADY 高信号,表明此时的读数据有效并且接收下来,操作成功。

需要注意,HREADY信号在数据有效期间必须为高, 并且延续到第三个周期的上升沿之后, 确保 master 的正确采样。

等待传输(transfers with wait states)

传送完成时间因等待而延迟,这是由于寻址到较慢的S单元所造/成。当HREADY被S拉低时,会发生等待状态。需要延迟传送的周期时, 就会在数据期间将HREADY拉低,此时地址与数据都必须延伸。有等待状态的AHB传递,下图中可看到在数据草式时, 时序必须多花二个周期的延迟等待时间(HREADY为0), S才能正常的接收收到M写的数据或准备好M欲读取的数据。

slave 可以及时处理 master 请求,但也可能存在 slave太慢不能立即处理的情况。这时需要让master 稍微等一等, 需要 slave 插入一些等待的状态。如上图所示, HREADY 信号在第二和第三周期拉低,意在告诉 master, slave 不能立即处理,需要 master等待2个周期。在这

里需要注意2点:

- 如果是写操作, master需要在等待期间保持写数据不变, 直到本次传输完成;

- 如果是读操作, slave不需要一开始就给出数据,仅当HREADY拉高后才给出有效数据。

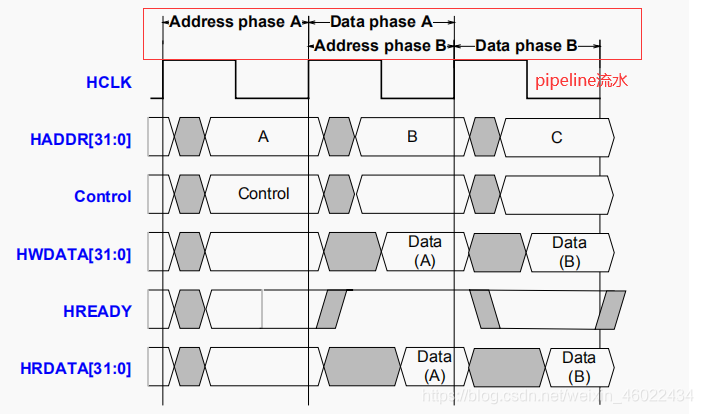

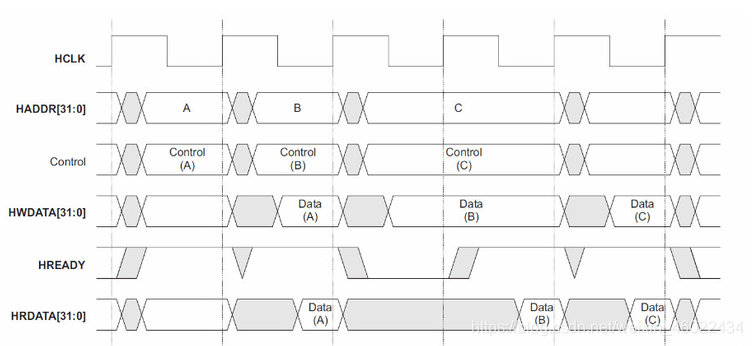

多重传送(multipletransfer)–Pipeline

一次完整的数据传送会有多个传送周期, 如下图下一笔地址可与上一笔数据同时在总线上, 时序图的说明如下:

下图是对上图的补充:

扩展数据周期的一个负效应是必需延长相应的下一笔传输的地址周期。A和C为零等待传输,B加入了一个等待周期,因此相应的C地址期要进行扩展。

- 第一个周期,master发起一个操作A,并驱动地址和控制信号;

- 第二个周期,slave收到了来自总线的请求,将HREADY信号拉高;

- 第二个周期上升沿后,master发现有操作B需要执行,并且检查到上一周期的HREADY为高,则发起第二个操作B;

- 第三个周期,master获取HREADY信号为高,表示操作A已经经完成

- 第三个周期上升沿后,master发现有操作C需要执行,并且检查到上一周期的HREADY为高,则发起第三个操作C;

- 第三个周期上升沿后,slave由于繁忙插入了一个等待状态,将HREADY拉低;

- 第四个周期,master获取HREADY信号为低,知道slave希望等待于是master保持和上一拍一样的信号;

- 第四个周期,slave处理完了事务,将HREADY信号拉高,表示可以继续处理;

- 第五个周期,master获取HREADY信号为高,知道slave已经可以处理B操作;

- 第五个周期上升沿后,B操作完成;

- 第六个周期上升沿后,C操作完成。

注意:

HREADY在一定程度上表示了slave的pipeline能力,在AHB中是2个pipe,也就是总线上最多存在2个未处理完的transfer。只有当总线上

未完成的transfer少于2个时,master才能发起操作。

AHB 控制信号

见下篇文章:【ARM AMBA AHB 入门 3.1 – AHB控制信号】

推荐阅读:

https://blog.csdn.net/weixin_46022434/article/details/104987905