【先楫HPM5E00_EVK系列-板卡测评3】hpm5e00evk平台中断、定时器、PWM、USART等基础功能详解

此文介绍了利用先楫半导体(hpm)官方hpm5e00_evk开发板使用的主控芯片的一些原理性知识,无实验内容展示,主要汇总了先楫半导体hpm5e00主控芯片的中断、定时器、pwm、usart等功能,主要内容来源于B站“HPM_FAE”的视频和官方的数据手册,如有整理不正确的地方还望指正。

至于为啥整理上面几个外设,因为上面几个外设是本人工作项目中,用到的最基本的内容,把上面外设跑通了就可以实现国产替代,当然还有一些深入的功能,待后续研究。

1、中断

先楫半导体(HPMicro)的微控制器中断系统,是其高性能MCU的重要组成部分,它基于RISC-V内核,并借鉴了现代中断控制的先进理念。其核心在于高效管理多种事件源(如外部设备、内部外设、软件事件),确保关键任务能得到及时响应。

1.1、中断定义与原理

中断是一种允许微控制器暂停当前正在执行的程序,转去处理紧急事件,待处理完成后再返回原程序继续执行的机制。在先楫半导体的微控制器中,中断系统主要用于:

• 提高实时性:对外部事件(如按键、传感器信号变化)或内部事件(如定时器溢出、通信数据到达)做出快速响应。

• 提升效率:避免了CPU不断轮询检查事件是否发生,节省了宝贵的计算资源,使其能专注于主要任务,只有在需要时才通过中断介入处理。

• 处理故障:为硬件故障、运算异常(如除零错误)等提供了处理机制。

中断可以是硬件中断(由外部硬件信号触发,如GPIO、定时器)或软件中断(由特定的软件指令触发)。中断系统的工作原理与流程,中断处理通常包含以下步骤:

中断请求:中断源(例如外设或软件)通过发出中断请求信号向CPU申请服务。

中断判优与响应:中断控制器(如果存在类似NVIC的模块)会根据预设的优先级对多个同时发生的中断请求进行裁决,选择当前最高优先级的请求向CPU响应。CPU在执行完当前指令后,若中断未被全局屏蔽,则会响应此中断。

保护现场:CPU在跳转执行中断服务程序前,会自动保存当前的程序计数器(PC)和状态寄存器等关键信息,以便中断处理后能正确恢复。

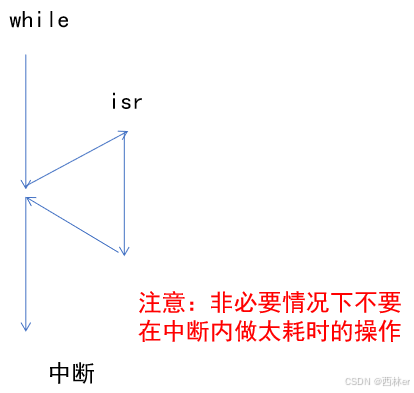

执行中断服务程序:CPU通过查询中断向量表(一个存储了各个中断服务程序入口地址的表格)跳转到对应的中断服务程序(ISR) 执行。开发者需要在此函数中编写处理特定中断事件的代码。

恢复现场与返回:ISR执行完毕后,通过特定的中断返回指令,CPU会恢复之前保存的现场信息,并返回到被中断的主程序继续执行。

1.2、先楫MCU中断

先楫MCU中断分为本地中断与外部中断,常用的本地中断包括机器定时器中断与软件中断。先楫MCU支持8个中断优先级设置,设置值0~7,优先级设置值越大中断优先级越高,0代表关闭中断。

针对先楫MCU中断:

没有硬件压栈,进出中断耗时略长一些,但是hpm主频一般ARM类的MCU主频高很多,进出中断其实也还好;

支持中断优先级和中断嵌套,当多个中断同时发生时,优先级高的中断会优先得到响应,允许高优先级中断打断正在处理的低优先级中断;

支持中断嵌套与中断向量,中断嵌套可保证CPU始终在处理优先级最高的中断,中断向量则可简化中断处理流程,提高中断响应速度

另外尤其要注意的是:本地中断可打断外部中断,外部中断无法打断本地中断。

1.3、中断使用注意

项目之初,在设计中断的是时候,需要特别注意一下事项:

• 避免中断过长:长时间的中断会阻塞系统对其他事件的响应,影响实时性。

• 谨慎处理中断嵌套:过深或设计不当的中断嵌套会增加系统复杂性,并可能引起优先级倒置等问题。

• 及时清除中断标志:这是最常见的错误之一,忘记清除标志位会导致程序行为异常。