FPGA实现VESA DSC编码功能

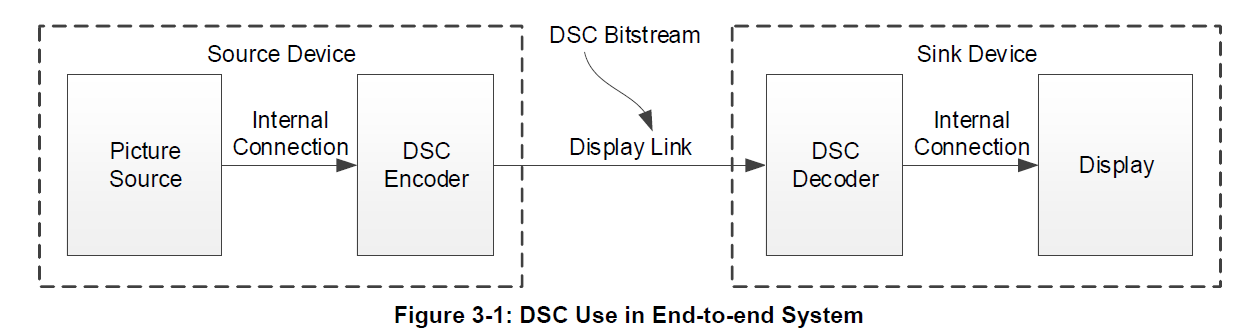

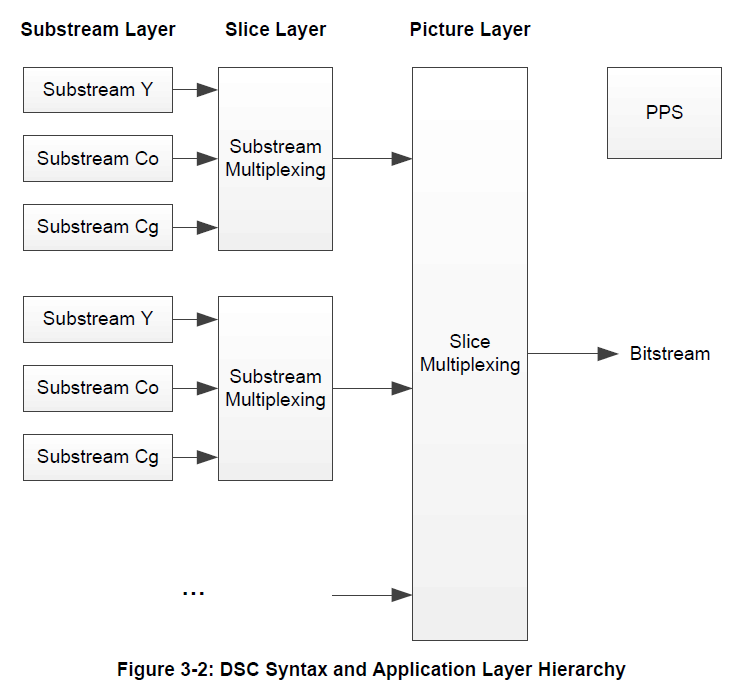

FPGA实现VESA DSC编码功能。Display Stream Compression (DSC)。

架构:

DSC编码输入数据为Ycbcr。

FPGA verilog top端口定义如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_SIGNED.ALL;

USE IEEE.NUMERIC_STD.ALL;

--=================================================================================================

-- DSC_Encoder entity declaration

--=================================================================================================

ENTITY DSC_Encoder IS

GENERIC(

-- Data width

G_DATA_WIDTH : INTEGER RANGE 0 To 12 := 8

);

PORT (

-- Port List

-- System reset

RESETN_I : IN STD_LOGIC;

-- System clock

PIX_CLK_I : IN STD_LOGIC;

-- Specifies the input data is valid or not

DATA_VALID_I : IN STD_LOGIC;

-- Luma Data input

DATA_Y_I : IN STD_LOGIC_VECTOR(G_DATA_WIDTH-1 DOWNTO 0);

-- Cb Data input

DATA_CB_I : IN STD_LOGIC_VECTOR(G_DATA_WIDTH-1 DOWNTO 0);

-- Cr Data input

DATA_CR_I : IN STD_LOGIC_VECTOR(G_DATA_WIDTH-1 DOWNTO 0);

-- Frame end input

FRAME_END_I : IN STD_LOGIC;

-- Hres input

HRES_I : IN STD_LOGIC_VECTOR(G_DATA_WIDTH+7 DOWNTO 0);

-- Vres input

VRES_I : IN STD_LOGIC_VECTOR(G_DATA_WIDTH+7 DOWNTO 0);

-- Data valid out

DATA_VALID_O : OUT STD_LOGIC;

-- Data out

DATA_O : OUT STD_LOGIC_VECTOR(47 DOWNTO 0)

);

END DSC_Encoder;

module DSC_Encoder_vid

(

input I_pxl_clk ,//pixel clock

input I_rst_n ,//low active

//input [23:0] I_rgb ,

// Data valid out

output DATA_VALID_O ,

// Data out

output [47:0] DATA_O

);

wire w_de,w_hsync,w_vsync;

wire [23:0] gen_pixdata;

wire [7:0] y_out;

wire [7:0] cb_out;

wire [7:0] cr_out;

wire data_valid;

mipi_colorbar_gen u_colorbar

(

.pix_clk_i(I_pxl_clk),

.reset_n_i(I_rst_n),

.pix_index(8'd5),

.pix_h_active(1920),

.pix_hbp(30),

.pix_hfp(30),

.pix_h_sync(30),

.pix_v_active(1080),

.pix_vbp(10),

.pix_vfp(10),

.pix_v_sync(10),

.pix_frame_set(16'd0),

.de_i(w_de),

.hsync_i(w_hsync),

.vsync_i(w_vsync),

.RGB(gen_pixdata)

);

DSC_Encoder DSC_Encoder_gen(

.RESETN_I (I_rst_n),

.PIX_CLK_I (I_pxl_clk),

.DATA_VALID_I (w_de),

.DATA_Y_I (gen_pixdata[23:16]),

.DATA_CB_I (gen_pixdata[15:8]),

.DATA_CR_I (gen_pixdata[7:0]),

.FRAME_END_I (~w_vsync),

.HRES_I (),

.VRES_I (),

.DATA_VALID_O (DATA_VALID_O),

.DATA_O (DATA_O)

);

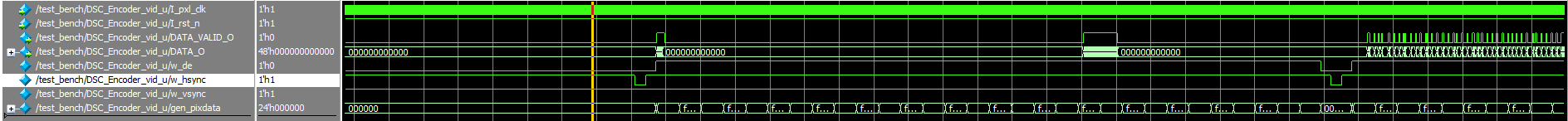

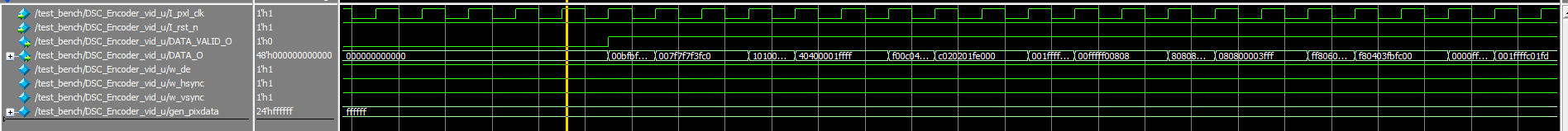

仿真如下:

欢迎讨论交流

微:moning_hello