嵌入式学习的第四十四天-ARM

一、ARM内核基础知识

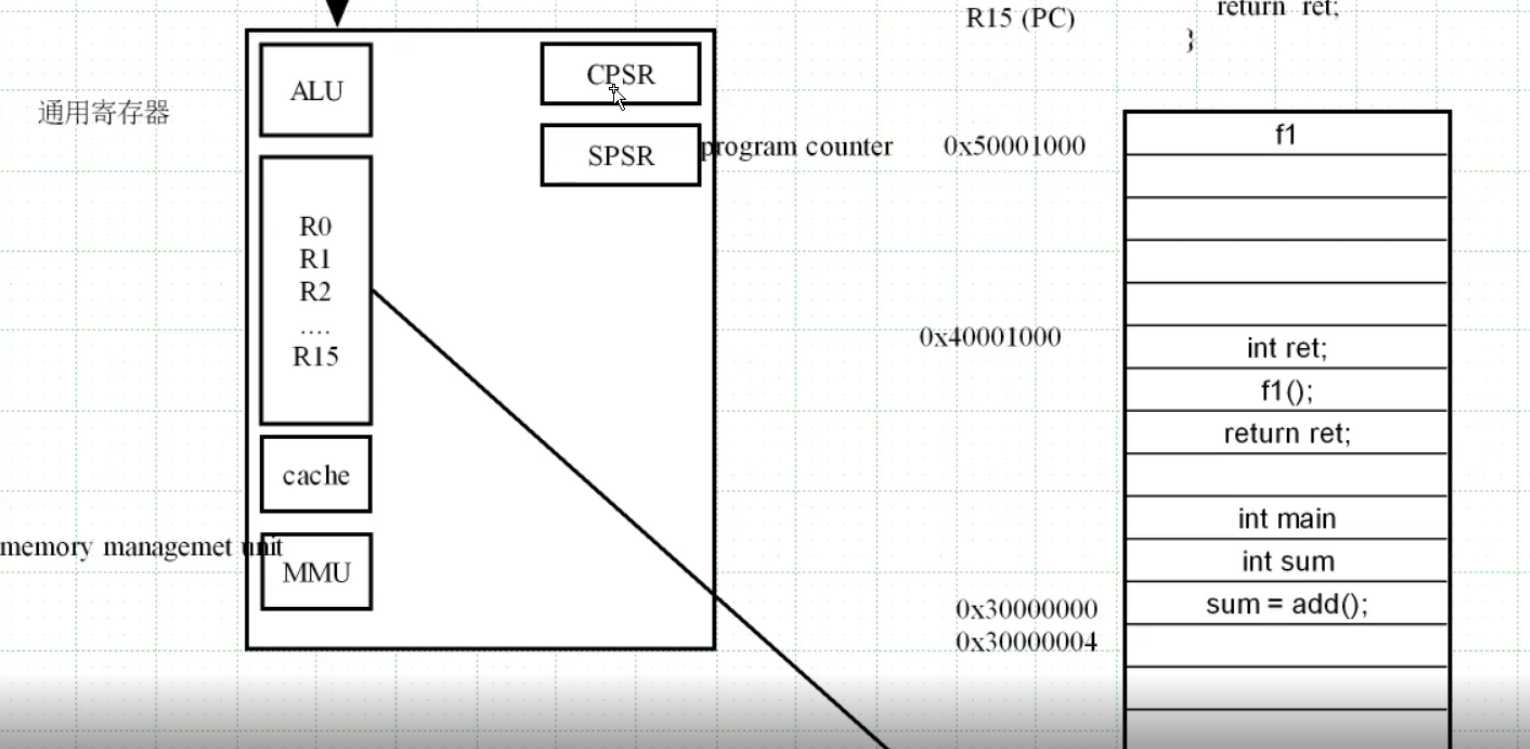

1.ALU

算术逻辑单元;完成运算的电路

2.通用寄存器:R0~R15

- R13(SP):栈指针寄存器:指向栈的指针(指向正确的位置),为了保护现场

- R14(LR):连接寄存器:保存PC要回来的位置,在PC调用完了,把地址给PC

- R15(PC)program counter 程序计数器;保存当前指令要执行的下一条指令的地址

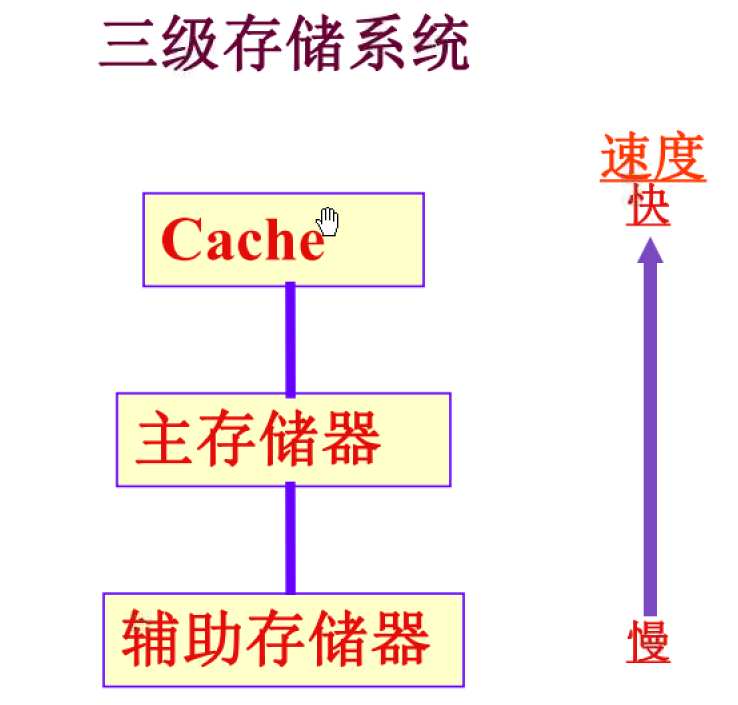

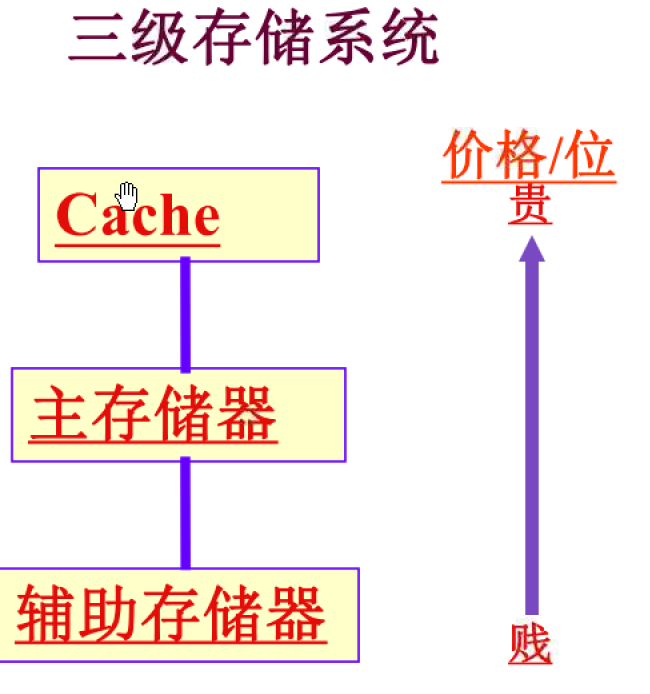

3.cache

高速缓存;RAM和内核速度不匹配;

- I cache:指令高速缓存 instruction

- d cache:数据高速缓存 data

4.MMU:memory management unit

内存管理单元;映射虚拟内存和物理内存:提高内存的使用效率

5.CPSR:current program status register

程序状态寄存器。

- 用户级编程时用于存储条件码

- 任何处理器模式下被访问

- 两种运行状态:ARM状态(32位)、Thumb状态(16位),两种状态之间可任意切换

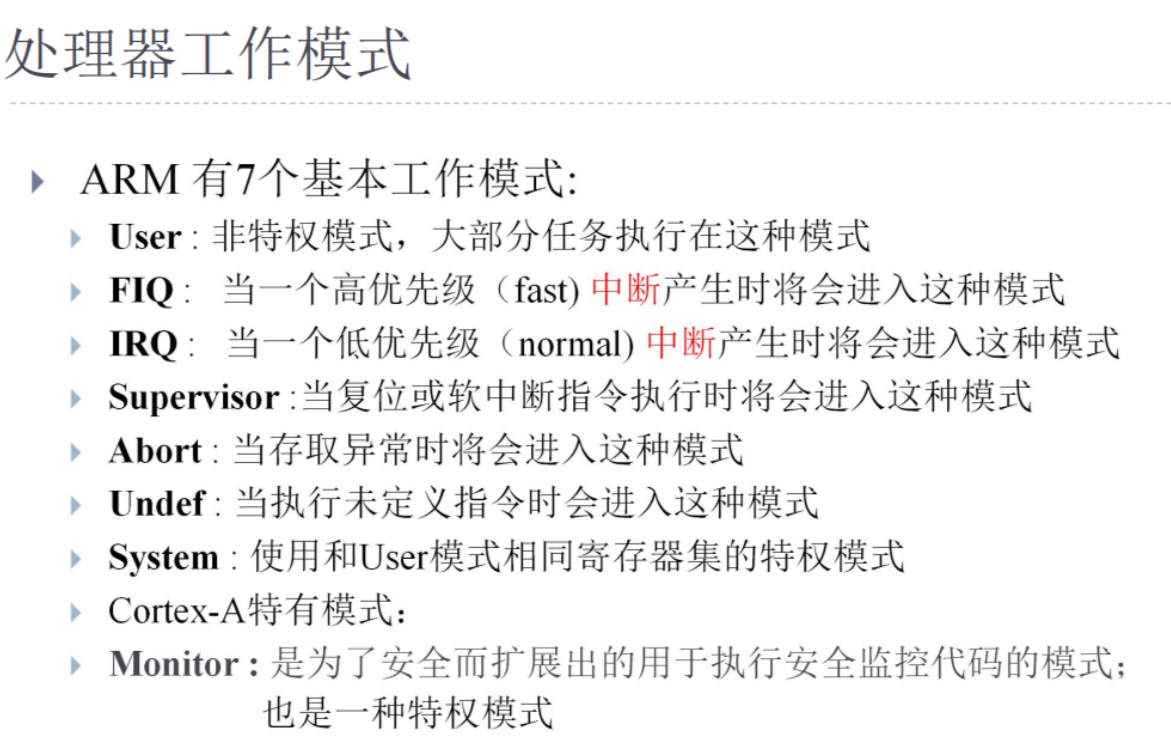

- 七种运行模式:usr(用户)、fiq(快速中断)、irq(外部中断)、svc(管理)、sys(系统)、abt(数据访问中止)、und(未定义指令中止)

6.SPSR:saved program status register

程序状态保存寄存器。

- 每一种处理器模式下都有一个状态寄存器SPSR,用于保存CPSR的状态,以便异常返回后恢复异常发生时的工作状态。

- 当特定的异常中断发生时,这个寄存器存放CPSR的内容。

- 在异常中断退出时,可以用SPSR来恢复CPSR。

7.CISC:complex instruction set computer

复杂指令集计算机

- 特点:指令集复杂、可变长度,单条指令可完成多步操作(如x86)。

优势:代码密度高,但硬件设计复杂,功耗较高,在80%情况下,只能用20%功能。

8.RISC:reduce instruction set computer

精简指令集计算机

特点:指令集简单、固定长度,执行效率高,通常采用流水线技术,依赖编译器优化。

优势:低功耗、高性能,适合嵌入式系统(如ARM、MIPS)。

9.cortex 系列:(从ARM 11)

- cortex A:应用,消费类电子,便携类设备;A7系列

- cortex R:实时性高,高端,军工、卫星;

- cortex M:单片机系列;

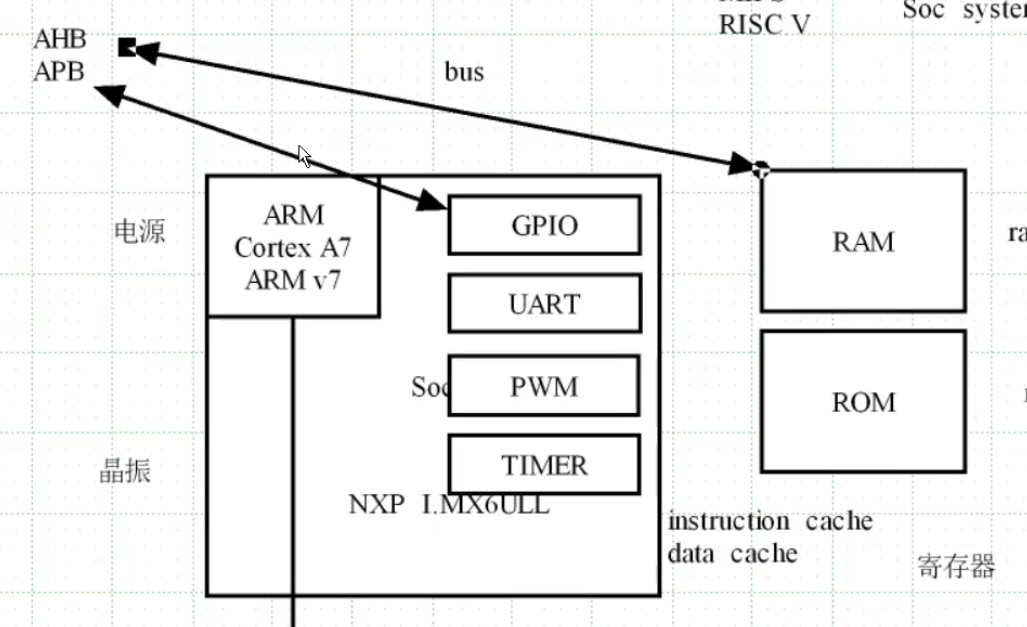

10.总线(bus)

AHB:先进的高速总线,连接高速设备,USB、RAM(早期叫北桥)

APB:先进外设总线,连接低速设备串口、GPIO,定时器(早期叫南桥)

11.哈佛结构和冯诺依曼

(1)哈佛架构

程序存储和数据存储分离:哈佛架构使用独立的存储器和总线来分别存储程序和数据。程序存储器专门用于存储指令,数据存储器用于存储变量和数据。

(2)冯·诺伊曼架构

程序存储和数据存储统一:冯·诺伊曼架构使用同一套存储器和总线来存储程序和数据。程序和数据存储在同一个存储空间中,通过地址来区分指令和数据。

(3) ARM内核

早期经典ARM(如ARM7)采用冯·诺伊曼架构;

现代ARM(如Cortex-M/A系列)采用改进的哈佛架构(缓存层级分离指令/数据)。

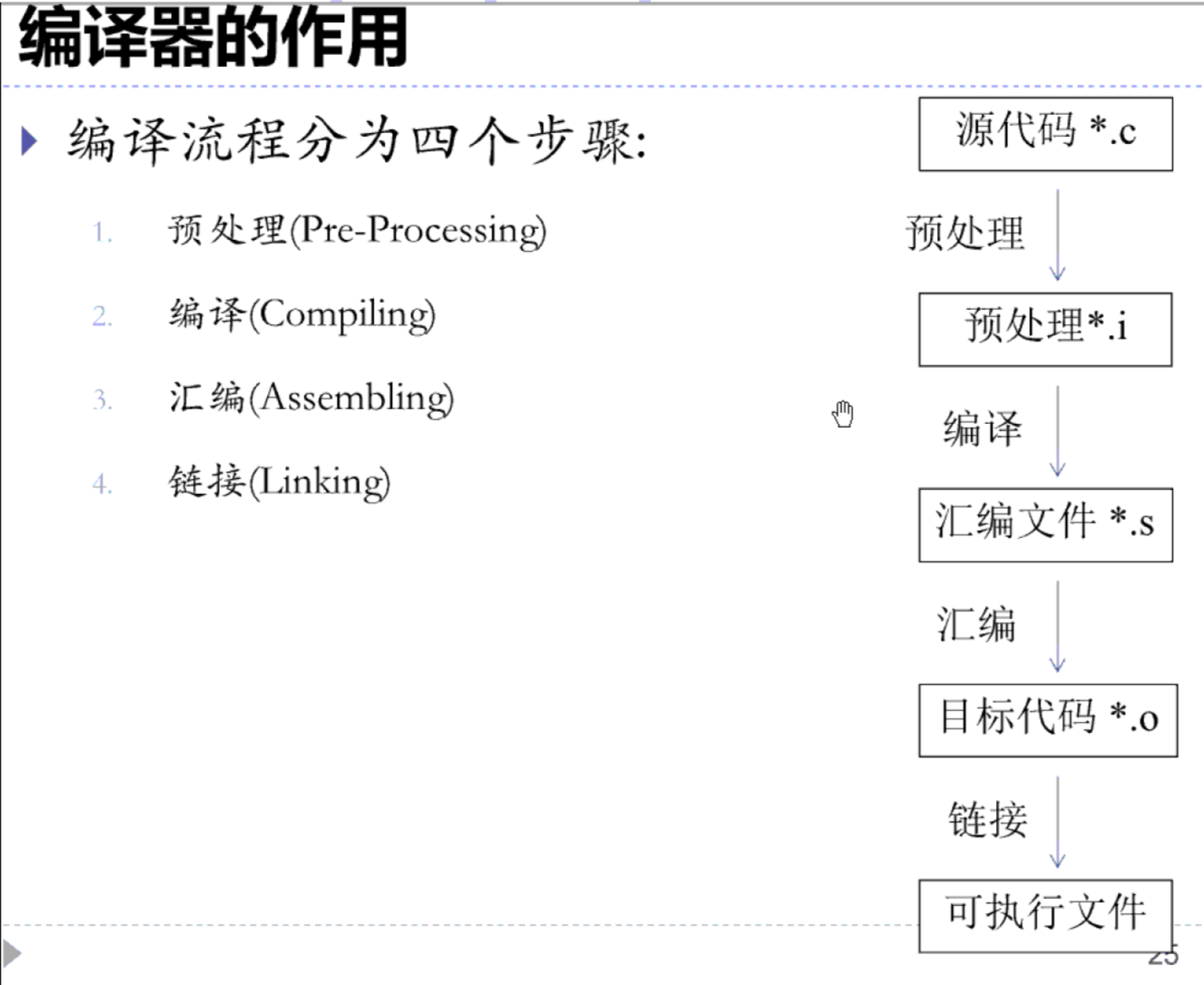

12.编译器

- 注:交叉编译工具链:arm-gcc,编译出来的代码无法在主机运行,只能在目标机上运行。

- 对内核进行操作,比如关闭MMU,打开SP,打开I cache,关闭d cache

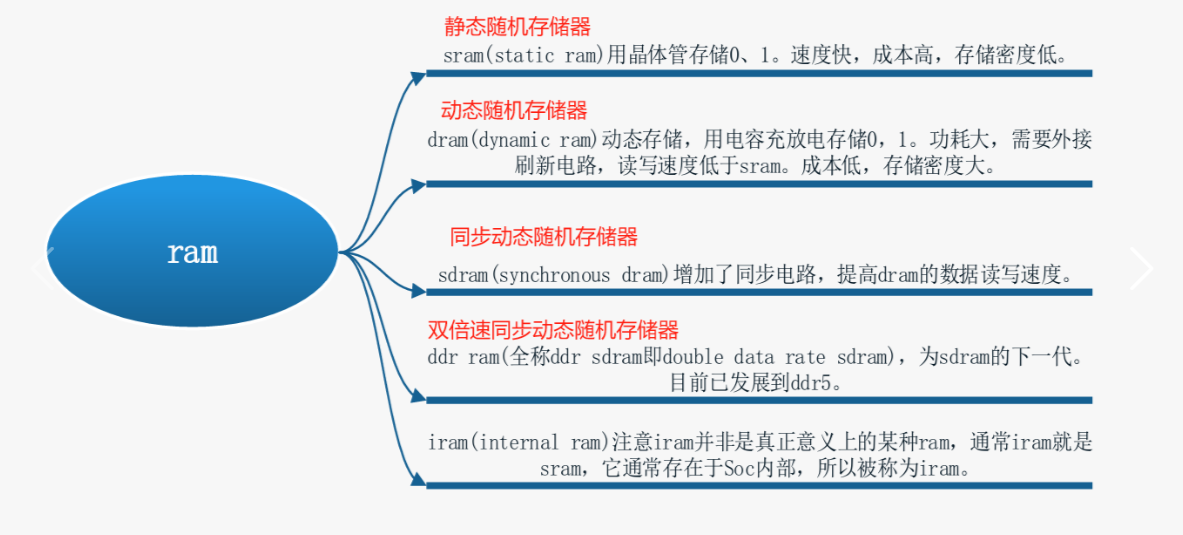

二、RAM分类

(1)sram(static ram)

用晶体管存储0、1;

速度快,成本高,存储密度低;

应用于单片机。

(2)dram(dynamic ram)动态存储

用电容充放电存储0,1;

功耗大,需要外接(外接刷新电路,电路复杂(定期向存储1的补充电荷)),读写速度低于sram,成本低,存储密度大;

多应用与高端Soc。

(3)sdram(synchronous dram)

增加了同步电路,提高dram的数据读写速度(dram升级版)。

(4)ddr ram(ddr sdramldouble data rate sdram)

为sdram的下一代;双倍速(双数据速率)

(5)iram(internal ram)

注意iram并非是真正意义上的某种ram,通常iram就是 sram,它通常存在于Soc内部,所以被称为iram(Soc内部直接封装好在芯片内部的sram)

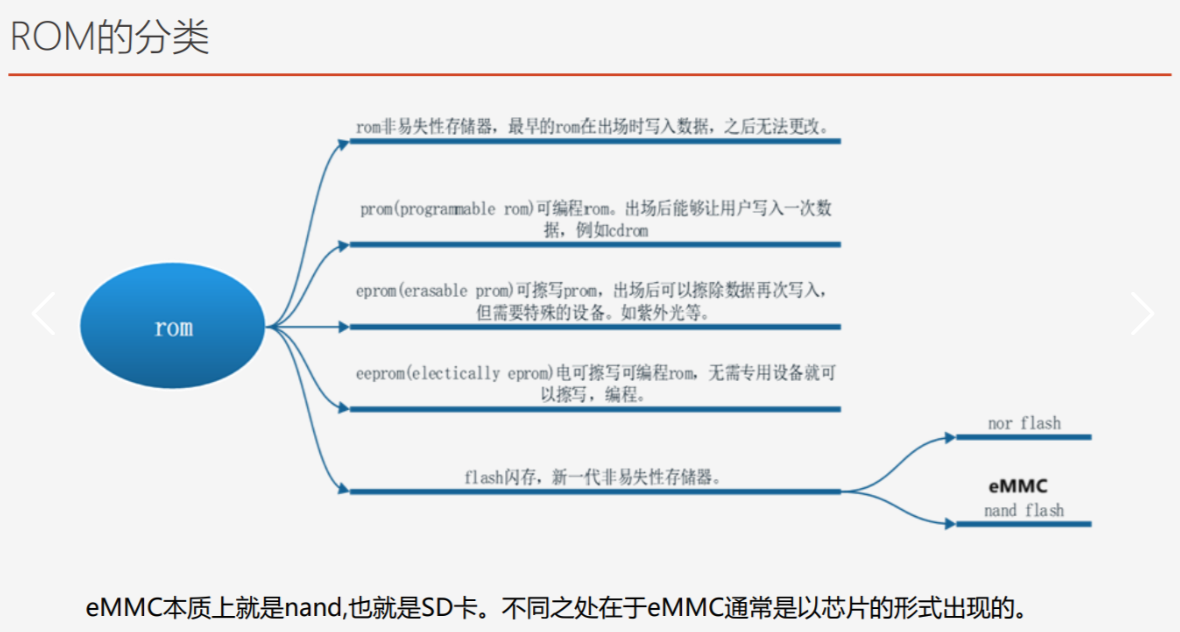

三、ROM分类

(1)rom非易失性存储器

最早的rom在出场时写入数据,之后无法更改。

(2)prom(programmable rom)可编程rom

出场后能够让用户写入一次数据,例如cdrom。

(3)eprom(erasable prom)可擦写prom

出场后可以擦除数据再次写入, 但需要特殊的设备,如紫外光等。

(4)eeprom(electically eprom)电可擦写可编程rom

无需专用设备就可以擦写,编程。

(5)flash闪存,新一代非易失性存储器

1)nor flash(或非falsh)

可直接被CPU寻址(每个字节都有独一无二的地址)

2)nand flash(与非falsh)

不可被COU寻址,每个字节不可被寻址(用flash控制器可以访问)

(6)存储系统的速度和价格对比

四、ARM处理器工作模式(kernal)

Cortex A7有9种基本工作模式

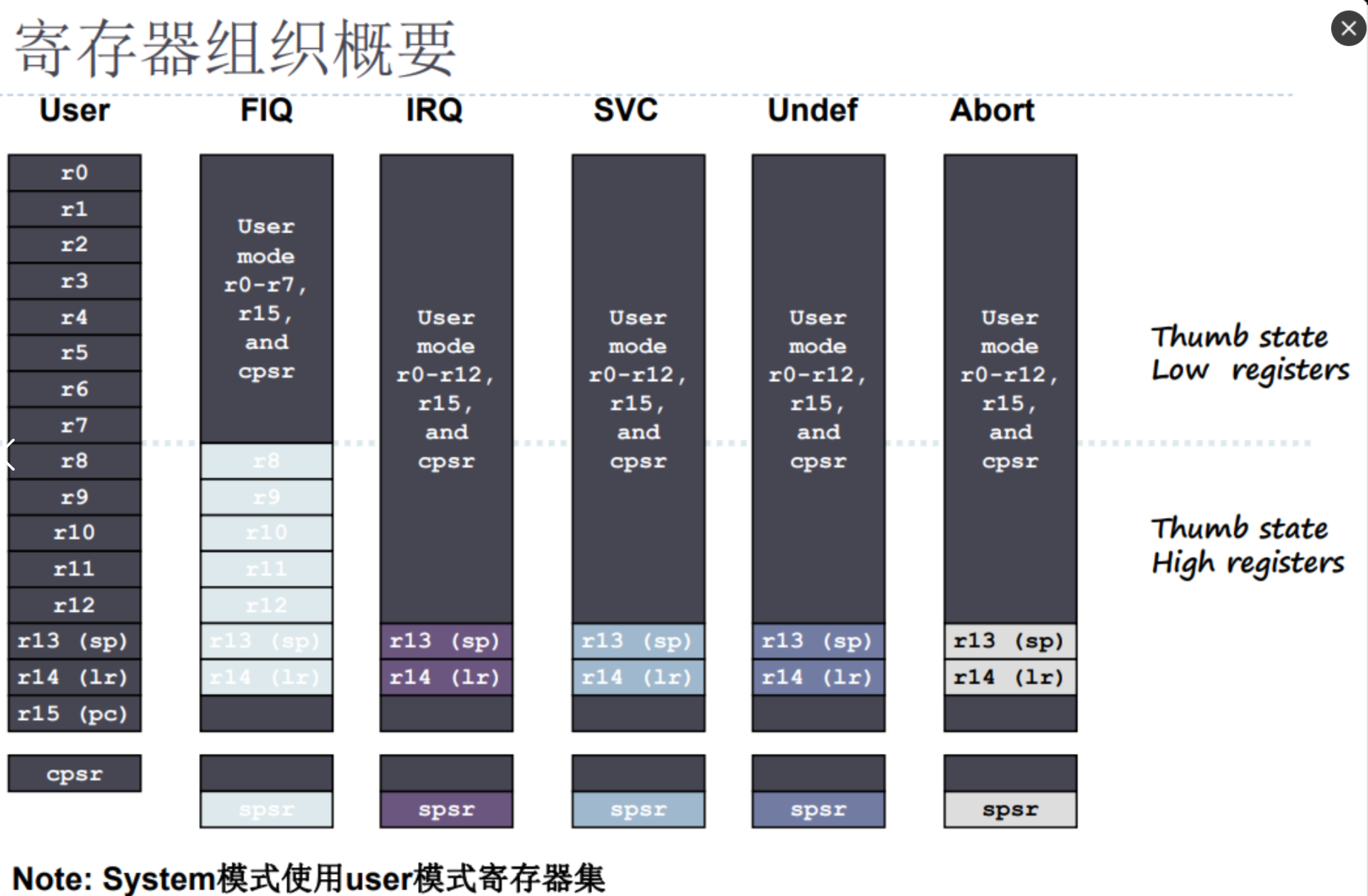

五、寄存器概要

注:1.PC所有模式公用;不同的工作模式下,各状态都有自己独立的栈区空间,管理不同的栈(SP和LR);

2. ARM9 :37个寄存器;cortex A-7有40个寄存器

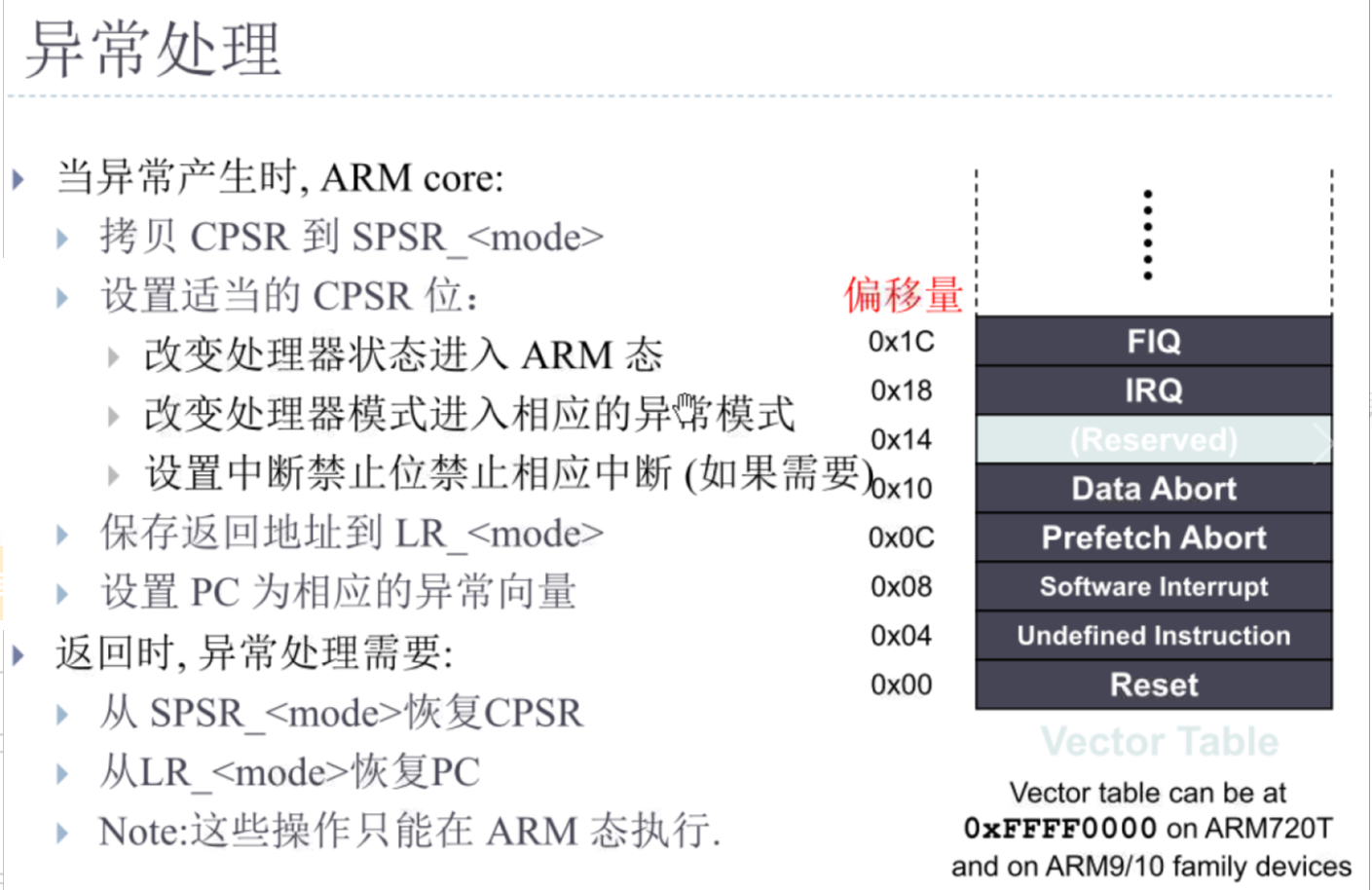

六、异常处理

1.异常模块

- FIQ中断

- IRQ中断

- Data Abort(数据存储异常):对RAM的访问发生错误

- Prefetch Abort(预取失败异常):指令预取阶段内存访问失败触发

- Software Interrupt(软中断异常):软件中断(任务切换),多任务的并发靠底层的软中断实现

- Undefined Instruction(未定义指令异常)

- Reset(复位异常)

2.异常向量表

定义:一段固定地址的内存区域(通常位于0x00000000或0xFFFF0000),存储异常处理函数的入口地址。

内容:每个异常类型对应一个4字节跳转指令

3. 当异常发生时,ARM内核会做哪些操作?

保存现场:

将当前PC(下一条指令地址)存入LR(如LR=PC-4或PC+4),CPSR存入SPSR(备份状态)。切换到对应的异常模式(如IRQ模式)。跳转至异常处理:

从异常向量表获取处理函数地址,执行异常服务程序(ISR)。中断屏蔽:

自动禁用同级或低优先级中断(FIQ可能不被屏蔽)。返回恢复(手动操作):

通过特定指令(如SUBS PC, LR, #4)恢复PC和CPSR,返回到原程序。