UFS Layout Guide (UFS 2.x)

关于PCB叠层

- 设置GND层和关键信号层,确保信号有一个稳定的地参考平面,这对UFS的传输线的必要条件

- 带状线是强烈推荐的,特别是对高速信号(明确了关键走内层)

- 可以的话建议针对电源安排单独的电源层

- 建议电源层紧邻地层

器件放置

- 尽可能主芯片的存储接口,越短的走线可以为设计提供更多优势

- 根据主控芯片的出现顺序放置UFS方向

- 为简化设计,允许将相同电压等级的电源轨进行合并,但必须确保每个器件/封装附近就近布置去耦电容,以降低任意相位下的电源噪声耦合。

- 尽可能使用多个不同容值的电源/去耦电容组合,这有助于降低等效串联电感。

- 去耦电容应尽量靠近UFS2.x器件的电源引脚/焊球放置,以缩短芯片到电容的串联电感路径。

- 在最佳位置(即均匀分布区域)增设去耦电容,可有效抑制结构谐振并降低电磁干扰(辐射发射)。

- 采用低等效串联电感电容有助于最小化引线电感。

电源层和地层

- 电源层需要覆盖UFS的所有电源脚

- 强烈建议将地平面(GND)整合为统一网络。

- 每个电源脚和GND的脚都通过过孔连接

- IO power 层尽量覆盖覆盖所有信号线,如果其在相邻层

- 电源平面尽量不需要在GND层,如果是这样,必须特别注意避免信号线跨分割

- 避免电源层相邻

- 同层电源层的不同电源网络避免过于紧密,会造成噪声耦合

- 电源和GND网络尽可能短

走线要求

- 在过孔、走线和电容器焊盘之间使用宽而短的走线

- 差分数据和CLK线需要优先布线,并且必须走在内层

- 三星推荐:所有信号线放在第二层或第三层,这取决于叠层设计,如第二层是GND,那就建议信号线走在第三层,反之亦然

- 如果顶层需要走线,那么可以把除了差分数据线、CLK的线放置在顶层

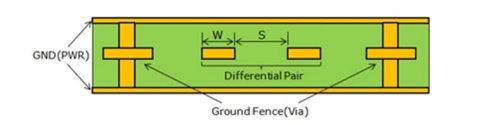

- 推荐差分数据线和CLK线需要包地,并且每隔3mm打地过孔

- 确保焊盘、走线到电源及GND过孔或铜皮尽可能远,至少保持2W

- 增加额外过孔(从每个焊盘到主电源/地平面),这能起到拓宽被动元件电流路径的效果,特别是去耦电容

- 使组内走线长度匹配,必要时可采用蛇形走线

- 保持走线连续性最小中断比走线长度匹配更为重要(尽可能少穿层)

- 避免因密集过孔造成平面切割或孔洞,这种情况容易发生在封装焊球下方区域

- 确保将所有接地走线连接到接地层。切勿遗漏任何悬空的形状和孤立的接地形状

- 若无法与接地平面连接,则移除孤立的接地形状

- 建议在信号走线区域和电源子平面区域周围布置接地屏蔽过孔,以隔离来自其他元件的噪声耦合

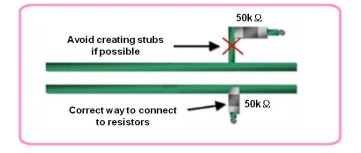

- 若使用上拉电阻,通往无源元件的走线也必须尽可能缩短,以减少由走线形成的支线长度,这种支线会因反射导致信号失真。示意如下:

- 开启主机控制器或UFS2.x控制器的片上上拉电阻,且不要在硬件复位引脚使用表面贴装技术上拉电阻。若实在无法避免,则在硬件复位引脚连接50千欧上拉电阻。

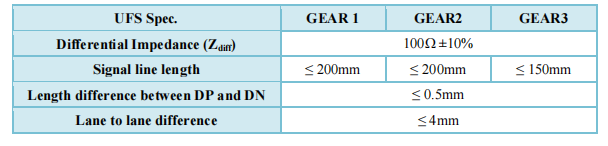

- 为确保差分对具备适当的信号完整性特性,插入损耗、阻抗匹配和长度平衡(偏斜)至关重要。下表总结了印刷电路板上推荐的最大信号走线长度与偏斜(DOUT_T与DOUT_C之间或DIN_T与DIN_C之间的走线长度失配)参数,其中信号长度限制适用于UFS默认均衡器设置的使用场景。

- 信号线下方(及上方)需保持完整参考地平面

- 将差分信号对的阻抗设置为100Ω(如有可能,建议将差分阻抗控制在略低于/不大于100Ω)

- 沿对称差分走线全程保持传输线阻抗均匀性,避免任何不连续

- 差分走线和参考时钟线应与其他信号线分层布线,避免串扰等不良耦合;若无法分层布线,需采用至少2倍线宽(W:信号线宽度)的地隔离带,并每隔3mm布置地过孔。具体参见下图

- 尽量保持差分走线平直。如需弯曲,应使用双45/135度折线或弧形走线替代直角弯曲

- 尽量减少使用多层信号层布线时的层间切换,因为这会导致意外的阻抗变化。

- 当必须进行层间切换时,应在差分对的过孔对旁放置连接接地层的接地过孔。(增加地回流过孔)

- 尽可能使用埋孔以避免通孔产生的残桩效应。若无法避免过孔残桩形成,应尽量缩短残桩长度。过孔残桩实际上会引发诸多不良问题及反射波失真(残桩越长,影响越严重)。

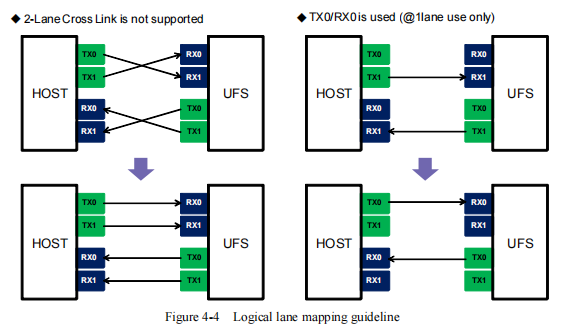

- 若仅需使用1通道,必须仅使用TX0/RX0引脚,同时将TX1/RX1引脚保持为NC状态,以防止主机出现通道映射错误,如下图所示。(SAMSUNG UFS)

PDN设计原则

电源分配网络(PDN)旨在为所有器件提供稳定均衡的电压。PDN(包含电源与地回路,通常称为"电源噪声")的电压波动会显著影响数字信号的时序完整性,表现为抖动和信号畸变,同时也是共模辐射导致电磁干扰(EMI)的潜在源头。PDN还承担着信号互连电流返回路径的基准参考功能。

PDN设计必须确保在目标频段内(通常以转折频率为基准)保持低阻抗特性。电流具有优先选择最低阻抗路径的特性——直流模式下最低阻抗表现为最小电阻,交流模式下则体现为最小回路电感。因此,返回路径的任何不连续性都将导致阻抗升高。

针对高速系统日益重要的PDN设计,推荐以下准则:

- 所有信号建议采用统一地平面作为参考基准,走线区域下方参考层应保持完整,避免分割、开槽或设置大型过孔

- 建议在PCB叠层中尽可能采用紧密耦合的平行板结构

- 不同电源域之间需设置最小2倍线宽(2W)的地隔离带

- 每隔3mm布置地过孔连接隔离带与内部地平面

- 确保电源层保持完整(子平面结构)。若必须走线,电源走线宽度应≥0.3mm以降低直流电阻与电感,并尽量缩短走线长度

- 布置多个电源/地过孔,通过并联路径降低回路电感

- 避免信号参考平面切换。不可避免时,需增设过孔和去耦电容提供临近返回路径

- 电源与地应相邻布置,通过反向电流产生的互感效应降低总电感

测点布置

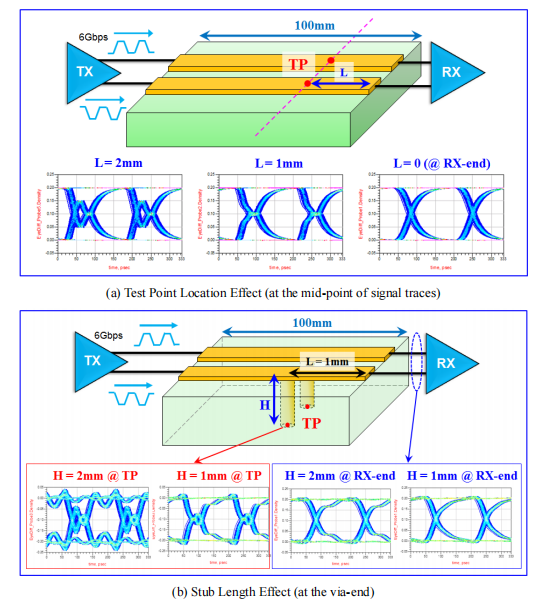

在使用测试点作为差分输入/输出对时,需考虑测试点位置和支线长度对信号完整性的影响,建议遵循以下设计准则:

- 将接收端引脚至测试点的走线长度控制在最短

- 尽可能降低通孔高度以减少Stub效应

埋孔设计

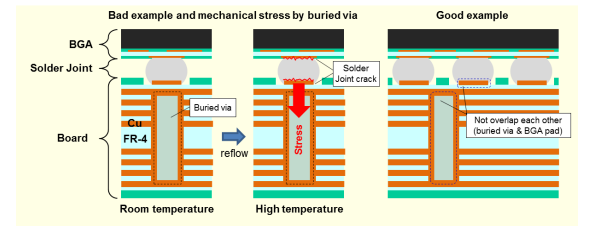

下图展示了在BGA焊盘下方使用埋孔的错误示例及改进建议。

BGA焊盘下方的埋孔会导致焊点处产生机械应力,从而在SMT工艺过程中引发裂纹失效。

这种机械应力的根源在于埋孔填充材料与FR-4基板之间Z轴热膨胀系数(CTE)的不匹配。

随着板材厚度的增加(即埋孔长度增大),机械应力会进一步增强。

- 建议避免将埋孔直接置于BGA焊盘正下方,确保BGA焊盘与埋孔不发生重叠。

验证

- 如有可能,建议通过仿真验证设计特性

- 根据仿真结果调整设计方案,去耦电容器可在实际装置测试后进行调节