Xilinx FPGA 重构Multiboot ICAPE2和ICAPE3使用

一、FPGA Multiboot

本文主要介绍基于IPROG命令的FPGA多版本重构,用ICAP原语实现在线多版本切换。需要了解MultiBoot Fallback点击链接。

如下图所示,ICAP原语可实现flash中n+1各版本的动态切换,在工作过程中,可以通过IPROG命令切换到其他任意版本所在地址运行。

二、ICAPE2

参考Xilinx ug470,ICAPE2原语如下:

ICAPE2 #(.DEVICE_ID(32'h3651093), // Specifies the pre-programmed Device ID value to be used for simulation// purposes..ICAP_WIDTH("X32"), // Specifies the input and output data width..SIM_CFG_FILE_NAME("NONE") // Specifies the Raw Bitstream (RBT) file to be parsed by the simulation// model.)ICAPE2_inst (.O(O), // 32-bit output: Configuration data output bus.CLK(CLK), // 1-bit input: Clock Input.CSIB(CSIB), // 1-bit input: Active-Low ICAP Enable.I(I), // 32-bit input: Configuration data input bus.RDWRB(RDWRB) // 1-bit input: Read/Write Select input);

DEVICE_ID:需要和芯片ID匹配,可以在ug470查询,也可以用过JTAG获取

各引脚定义如下:

O:回读的config数据

CLK:操作时钟

CSIB:使能端,低有效

I:输入的配置数据

RDWRB:读写控制端,1-读,0-写

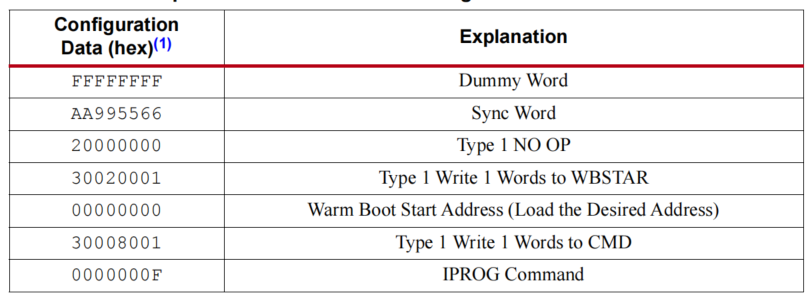

ICPE实现multiboot的配置流程如下,在使能后,以此每个时钟输入以下命令,其中Warm Boot Start Address为需要跳转的地址

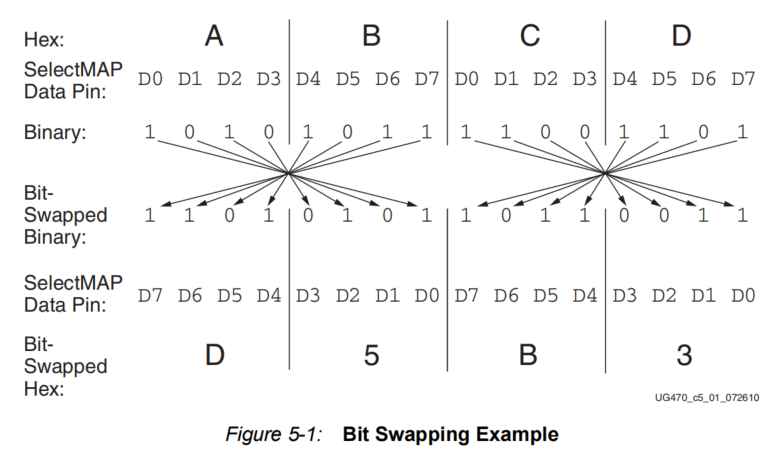

需要注意的是,输入的配置数据字节内需进行bit swap,例如:

三、ICAPE3

参考Xilinx ug570,ICAPE3如下:

ICAPE3 #(.DEVICE_ID(32'h03628093), // Specifies the pre-programmed Device ID value to be used for simulation// purposes..ICAP_AUTO_SWITCH("DISABLE"), // Enable switch ICAP using sync word..SIM_CFG_FILE_NAME("NONE") // Specifies the Raw Bitstream (RBT) file to be parsed by the simulation// model.)ICAPE3_inst (.AVAIL(AVAIL), // 1-bit output: Availability status of ICAP..O(O), // 32-bit output: Configuration data output bus..PRDONE(PRDONE), // 1-bit output: Indicates completion of Partial Reconfiguration..PRERROR(PRERROR), // 1-bit output: Indicates error during Partial Reconfiguration..CLK(CLK), // 1-bit input: Clock input..CSIB(CSIB), // 1-bit input: Active-Low ICAP enable..I(I), // 32-bit input: Configuration data input bus..RDWRB(RDWRB) // 1-bit input: Read/Write Select input.);

DEVICE_ID:需要和芯片ID匹配,可以在ug470查询,也可以用过JTAG获取

各引脚定义如下:

AVAIL:回读有效标志

PRDONE:重购完成标志

PRERROR:重构失败标志

O:回读的config数据

CLK:操作时钟

CSIB:使能端,低有效

I:输入的配置数据

RDWRB:读写控制端,1-读,0-写

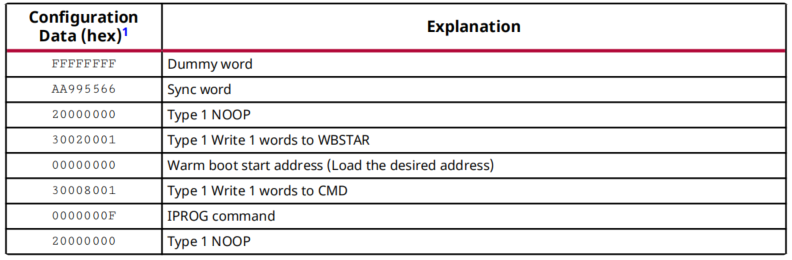

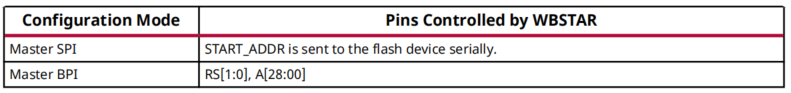

ICPE实现multiboot的配置流程如下,在使能后,以此每个时钟输入以下命令,其中Warm Boot Start Address为需要跳转的地址

在BPI重构是,配置地址有所区别,需增加一个RS控制。

与ICAPE2相同,ICAPE3输入的配置数据字节内需进行bit swap。

三、ICAPE3例程

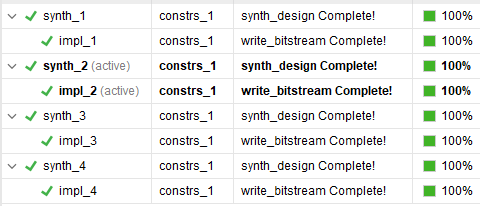

下面基于ICAPE3,设计了4个image重构例程。

1、输入输出

采用一个25MHz时钟,输出LED用于判断是那个image,同时可以通过VIO判断image

module Multiboot_top(

//---------------------------全局信号--------------------------------------------- input i_FPGA_GCLK25M , // 板载晶振输出output reg o_FPGA_TEST_LED

);

2、image配置及状态

(1)通过一个VIO配置不同image的跳转,跳转地址32bit,跳转使能触发状态机进行跳转,同时可用过VIO观测不同的image

(2)通过条件编译例化4个综合实现选项,输出4个bit

(3)通过LED的闪烁次数观察不同的image

`ifdef B2

localparam IMAGE_NUM = 2'd1;

`elsif B3

localparam IMAGE_NUM = 2'd2;

`elsif B4

localparam IMAGE_NUM = 2'd3;

`else

localparam IMAGE_NUM = 2'd0;

`endif

localparam CLK_CNT_MAX = 32'd6250000;

//------------------led image --------------

reg [31:0] clk_cnt;

reg [2:0] led_num;

always @(posedge i_FPGA_GCLK25M) beginif(clk_cnt == CLK_CNT_MAX) beginclk_cnt <= 32'd0;led_num <= led_num + 1'b1;endelse clk_cnt <= clk_cnt + 1'b1;

end

//1S内闪烁IMAGE_NUM+1次,停1S,依次循环

always @(posedge i_FPGA_GCLK25M) beginif(clk_cnt <= CLK_CNT_MAX/2 && led_num <= IMAGE_NUM) o_FPGA_TEST_LED <= 1'b1;else o_FPGA_TEST_LED <= 1'b0;

end

//------------------vio image --------------

wire reboot_valid;

wire [31:0] reboot_addr;

vio_0 vio_image (.clk(i_FPGA_GCLK25M), // input wire clk.probe_in0(IMAGE_NUM), // input wire [1 : 0] probe_in0.probe_out0(reboot_valid), // output wire [0 : 0] probe_out0.probe_out1(reboot_addr) // output wire [31 : 0] probe_out1

);

3、ICAPE3实现IPROG重构

//------------------image exchange--------------

wire ICAPE_CLK;

wire [31:0] ICAPE_O;

reg ICAPE_CSIB;

wire [31:0] ICAPE_I;

reg ICAPE_RDWRB;localparam [31:0] Dummy = 32'hFFFFFFFF;

localparam [31:0] SYNC_WORD = 32'hAA995566;

localparam [31:0] NOOP = 32'h20000000;

localparam [31:0] WR_WBSTAR = 32'h30020001;

localparam [31:0] WR_CMD = 32'h30008001;

localparam [31:0] IPROG = 32'h0000000F;ICAPE3 #(.DEVICE_ID(32'h04AC2093), // Specifies the pre-programmed Device ID value to be used for simulation// purposes..ICAP_AUTO_SWITCH("DISABLE"), // Enable switch ICAP using sync word..SIM_CFG_FILE_NAME("NONE") // Specifies the Raw Bitstream (RBT) file to be parsed by the simulation// model.)ICAPE3_multiboot (.AVAIL (AVAIL ), // 1-bit output: Availability status of ICAP..O (ICAPE_O ), // 32-bit output: Configuration data output bus..PRDONE ( ), // 1-bit output: Indicates completion of Partial Reconfiguration..PRERROR ( ), // 1-bit output: Indicates error during Partial Reconfiguration..CLK (ICAPE_CLK ), // 1-bit input: Clock input..CSIB (ICAPE_CSIB ), // 1-bit input: Active-Low ICAP enable..I (ICAPE_I ), // 32-bit input: Configuration data input bus..RDWRB (ICAPE_RDWRB ) // 1-bit input: Read/Write Select input.);

assign ICAPE_CLK = i_FPGA_GCLK25M;wire [31:0] WBSTAR ;

assign WBSTAR = reboot_addr;//ICAPE位翻转

reg [31:0] wrdat;

assign ICAPE_I = {wrdat[24], wrdat[25], wrdat[26], wrdat[27], wrdat[28], wrdat[29], wrdat[30], wrdat[31], wrdat[16], wrdat[17], wrdat[18], wrdat[19], wrdat[20], wrdat[21], wrdat[22], wrdat[23], wrdat[8], wrdat[9], wrdat[10], wrdat[11], wrdat[12], wrdat[13], wrdat[14], wrdat[15], wrdat[0], wrdat[1], wrdat[2], wrdat[3], wrdat[4], wrdat[5], wrdat[6], wrdat[7]};reg [1:0] reboot_valid_r;

reg [3:0] send_cmd_cnt = 4'hf;always @(posedge i_FPGA_GCLK25M) reboot_valid_r = {reboot_valid_r[0], reboot_valid};

always @(posedge i_FPGA_GCLK25M) beginif(reboot_valid_r == 2'b01) send_cmd_cnt <= 4'd0;else if(send_cmd_cnt != 4'hf) send_cmd_cnt <= send_cmd_cnt + 1'b1;

endalways @(posedge i_FPGA_GCLK25M) begincase(send_cmd_cnt)4'd0: begin //DUMMYwrdat <= Dummy;ICAPE_CSIB <= 1'b0;ICAPE_RDWRB <= 1'b0;end4'd1: begin //SYN_WORDwrdat <= SYNC_WORD;ICAPE_CSIB <= 1'b0;ICAPE_RDWRB <= 1'b0;end4'd2: begin //NOOP1wrdat <= NOOP;ICAPE_CSIB <= 1'b0;ICAPE_RDWRB <= 1'b0;end4'd3: begin //WR_WBSTARwrdat <= WR_WBSTAR;ICAPE_CSIB <= 1'b0;ICAPE_RDWRB <= 1'b0;end4'd4: begin //WBSTARwrdat <= WBSTAR;ICAPE_CSIB <= 1'b0;ICAPE_RDWRB <= 1'b0;end4'd5: begin //WR_CMDwrdat <= WR_CMD;ICAPE_CSIB <= 1'b0;ICAPE_RDWRB <= 1'b0;end4'd6: begin //IPROGwrdat <= IPROG;ICAPE_CSIB <= 1'b0;ICAPE_RDWRB <= 1'b0;end4'd7: begin //NOOP2wrdat <= NOOP;ICAPE_CSIB <= 1'b0;ICAPE_RDWRB <= 1'b0;end4'd8: begin //STOPwrdat <= 32'd0;ICAPE_CSIB <= 1'b1;ICAPE_RDWRB <= 1'b1;enddefault: beginwrdat <= 32'd0;ICAPE_CSIB <= 1'b1;ICAPE_RDWRB <= 1'b1;endendcase

end

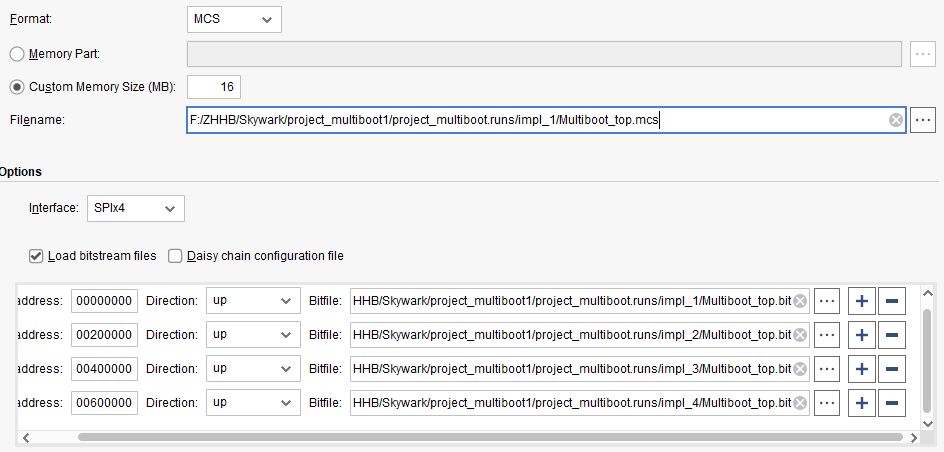

4、mcs文件生成

如下图所示设置地址和bit,生成mcs并烧写flash

5、mcs烧写及切换

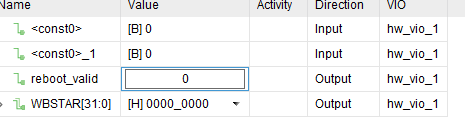

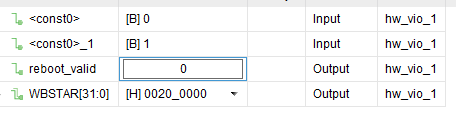

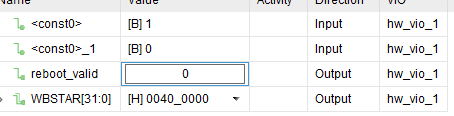

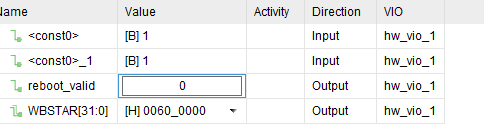

mcs烧写完成后,通过VIO配置相应启动地址,产生使能完成重加载,VIO配置加载后观察IMAGE ID如下:

(1)addr=0

(2)addr=0x00200000

(3)addr=0x00400000

(4)addr=0x00600000

参考工程请点击

链接:https://download.csdn.net/download/u014035968/90962933

参考文件

ug570-ultrascale-configuration

ug470-7Series-configuration