4H-SiC 射频功率MESFET 的表面态分析

4H-SiC 功率MESFET 的制造工艺流程与GaAsFET 工艺有相似之处,但其工艺难度很大,因此,目前,国际上也仅有少数几个研究机构能够涉足其制造领域。

从目前的SiC MESFET 制造工艺分析,主要存在几个难点

1.高温处理工艺,若有离子注入环节,退火温度需达到1500℃ 以上,欧姆接触合金工艺也在1000℃左右。

2.刻蚀工艺,目前对SiC 只能采用干法刻蚀,如反应离子刻蚀(RIE)、等离子刻蚀(Plasma),这就造成了刻蚀面的损伤,大大增加了表面粗糙度,需SacOx(Sacrificial thermal Oxidation)和ICP(Inductively Coupled Plasma)的后处理工艺将表面损伤降到最低,但这种处理在器件栅区的微细加工时有一定的难度。

另外,对于大功率器件,为了提高击穿电压指标,除在结构上采取一些措施外,器件表面钝化是必需的,但钝化处理有可能增加表面态密度,对功率及频率特性也会造成负面影响,因此,在大功率器件模型中必须考虑由材料本身或由工艺造成的表面态增加的因素,使模型更合理地描述器件工作状态。

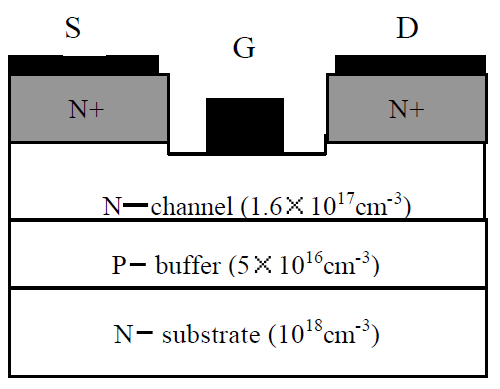

采用凹陷栅工艺的4H-SiC 功率MESFET结构如下图所示。

4H-SiC MESFET主要有以下几个工艺步骤:有源区隔离台面形成,栅区和源漏岛形成,源漏岛欧姆接触形成,栅金属接触形成,互连金属及空气桥形成。

制备材料一般为n /p/n /n+多层外延结构,或由离子注入形成多层结构,在上述工艺中需要刻蚀形成台面和凹陷栅区(recess- gate region)。

由于4H-SiC 只能采用干法刻蚀工艺,在刻蚀面会形成一定的晶格损伤,使表面态增加,特别在凹陷栅区,会造成明显的影响:在栅下可造成Schottky 势垒的变化,在非栅下区(特指栅源间距和栅漏间距)可造成源漏电阻的增加,而在整个沟道区可造成横向迁移率电场等重要参数的变化。所有这些最终导致器件输出特性的退化。