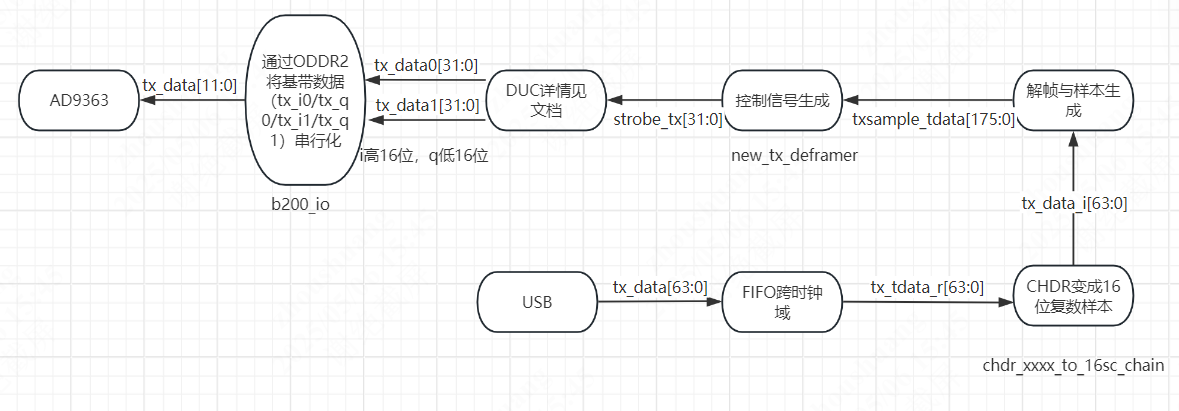

USRP B210 TX_IQ处理

文章目录

- FIFO模块

- chdr_xxxx_to_16sc_chain模块

- new_tx_deframer模块

- new_tx_control模块

- DUC模块

- 1、数据拆分:I/Q 通道分离

- 2、两级半带插值滤波

- 3、 CIC 插值滤波

- 4、 数字上变频(NCO 混频)

- 5、 增益调整与限幅

- 6. 输出映射

- tx_responder模块

- b200_io模块

FIFO模块

tx_tdata(64 位,USB传输过来,总线时钟域bus_clk)通过FIFO同步到射频时钟域radio_clk,tx_tdata_r

chdr_xxxx_to_16sc_chain模块

将 64 位 CHDR 格式的tx_tdata_r转换为 16 位复数样本格式,tx_data_i[63:0](实部 + 虚部各 16 位)

new_tx_deframer模块

解帧与样本生成:

将格式化后的数据流解包为样本数据txsample_tdata(176 位,包含多样本信息)。

生成txsample_tvalid(样本有效)和txsample_tready(准备好接收样本)信号。

new_tx_control模块

根据配置寄存器(SR_TX_CTRL)生成控制信号:

sample[31:0]:选通样本数据进入 DUC 链。

生成序列编号seqnum、源 IDsid等元数据,用于响应生成

DUC模块

输入32位sample[31:0]数据

1、数据拆分:I/Q 通道分离

sample 的高 16 位和低 16 位分别对应 I 通道 和 Q 通道 的基带信号:

// 从sample中提取I/Q数据(各16位,扩展为18位定点数)

hb47_int hb1_i0 (.data_in({sample[31:16], 2'b00}), // I通道:高16位 + 2位零扩展(18位)...

);

hb47_int hb1_q0 (.data_in({sample[15:0], 2'b00}), // Q通道:低16位 + 2位零扩展(18位)...

);

- sample[31:16]:I 通道原始数据(16 位),扩展为 18 位定点数(补 2 位 0)。

- sample[15:0]:Q 通道原始数据(16 位),扩展为 18 位定点数(补 2 位 0)。

2、两级半带插值滤波

第一级半带插值滤波:

hb_interp #(.IWIDTH(18),.OWIDTH(18),.ACCWIDTH(WIDTH)) hb_interp_i (.clk(clk), .rst(rst), .bypass(~enable_hb1), //enable_hb1=0,直接输出输入数据.cpo(cpo), // 插值速率.stb_in(strobe_hb1), .data_in({sample[31:16], 2'b0}), // I通道输入.stb_out(strobe_hb2), .data_out(hb1_i) // 第一级滤波后的I通道数据(18位)

);

// Q通道同理,处理sample低16位

- cpo = enable_hb2 ? ({interp_rate,1’b0}) : interp_rate

插值速率interp_rate由ctrl_tdata通过USB总线传输过来

第二级半带插值滤波:

small_hb_int #(.WIDTH(18)) small_hb_interp_i (.clk(clk), .rst(rst), .bypass(~enable_hb2), //若enable_hb2=0,直接输出输入数据.stb_in(strobe_hb2), .data_in(hb1_i), // 第一级滤波后的I通道数据(18位).output_rate(interp_rate), // 最终插值速率(8位,决定过采样倍数).stb_out(strobe_cic), .data_out(hb2_i) // 第二级滤波后的I通道数据(18位)

);

// Q通道同理

3、 CIC 插值滤波

进一步提高采样率,支持大倍数过采样(最大 128 倍)

cic_interp_i (.signal_in(hb2_i), // 第二级半带滤波后的I通道数据(18位).signal_out(i_interp), //CIC插值后的I通道数据(18位)

);

cic_interp_q (.signal_in(hb2_q), // 第二级半带滤波后的Q通道数据(18位).signal_out(q_interp), // CIC插值后的Q通道数据(18位)

);

4、 数字上变频(NCO 混频)

通过 CORDIC 算法 实现正交混频,将基带信号搬移到目标载波频率:

//zwidth = 24;

cordic_z24 cordic (.xi({i_interp, {(cwidth-18){1'b0}}}), // I通道数据扩展为24位.yi({q_interp, {(cwidth-18){1'b0}}}), // Q通道数据扩展为24位.zi(phase[31:32-zwidth]), // NCO相位 32位相位累加器.xo(da_c), // 混频后的I通道信号(24位).yo(db_c), // 混频后的Q通道信号(24位)

);

5、 增益调整与限幅

增益调整:

// I通道增益调整

mult_i (.A(da_c[23:6]), .B(scale_factor), .P(prod_i)); // 截取24位中的高18位相乘

// Q通道增益调整

mult_q (.A(db_c[23:6]), .B(scale_factor), .P(prod_q));//prod_i\prod_q为36位

scale_factor[17:0]同样是由ctrl_tdata通过USB总线传输过来

setting_reg #(.my_addr(BASE+1), .width(18)) sr_1(.clk(clk),.rst(rst),.strobe(set_stb),.addr(set_addr),.in(set_data),.out(scale_factor),.changed());

限幅处理:

确保不超过前端输入范围

clip_i (.in(prod_i[35:0]), .out(i_clip)); // 36位输入 → 33位输出

clip_q (.in(prod_q[35:0]), .out(q_clip));

6. 输出映射

最终,限幅后的 33 位信号被截取为 WIDTH 位( 24 位),输出到模拟前端:

assign tx_fe_i = i_clip[32:33-WIDTH]; // 截取高WIDTH位(24位)

assign tx_fe_q = q_clip[32:33-WIDTH];

tx_responder模块

24 位 I/Q 信号的高 16 位([23:8])赋值给tx输出:

always @(posedge radio_clk) begintx[31:16] <= (run_tx) ? tx_fe_i[23:8] : tx_idle[31:16];tx[15:0] <= (run_tx) ? tx_fe_q[23:8] : tx_idle[15:0];end

根据 TX 处理结果(如 ACK / 错误码)生成响应包txresp_tdata_r。

包含序列编号seqnum、错误码error_code等元数据,用于反馈给主机。

b200_io模块

通过ODDR2将基带数据(tx_i0/tx_q0/tx_i1/tx_q1)串行化tx_codec_d[11:0]然后发送给AD9363