学习笔记msp430f5529lp

注:本文仅用于个人学习使用,记录笔记。

学习视频msp430f5529库函数入门教程 00.序言_哔哩哔哩_bilibili

向大佬致敬@理工男小帅-CSDN博客

CCS环境快捷键使用

代码注释:Ctrl+/ 提示/补全: Ctrl+Shift+C

放大:Ctrl++ 缩小:Ctrl+-

切换选择模式(列/竖向选择):Ctrl+Shift+A

*需要自己设置快捷键:Window -> preferences -> Editors -> Keys

GPIO

GPIO(General Purpose Input Output):

1.输出模式下可控制端口输出高低电平,用以驱动LED、控制蜂鸣器、模拟通信协议输出时序等

2.输入模式下可读取端口的高低电平或电压,用以读取按键输入、外接模块电平信号输入、ADC电压采集、模拟通信协议接收数据等

OLED+软件IIC

//由于I2C需要开漏输出(高电平无驱动能力:释放总线(I2C系统中已经配备上拉电阻))

//但是msp430没有,所以使用 “将引脚配置为输入模式(或上拉模式)” 来模拟

oled引脚配置:

#define SCL_PORT GPIO_PORT_P8

#define SCL_PIN GPIO_PIN2

#define SDA_PORT GPIO_PORT_P8

#define SDA_PIN GPIO_PIN1

UCS:430的时钟树

Unified Clock System (UCS) Introduction

The UCS module supports low system cost and ultra-low power consumption. Using three internal clock signals, the user can select the best balance of performance and low power consumption. The UCS module can be configured to operate without any external components, with one or two external crystals, or with resonators, under full software control. The UCS module includes up to five clock sources:

• XT1CLK: Low-frequency or high-frequency oscillator that can be used either with low-frequency 32768 Hz watch crystals, standard crystals, resonators, or external clock sources in the 4 MHz to 32 MHz range. XT1CLK can be used as a clock reference into the FLL. Some devices only support the low frequency oscillator for XT1CLK. See the device-specific data sheet for supported functions.

• VLOCLK: Internal very low power, low-frequency oscillator with 10-kHz typical frequency

• REFOCLK: Internal trimmed low-frequency oscillator with 32768-Hz typical frequency, can be used as a clock reference into the FLL

• DCOCLK: Internal digitally controlled oscillator (DCO) that can be stabilized by the FLL

• XT2CLK: Optional high-frequency oscillator that can be used with standard crystals, resonators, or external clock sources in the 4 MHz to 32 MHz range. XT2CLK can be used as a clock reference into the FLL.

Three clock signals are available from the UCS module:

• ACLK: Auxiliary clock. The ACLK is software selectable as XT1CLK, REFOCLK, VLOCLK, DCOCLK, DCOCLKDIV, and when available, XT2CLK. DCOCLKDIV is the DCOCLK frequency divided by 1, 2, 4, 8, 16, or 32 within the FLL block. ACLK can be divided by 1, 2, 4, 8, 16, or 32. ACLK/n is ACLK divided by 1, 2, 4, 8, 16, or 32 and is available externally at a pin. ACLK is software selectable by individual peripheral modules.

• MCLK:Master clock. MCLK is software selectable as XT1CLK, REFOCLK, VLOCLK, DCOCLK, DCOCLKDIV, and when available, XT2CLK. DCOCLKDIV is the DCOCLK frequency divided by 1, 2, 4, 8, 16, or 32 within the FLL block. MCLK can be divided by 1, 2, 4, 8, 16, or 32. MCLK is used by the CPU and system.

• SMCLK: Subsystem master clock. SMCLK is software selectable as XT1CLK, REFOCLK, VLOCLK, DCOCLK, DCOCLKDIV, and when available, XT2CLK. DCOCLKDIV is the DCOCLK frequency divided by 1, 2, 4, 8, 16, or 32 within the FLL block. SMCLK can be divided by 1, 2, 4, 8, 16, or 32. SMCLK is software selectable by individual peripheral modules

Power Management Module

可选参数:

PMM_CORE_LEVEL_O[Default]

PMM_CORE_LEVEL_1

PMM_CORE_LEVEL_2

PMM_CORE_LEVEL_3

使用/配置过程

1.根据想要配置的MCLK频率设置核心电平

2.初始化晶振对应引脚并起振

3.配置FLL(锁频环)

4.配置时钟树(主要是MCLK、SMCLK、ACLK)

5.记录外部时钟源频率

实验

实验一:

配置ACLK=4MHz,MCLK=SMCLK=25MHz,让OLED显示屏刷新加快

实验二:

配置ACLK=32768Hz,MCLK=SMCLK=24MHz,通过引脚输出,示波器观察

中断

中断定义:中断是暂停CPU正在运行的程序,转去执行相应的中断服务程序,完毕后返回被中断的程序继续运行的现象和技术

中断源:把引起中断的原因或者能够发出中断请求的信号源统称为中断源(外部硬件中断源和内部软件中断源,外部硬件中断源包括可屏蔽中断和不可屏蔽中断)

中断向量表:中断向量的地址是中断服务程序的入口地址的地址

中断优先级:......//断点和中断现场:......//

中断嵌套:msp430单片机会自动清除总中断允许标志位GIE,也就是说,msp430单片机的中断默认是不能发生嵌套的

中断响应过程

中断响应过程为从CPU接收一个中断请求开始至执行第一条中断服务程序指令结束,共需要6个时钟周期。中断响应过程如下:

① 执行完当前正在执行的指令;

② 将程序计数器(PC)压入堆栈,程序计数器指向下一条指令;

③ 将状态寄存器(SR)压入堆栈,状态寄存器保存了当前程序执行的状态;

④ 如果有多个中断源请求中断,选择最高优先级,并挂起当前的程序;

⑤ 清除中断标志位,如果有多个中断请求源,则予以保留等待下一步处理;

⑥ 清除状态寄存器SR,保留SCG0,因而CPU可从任何低功耗模式下唤醒;

⑦ 将中断服务程序入口地址加载给程序计数器(PC),转向执行中断服务子程序;

中断返回过程

通过执行中断服务程序终止指令(RETI)开始中断的返回,中断返回过程需要5个时钟周期,主要包含以下过程:

① 从堆栈中弹出之前保存的状态寄存器给SR;

② 从堆栈中弹出之前保存的程序计数器给PC;

③ 继续执行中断时的下一条指令。

**执行中断返回后,程序返回到原断点处继续执行,程序运行状态被恢复。假设中断发生前CPU处于某种休眠/低功耗模式下,中断返回后CPU仍然在该休眠模式下,程序执行将暂停;

__bis_SR_register(LPM3_bits + GIE); //进入低功耗模式3,且启用可屏蔽中断__bis_SR_register_on_exit(LPM3_bits); //退出低功耗模式3中断服务函数编写示例:

#pragma vector=PORT1_VECTOR //P1口中断向量__interrupt void Port_1 (void) //声明中断服务程序,名为Port_1

{ GPIO_clearInterrupt( XXX, XXX );//清除中断标志位 _EINT(); //恢复总的中断允许 ………//上面这两步顺序不能改变,否则将进入死循环 ………

}**MSP430单片机的中断源数量很多,比如P1,P2口每个IO口都能产生中断,16个ADC采样通道采样结束及遇到的错误也能产生中断。为了便于管理,MSP430单片机的中断管理机制把同类的中断合并成一个总中断源,具体的中断需要由软件查询中断标志位进行确定。例如,ADC的任何一个采样通道采样结束,程序都会执行ADC的中断服务程序,在ADC中断服务程序中,再查询相应标志位具体判断是哪一个通道采样结束发生了中断。

中断向量宏定义

中断向量宏定义.txt

定时器中断

timer_A

Timer_A is a 16-bit timer/counter with up to seven capture/compare registers. Timer_A can support multiple capture/compares, PWM outputs, and interval timing. Timer_A also has extensive interrupt capabilities. Interrupts may be generated from the counter on overflow conditions and from each of the capture/compare registers. Timer_A features include:

• Asynchronous 16-bit timer/counter with four operating modes

• Selectable and configurable clock source

• Uptoseven configurable capture/compare registers

• Configurable outputs with pulse width modulation (PWM) capability • Asynchronous input and output latching

• Interrupt vector register for fast decoding of all Timer_A interrupts

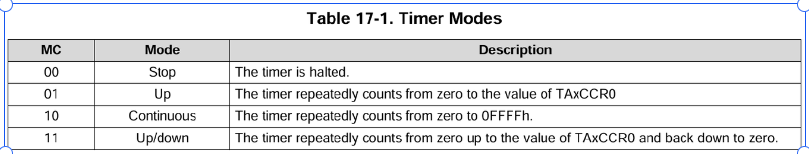

timer_A的四种工作模式

00:定时器暂停、并不复位,所有寄存器现行的内容在停止模式结束后都可用。当定时器暂停后重新计数时,计数器将从暂停时的值开始以暂停前的计数方向计数。TACLR可清除定时器的计数及方向

01:**占用了CCR0捕获比较寄存器,只有1~6可用

-

TAxCCR0的数值定义了定时的周期(可以不用是固定的0FFFFh)

-

TAR= TAxCCR0定时器复位并从0开始重新计数

-

TAR= TAxCCR0时CCR0中断标志位CCIFG=1

-

定时器从TAxCCR0计数到0时,置位Timer_A中断标志位TAIFG

10:用来:1、产生多个独立的时序信号;2、产生多个定时信号

-

周期固定为0~0FFFFh,TAxCCR0与其他捕获/比较寄存器工作方式相同

-

TAR= 0FFFFh定时器复位并从0开始重新计数

-

定时器从TAxCCR0计数到0时,置位Timer_A中断标志位TAIFG

11:

-

需要对称波形时

-

TAxCCR0的数值定义了定时的周期(可以不用是固定的0FFFFh)

-

TAR= TAxCCR0时CCR0中断标志位CCIFG=1

-

定时器计数到0时,置位Timer_A中断标志位TAIFG

timer_A中断

TAxCCRn中断 -> CCIFGn

TAxCCR0中断标志位CCIFG0在Timer_A中断中具有最高的中断优先级(看中断向量表),相应的TAxCCR0中断请求被响应后,TAxCCR0中断标志位CCIFG0自动复位

TAxIV中断 -> CCIFGn + TAIFG

包括除CCIFG0外的所有CCIFGn(当前计时器)中断和TAIFG中断标志。对TAxIV中断向量寄存器的读或写,都将自动清除挂起的最高优先级中断标志位。如果同时也置位了其他中断标志位,在当前中断服务程序执行完毕后,将自动立即响应新的中断请求。

-

在捕获模式下,当定时计数器TAR的值被捕获到TAxCCRn寄存器内时,置位相关的CCIFGn中断标志位。在比较模式下,当定时计数器TAR的值计数到TAxCCRn的值时,置位相关的CCIFGn中断标志位。也可利用软件置位或清除任意一个CCIFG中断标志位。

实验

1、使用UpMode + TAxCCR0中断,LED固定1s间隔闪烁(身边有示波器的同学可观察频率)

2、使用ContinuousMode + TAxIV中断,LED固定间隔(约0.5s)闪烁(身边有示波器的同学可观察频率)

TIMER_A模块的基地址:

TIMER_A0_BASE

TIMER_A1_BASE

TIMER_A2_BASE

timer_A的PWM输出

CAP位 = 0 时,捕获/比较模块工作在比较模式,比较模式常用来产生PWM信号或者在特定的时间间隔产生中断。此时TAxCCRn的值可由软件写入,并通过比较器与主计数器TAR值进行比较,当TAR计数到TAxCCRn时,将依次产生以下事件:

1、中断标志CCIFG置位

2、内部信号EQUn = 1

3、根据输出方式不同,EQUn根据不同的输出模式触发相应的输出逻辑

4、输入信号CCI锁存到SCCI。

每个输出单元都有8种工作模式,可产生EQUx的多种信号。输出模式可通过OUTMOD控制位进行定义,具体定义如表所示:《芯片技术参考手册》P469

实验

1、单定时器单PWM输出,按键可调占空比(需要示波器观察或外接LED)

2、单定时器多PWM输出(需要示波器观察或外接LED)

死区:死区就是在上半桥关断后,延迟一段时间再打开下半桥或在下半桥关断后,延迟一段时间再打开上半桥,从而避免功率元件烧毁。这段延迟时间就是死区。

The up/down mode supports applications that require dead times between output signals (see Section 17.2.5). For example, to avoid overload conditions, two outputs driving an H-bridge must never be in a high state simultaneously. In the example shown in Figure 17-9, the tdead is:

tdead = ttimer × (TAxCCR1– TAxCCR2)

Where:

tdead = Time during which both outputs need to be inactive

ttimer = Cycle time of the timer clock

TAxCCRn = Content of capture/compare register n

终于明白:什么是PWM“死区”!-电子工程专辑 (eet-china.com)

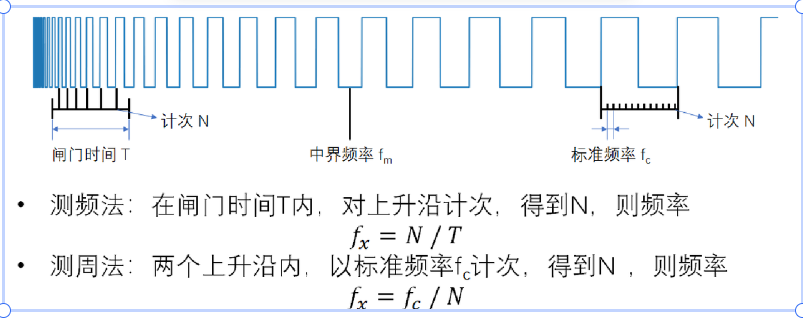

timer_A输入捕获

《msp430...芯片技术参考手册》P467

The capture mode is selected when CAP = 1. Capture mode is used to record time events. It can be used for speed computations or time measurements. The capture inputs CCIxA and CCIxB are connected to external pins or internal signals and are selected with the CCIS bits. The CM bits select the capture edge of the input signal as rising, falling, or both. A capture occurs on the selected edge of the input signal. If a capture occurs:

• The timer value is copied into the TAxCCRn register.

• The interrupt flag CCIFG is set.

The input signal level can be read at any time from the CCI bit. Devices may have different signals connected to CCIxA and CCIxB. See the device-specific data sheet for the connections of these signals. The capture signal can be asynchronous to the timer clock and cause a race condition. Setting the SCS bit synchronizes the capture with the next timer clock. Setting the SCS bit to synchronize the capture signal with the timer clock is recommended (see Figure 17-10).SCS这里推荐=1.

NOTE:

1.Changing Capture Inputs Changing capture inputs while in capture mode may cause unintended capture events. To avoid this scenario, capture inputs should only be changed when capture mode is disabled (CM = {0} or CAP = 0)

2. Overflow logic is provided in each capture/compare register to indicate if a second capture was performed before the value from the first capture was read. Bit COV is set when this occurs as shown in Figure 17 11. COV must be reset with software.

实验

1、捕获按键次数

实验1:

初始化选定的定时器

配置定时器为输入捕获模式

准备被捕获信号对应的引脚

编写中断服务函数

2、测量周期

实验二:

初始化选定的定时器

配置定时器为输入捕获模式

准备被捕获信号(一定频率方波)

编写中断服务函数

*定时器的信号连接表见《芯片数据手册》P65

*中断向量表见《芯片数据手册》P55

*中断向量宏定义: 云盘txt文档或者msp430f5529.h 4773行

USCI:UART

异步串行通信(UART)的特点:

1、传输7位或8位数据,可采用奇校验、偶校验或者无校验;

2、具有独立的发送和接收移位寄存器;

3、具有独立的发送和接收缓冲寄存器;

4、支持最低位优先或最高位优先的数据发送和接收方式;

5、内置多处理器系统,包括线路空闲和地址位通信协议;

6、通过有效的起始位检测将MSP430单片机从低功耗模式下唤醒;

7、可编程实现分频因子为整数或小数的波特率;

8、具有用于检测错误或排除错误的状态标志位;

9、具有用于地址检测的状态标志位;

10、具有独立的发送和接收中断能力;

USCI_Ax模块支持以下模式:

UART通信模式;

具有脉冲整形的IrDA通信模式;

具有自动波特率检测的LIN通信模式;

SPI通信模式。

USCI_Bx模块支持以下通信模式:

I2C通信模式;

SPI通信模式。

Initializing NOTE:

Initializing or reconfiguring the USCI module

The recommended USCI initialization/reconfiguration process is:

1. Set UCSWRST (BIS.B #UCSWRST,&UCAxCTL1) ,To avoid unpredictable behavior, configure or reconfigure the USCI_A module only when UCSWRST is set.

2. Initialize all USCI registers with UCSWRST = 1 (including UCAxCTL1).

3. Configure ports.

4. Clear UCSWRST via software (BIC.B #UCSWRST,&UCAxCTL1).

5. Enable interrupts (optional) via UCRXIE and/or UCTXIE.

波特率生成

USCI波特率发生器可以从非标准的时钟源频率中产生标准的波特率

1、产生低频波特率( UCOS16=0 低频模式)

-

允许从低频时钟源产生标准的波特率,比如32768产生9600bps波特率。

-

使用较低的输入频率,可以降低系统的功耗。

-

在高频输入下,该模式会降低多数表决法的优势。

-

波特率发生器使用1个预分频器和1个调制器产生时钟,支持小数分频

-

最大USCI波特率是UART时钟频率BRCLK的1/3

2、产生高频波特率( UCOS16=1 过采样模式)

-

支持在较高的输入时钟频率下产生较高的UART波特率

-

波特率发生器使用1个预分频器和1个调制器产生时钟,支持小数分频

-

该模式的参考时钟为BITCLK16,频率为BITCLK的1/16,故计算分频系数时需将波特率发生器的参考时钟频率除以16后再进行计算

-

最大的USCI波特率是UART源时钟频率的1/16

波特率的设置:

1、选择合适的时钟源(9600bps以下,可以选择ACLK作为时钟源,以上建议选择较高的SMCLK作为时钟源)

2、在某些特殊应用中,也可以使用外部的时钟输入作为波特率发生器的时钟源 UCAxCLK

3、分频因子 N = fBRCLK / f波特率 。分频因子N通常不是一个整数值,故系统中用一个分频器和一个调制器来尽可能接近分频因子。如果N等于或大于16,可以通过置位UCOS16选择过采样模式

1、低频波特率设置

预分频器 UCBRx = int(N) ; 调制器 UCBRSx = round((N-int(N))x8)

2、高频波特率设置

预分频器 UCBRx = int(N/16) ;调制器 UCBRFx = round(((N/16)-int(N/16))x16)

实验

1、串口收发实验(收到什么就发什么)

2、printf打印实验

*常用波特率配置表《芯片数据手册》P952

*本节库函数《函数库手册》P476

USCI_A_UART模块的基地址:

USCI_A0_BASE

USCI_A1_BASE

ADC

-

ADC理论工作原理: ADC在模拟信号转化为数字信号需要经过采样、保持、量化和编码。采样和保持在采样保持电路中完成,而量化和编码步骤则在ADC中完成;

-

ADC的位数:ADC的位数为ADC模块采样转换后输出结果的位数,如12位ADC采样转换后的输出结果为12位表示的数据,范围为0~4096;

-

分辨率: 分辨率表示输出数字量变化的一个相邻数码所需输入模拟电压的变化量,比如12位ADC若满刻度采样电压为5V(msp430f5: 3.3V),那最小分辨率为 5*(1/4096)=1.22mV

-

量化误差: 量化误差是由于用有限数字对模拟数值进行离散取值(量化)而引起的误差。量化误差是无法消除的,但是可以通过提高分辨率减少量化误差。

-

采样周期:采样周期是每两次采样之间的时间间隔,采样周期包括采样保持时间和转换时间。

-

采样频率:也称为采样速率或者采样率,定义为每秒从连续信号中提取并组成离散信号的采样个数,单位为赫兹(Hz)。采样频率的倒数是采样周期。实际使用中采样频率应为被采样信号中最高频率的5~10倍(理论是2倍_香农采样定理)

MSP430F5529 ADC12_A

特性包括:

最大转换速率超过 200 ksps(千次采样每秒)

单调的 12 位转换器,无丢失代码

带可编程采样周期的采样保持电路,可通过软件或定时器控制

可通过软件或定时器启动转换

软件可选择的片上参考电压生成(MSP430F54xx(仅非 A 系列):1.5 V 或 2.5 V,其他设备:1.5 V、2.0 V 或 2.5 V)

软件可选择内部或外部参考

最多 12 个单独可配置的外部输入通道

内部温度传感器、AVCC 和外部参考的转换通道

正负参考源均可独立选择通道

可选择的转换时钟源

单通道、重复单通道、序列(自动扫描)、重复序列(重复自动扫描)转换模式

ADC 核心和参考电压可以分别关闭

用于快速解码 18 个 ADC 中断的中断向量寄存器

16 个转换结果存储寄存器

有4种转换模式,可以通过CONSEQx位进行选择:

00:单通道单次转换

01:序列单通道单次转换

10:单通道多次转换

11:序列多通道多次转换

-

ADC内核采用可编程参考电压VR+、VR-作为转换上下限,最终转换结果满足 NADC=4095x(Vin - VR-)/(VR+ - VR-)

-

ADC控制位只能在ENC=0时被修改,转换发生前必须置1

-

模拟输入多路复用器,12路外部输入+4路内部输入

-

ADC参考电压可编程6种可选,内部参考模块不使用时可关闭降低功耗

-

包含16个结果缓冲寄存器、16个控制器寄存器。控制寄存器用于控制其相连的缓冲寄存器对应的输入通道与参考电压。正确配置后转换结果会自动存于结果缓冲寄存器

当采样触发信号SHI出现上升沿时将启动模数转换。可通过SHSx位选择,可选项有:ADC12SC(软件触发)、TA0_CCR1、TB0_CCR0、 TB0_CCR1(芯片数据手册P65)

The ADC12_A supports 8-bit, 10-bit, and 12-bit resolution modes selectable by the ADC12RES bits. The analog-to-digital conversion requires 9, 11, and 13 ADC12CLK cycles, respectively. The polarity of the SHI signal source can be inverted with the ADC12ISSH bit. The SAMPCON signal controls the sample period and start of conversion. When SAMPCON is high, sampling is active. The high-to-low SAMPCON transition starts the analog-to-digital conversion.

ADC12SHP定义了两种不同的采样时序方法:

扩展采样时序模式和脉冲采样时序模式(芯片技术参考手册P736)

The extended sample mode is selected when ADC12SHP = 0.

Set ADC12SHP = 1 to select the pulse sample mode.

注意:使用MSP430单片机片内的温度传感器时,采样周期必须大于30ms。温度传感器的偏移误差比较大,在大多数实际应用中需要进行校准。

实验

1:单通道单次转换&单通道多次转换

2:序列多通道单次转换&序列多通道多次转换

3:关于参考电压--讲解官方例程

*12-Bit ADC, Power Supply and Input Range Conditions、Timing Parameters 见《芯片数据手册》P44

*本节库函数《函数库手册》P53

ADC12模块的基地址:ADC12_A_BASE