SI5338-EVB Usage Guide(LVPECL、LVDS、HCSL、CMOS、SSTL、HSTL)

目录

1. 简介

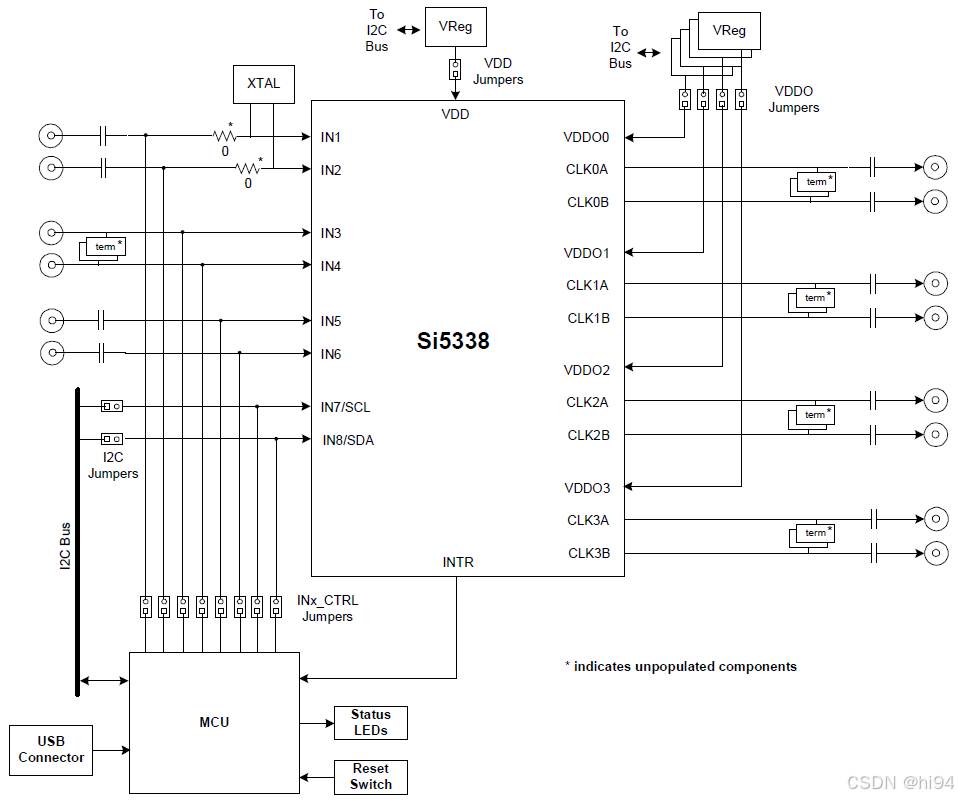

1.1 EVB 介绍

1.2 Si5338 Block Diagram

2. EVB 详解

2.1 实物图

2.2 基本配置

2.2.1 Universal Pin

2.2.2 IIC I/F

2.2.3 Input Clocks

2.2.4 Output Frequencies

2.2.5 Output Driver

2.2.6 Freq and Phase Offset

2.2.7 Spread Spectrum

2.2.8 快速参考手册

2.3 可编程电压

2.3.1 GUI 配置

2.3.2 原理解析

2.3.3 AD5263

2.3.4 MAX8869

2.4 供电

2.4.1 VDD

2.4.2 VDDOn

3. Si5338

3.1 Input Stage

3.1.1 Diagram

3.1.2 时钟输入

3.1.3 自由晶振

3.1.4 单端至差分

3.2 Output Stage

3.2.1 Diagram

3.2.2 Output CLK Info

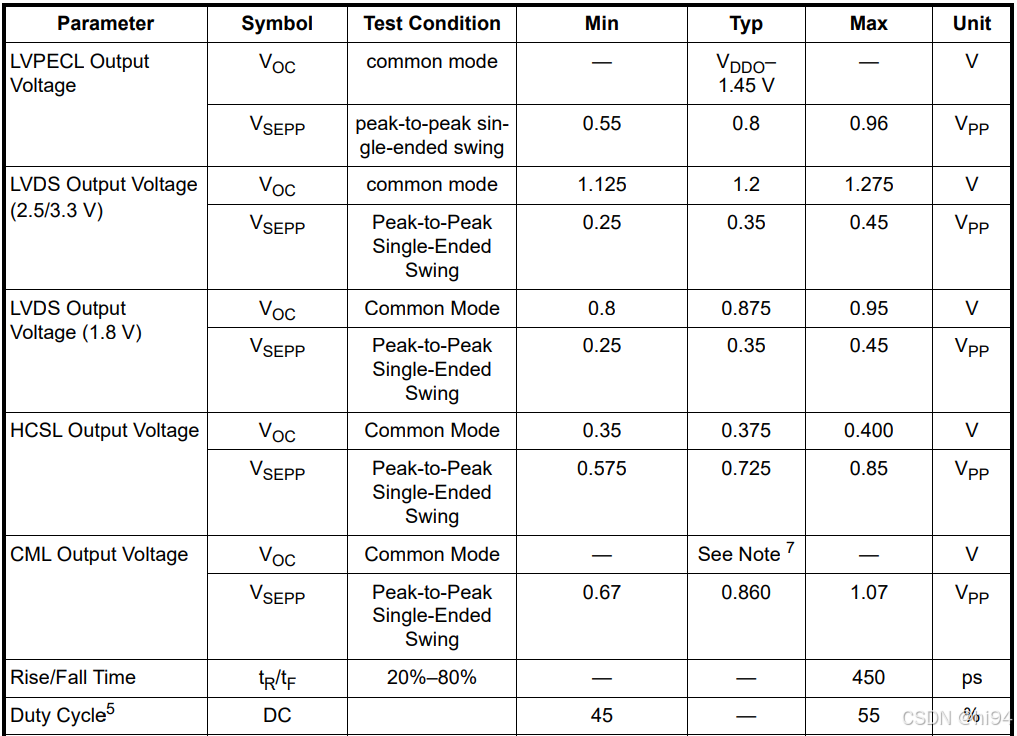

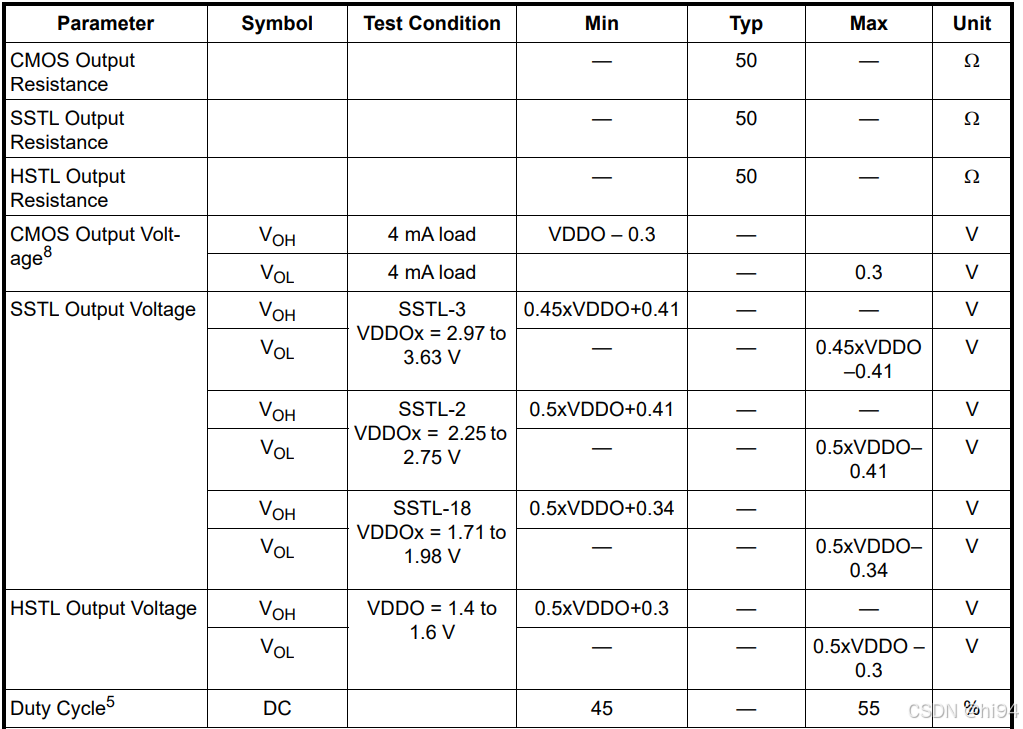

3.2.3 Output Volt Info

3.3 LVDS

3.4 ECL

3.4.1 ECL 系列

3.4.2 输入输出级

3.4.3 DC 耦合

3.4.4 AC 耦合

3.5 CML

3.6 HCSL

3.7 SSTL

3.8 HSTL

4. 总结

1. 简介

1.1 EVB 介绍

- EVB 包含一个 MCU,用于实现 USB 至 I2C 的信号转换,兼具电压调节器控制、中断引脚监测和四路状态 LED 控制功能。

- 当配置 INx_CTRL 跳线时,还可对八路输入引脚进行控制。板上设五组可编程电压调节器(含VDD、VDDO0-3),为 Si5338 芯片供电。

- VDD 和 VDDO 跳线可切换至外接电源供电模式,亦提供便捷的电流测量接入点。

- IIC 跳线可断开 EVB 与 Si5338 器件的总线连接,供其他 IIC 主控设备实施外部控制。

- EVB 板载 25MHz 晶振,支持独立异步工作模式。

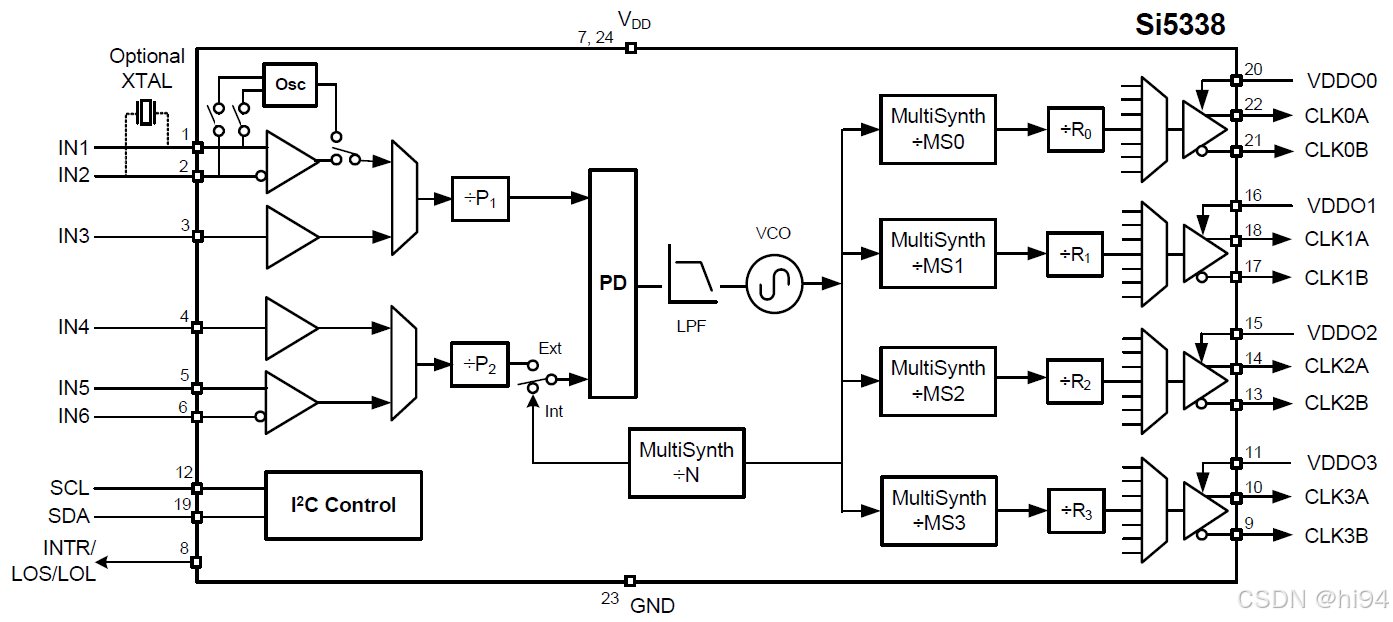

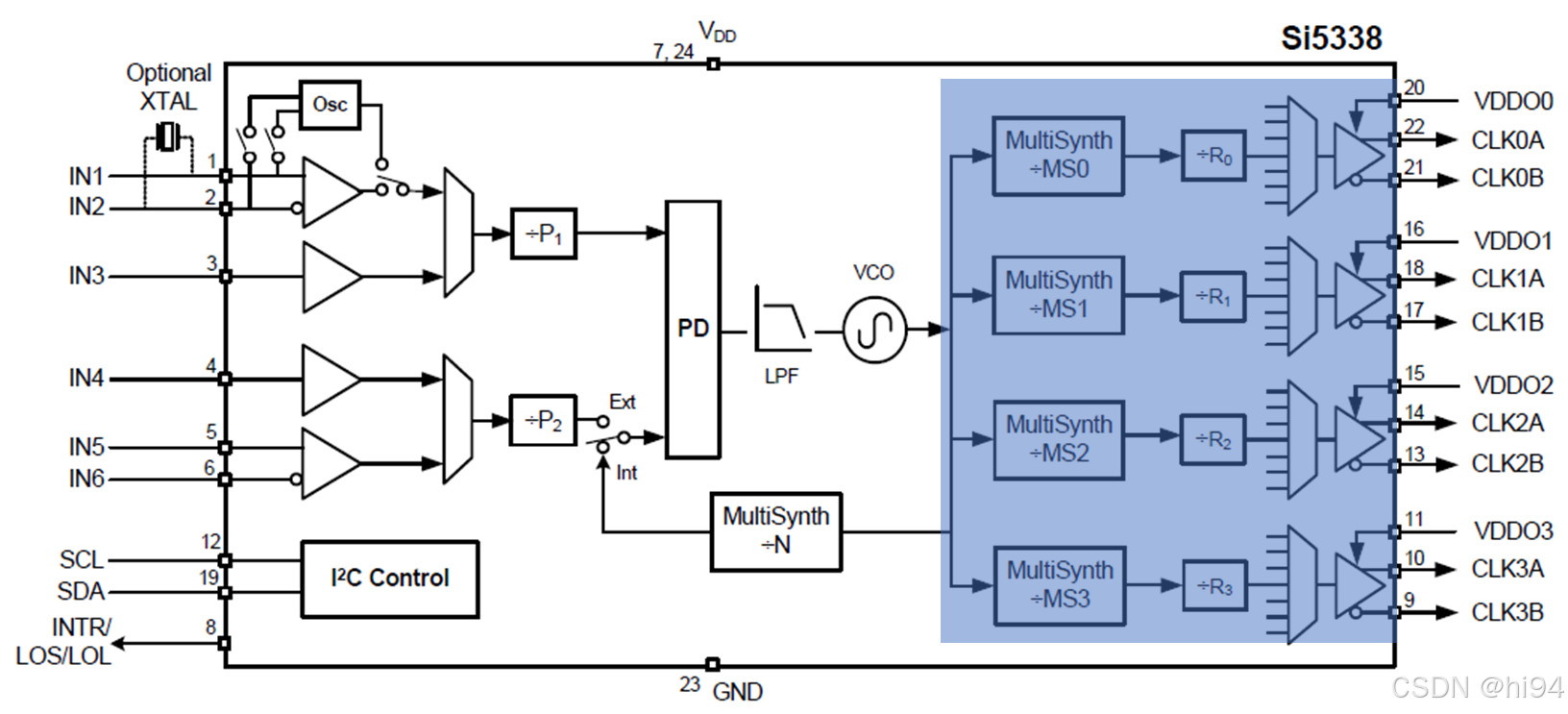

1.2 Si5338 Block Diagram

2. EVB 详解

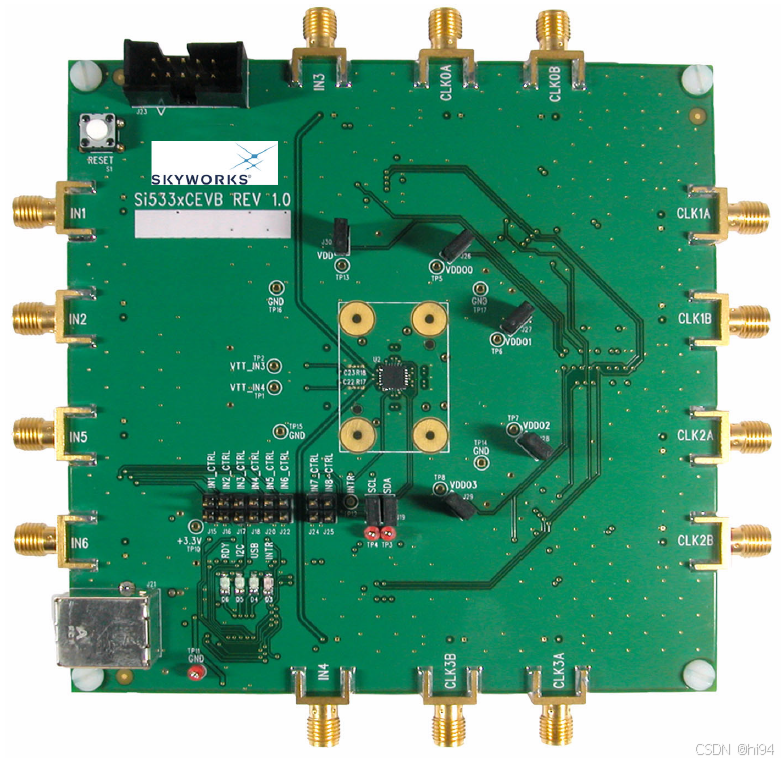

2.1 实物图

2.2 基本配置

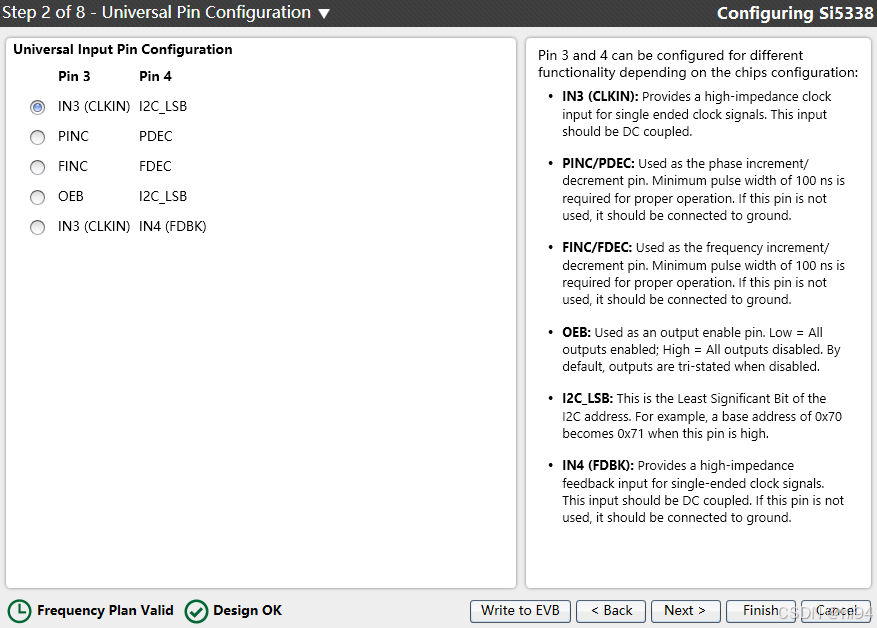

2.2.1 Universal Pin

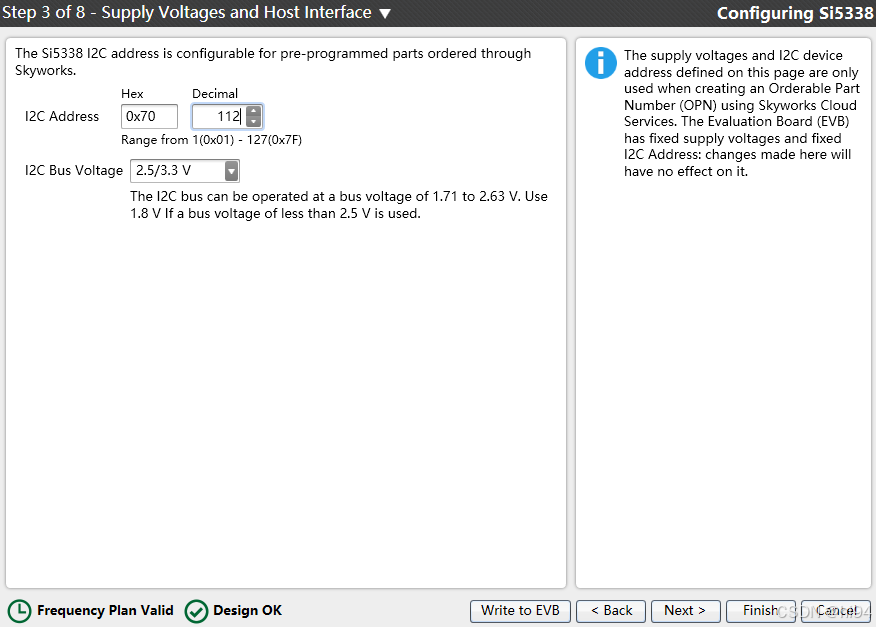

2.2.2 IIC I/F

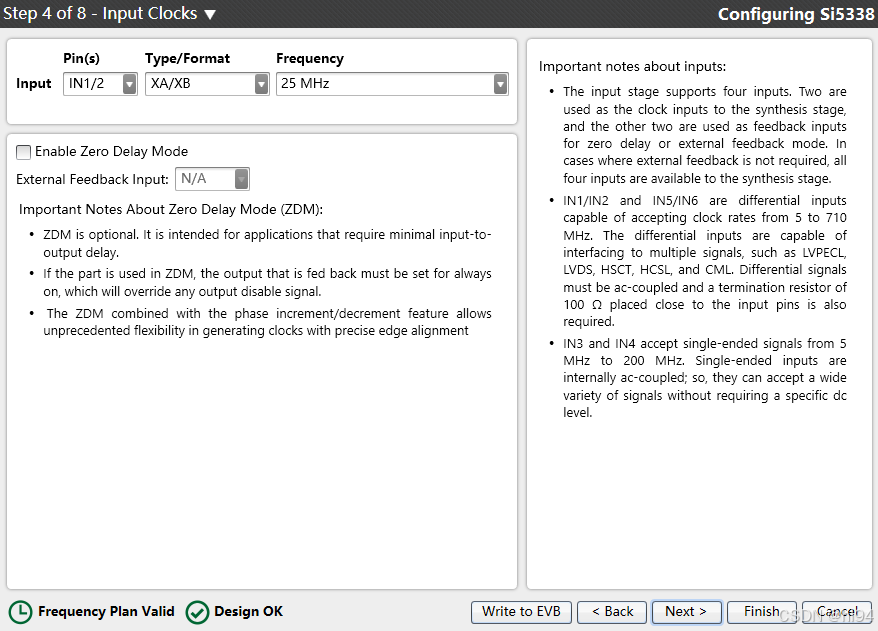

2.2.3 Input Clocks

EVB 板载晶振为 25MHz。

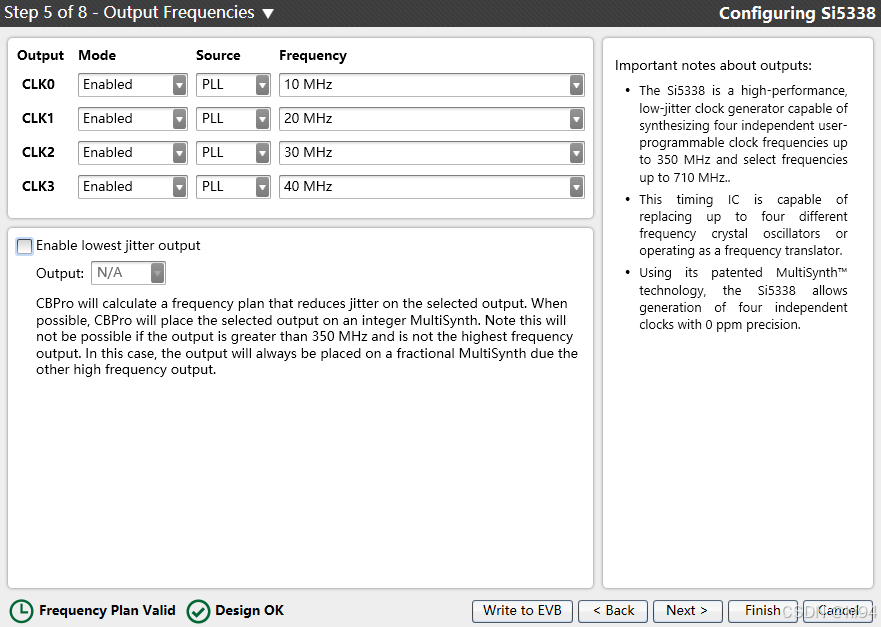

2.2.4 Output Frequencies

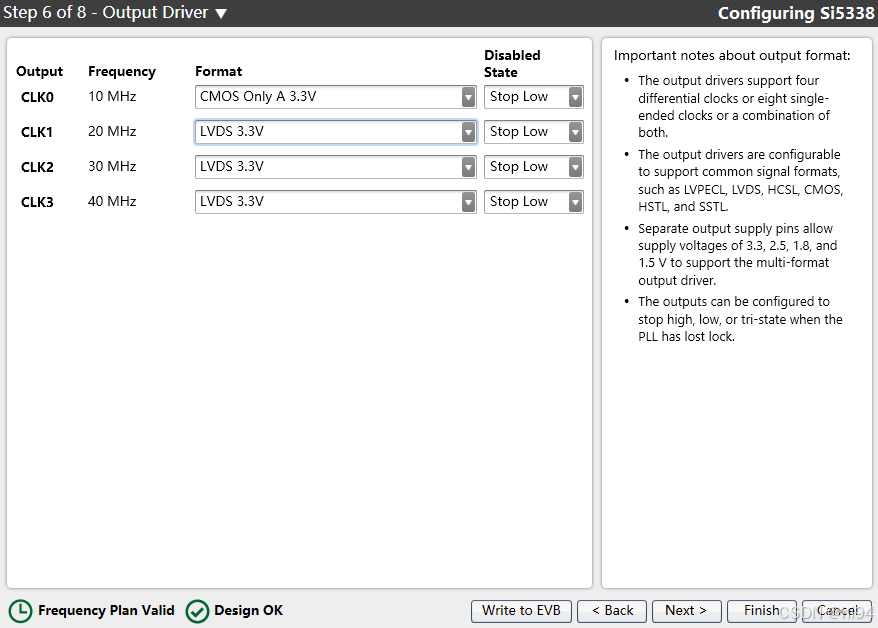

2.2.5 Output Driver

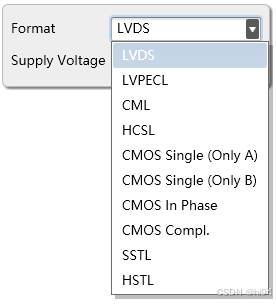

可选项:

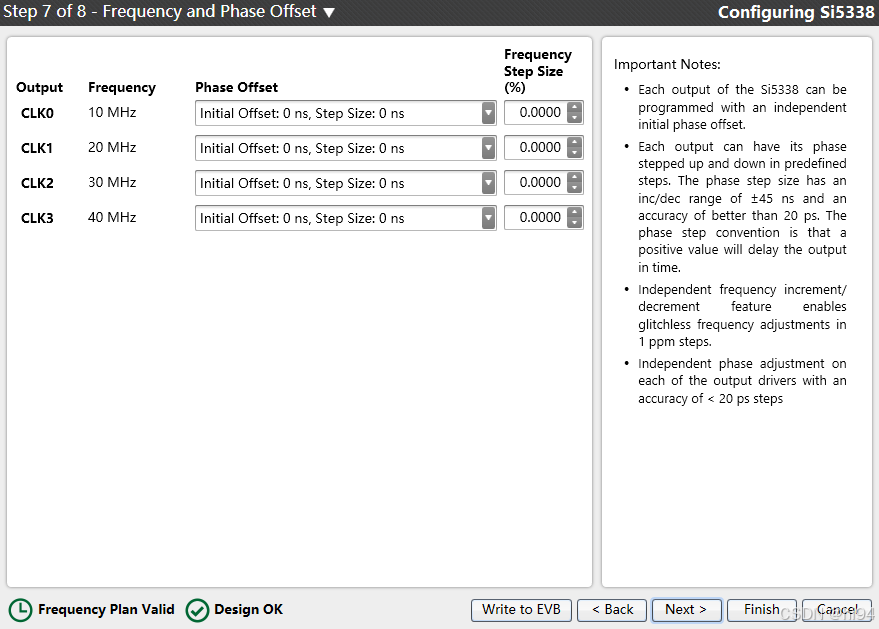

2.2.6 Freq and Phase Offset

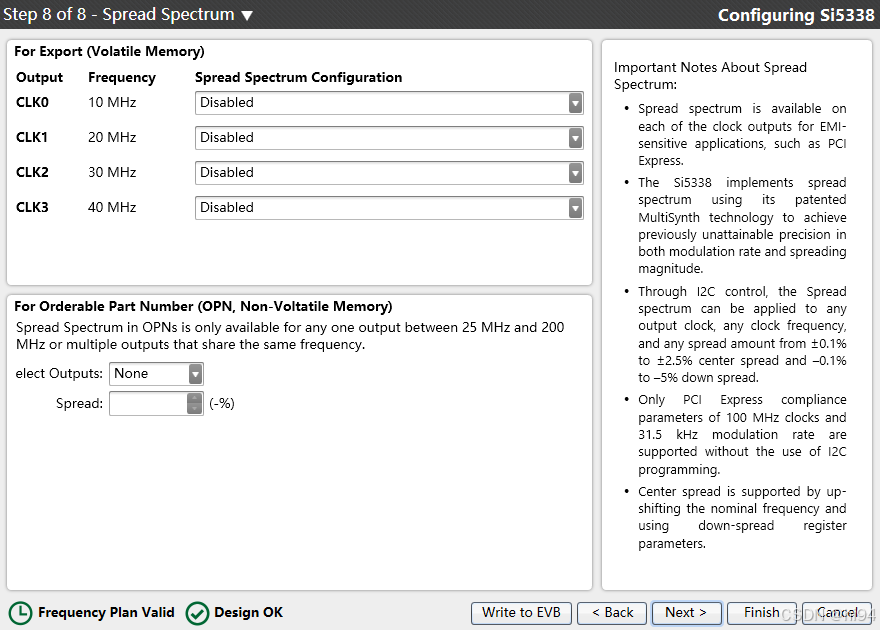

2.2.7 Spread Spectrum

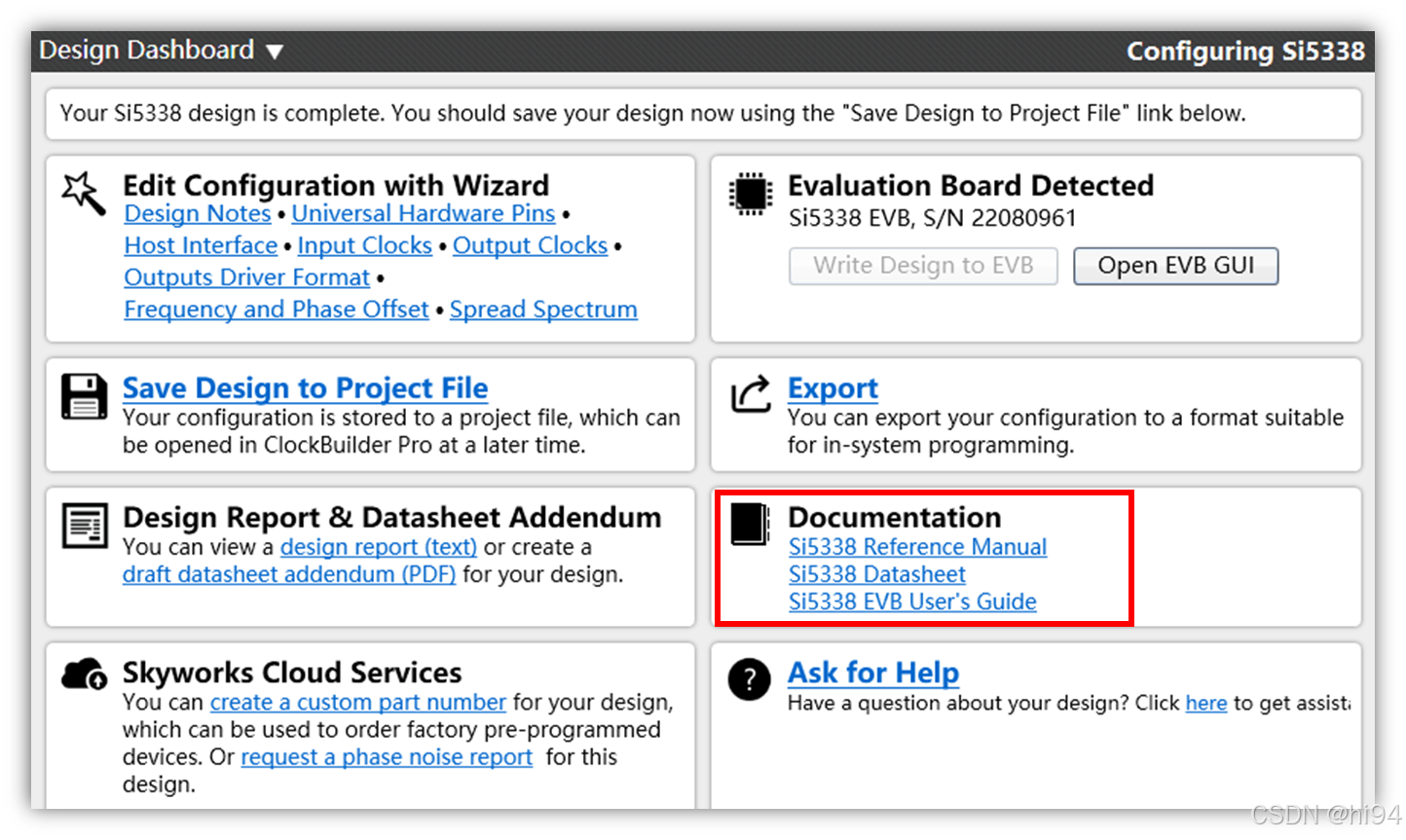

2.2.8 快速参考手册

2.3 可编程电压

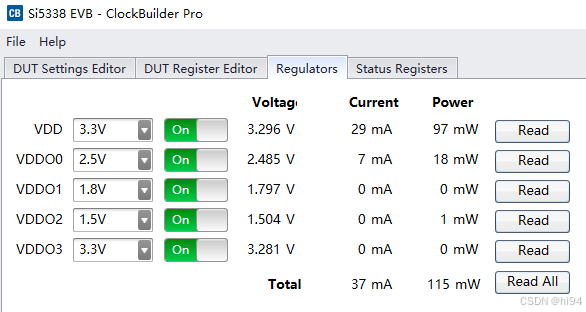

2.3.1 GUI 配置

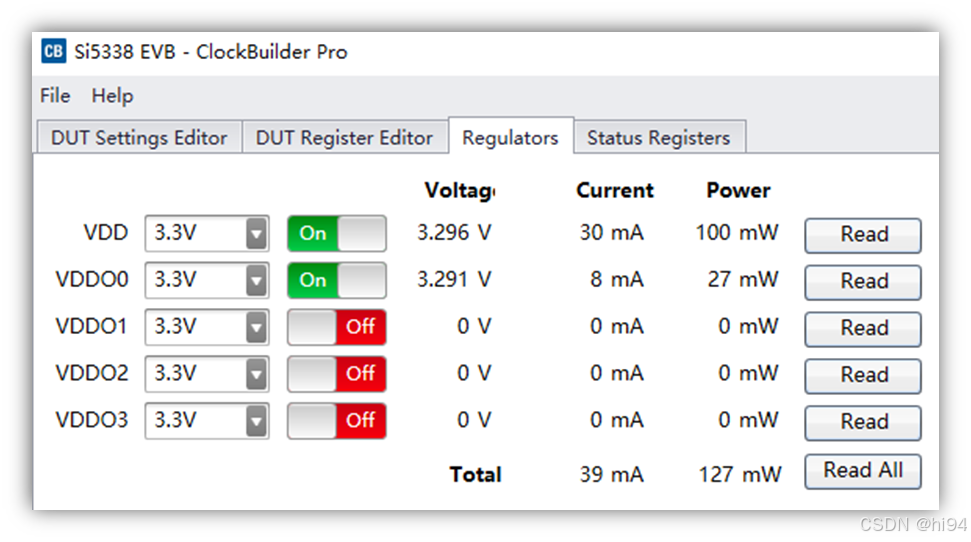

可通过 GUI 编程设定 VDD 供电电压(3.3V、2.5V、1.8V)。

可通过 GUI 独立配置四个输出的 VDDO 电压(3.3V、2.5V、1.8V、1.5V)。

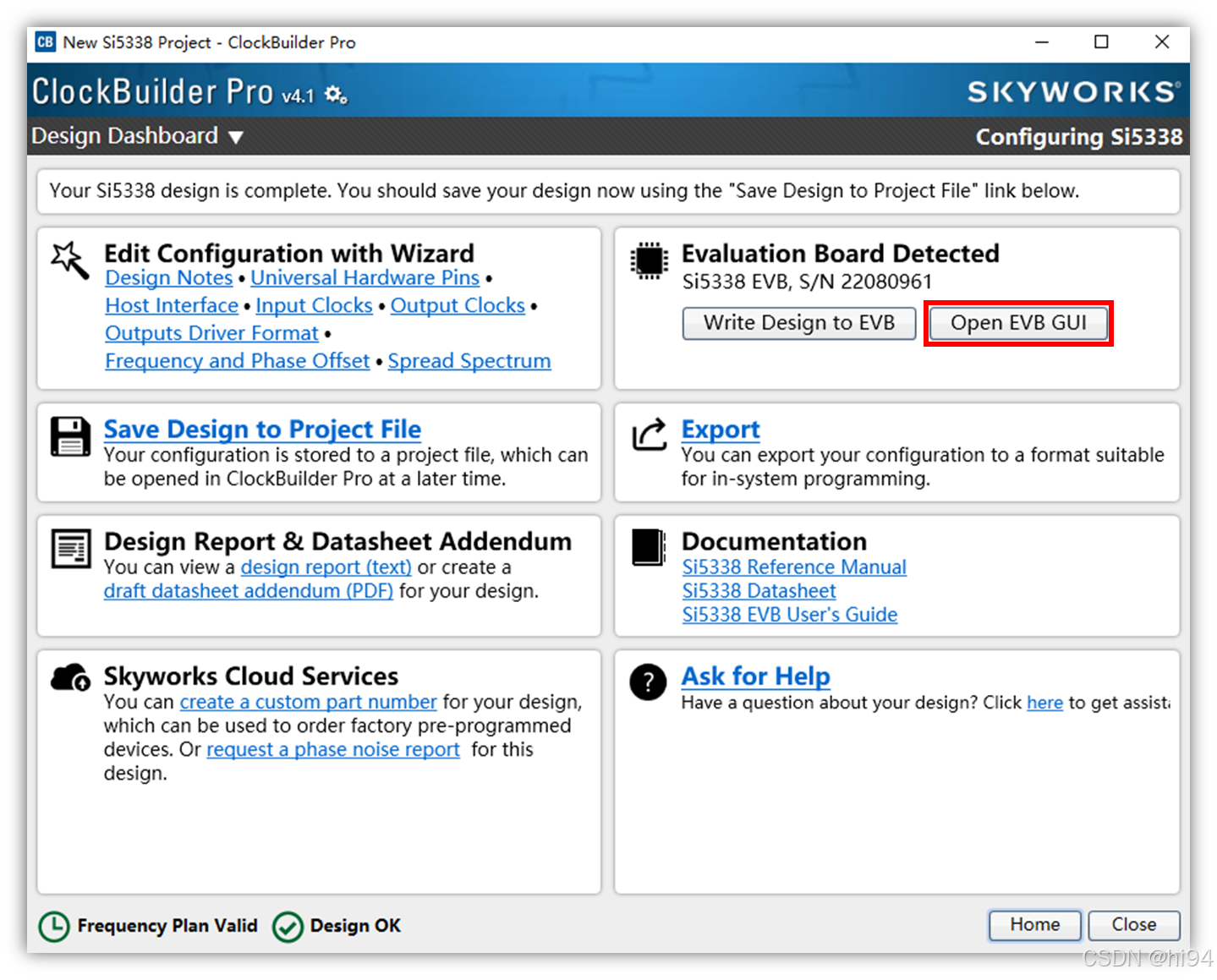

1)在 Design Dashboard 中,选择 Open EVB GUI

2)在 Si5338 EVB 中,选择 Regulators

2.3.2 原理解析

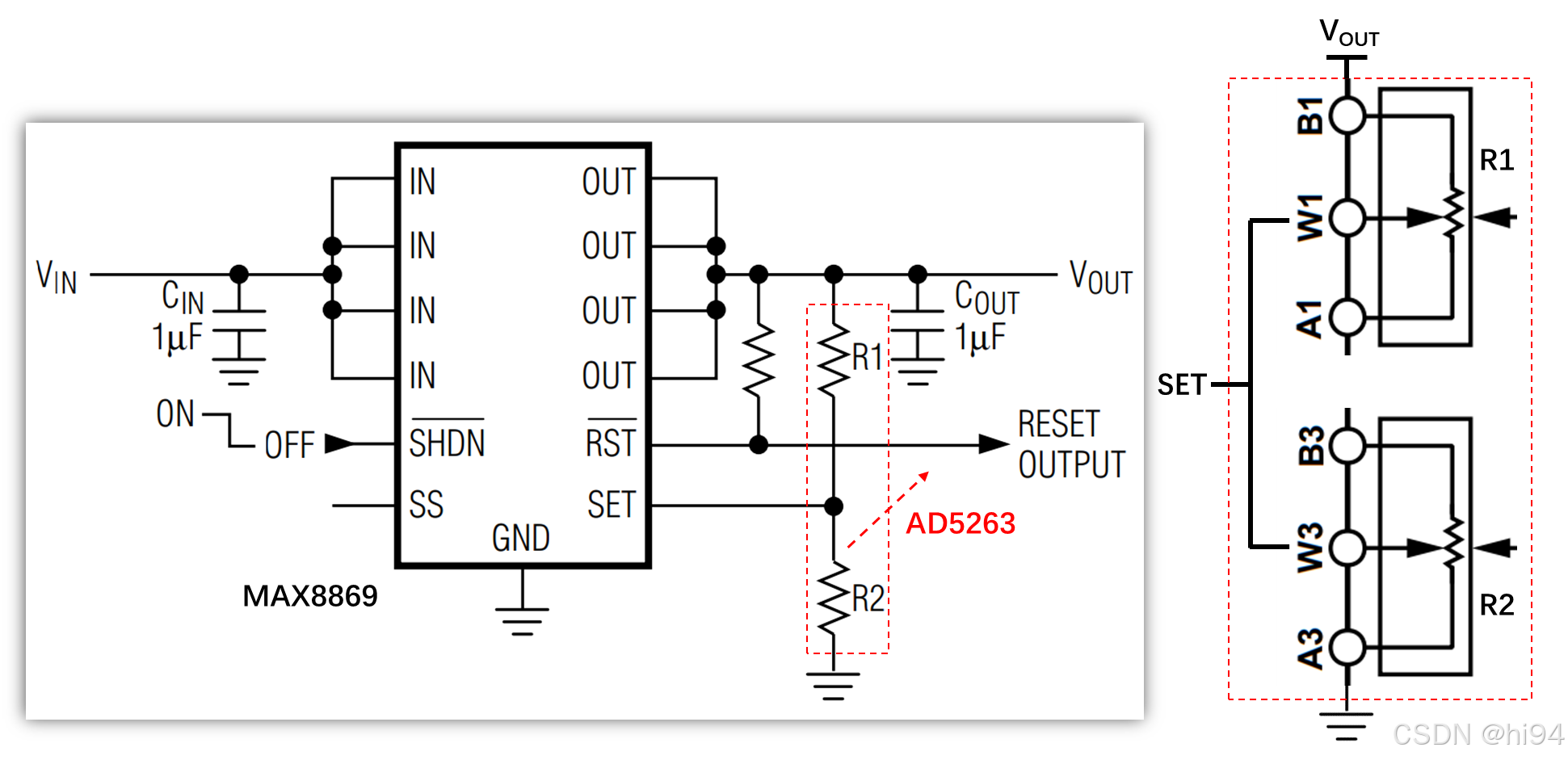

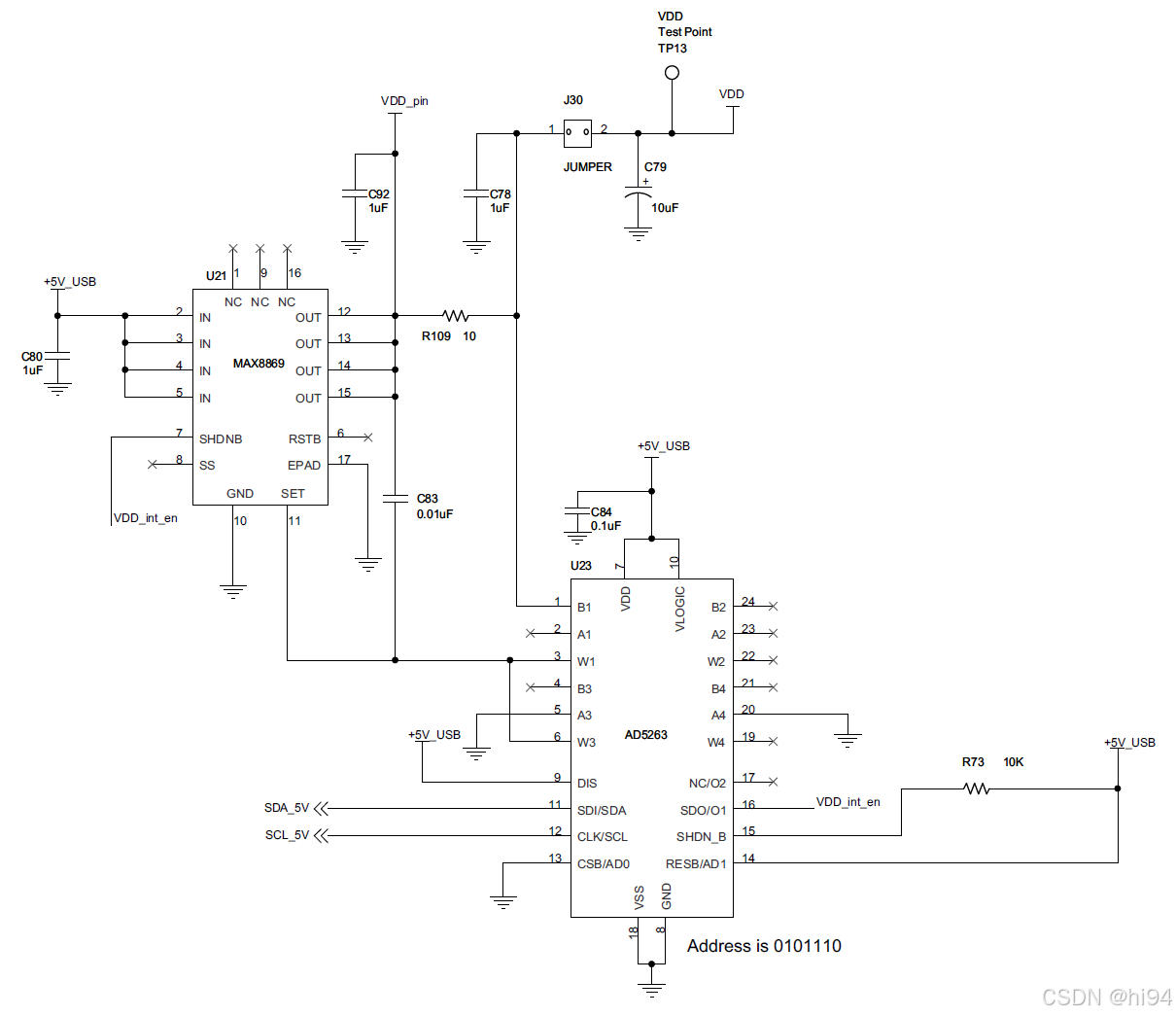

1)示意图

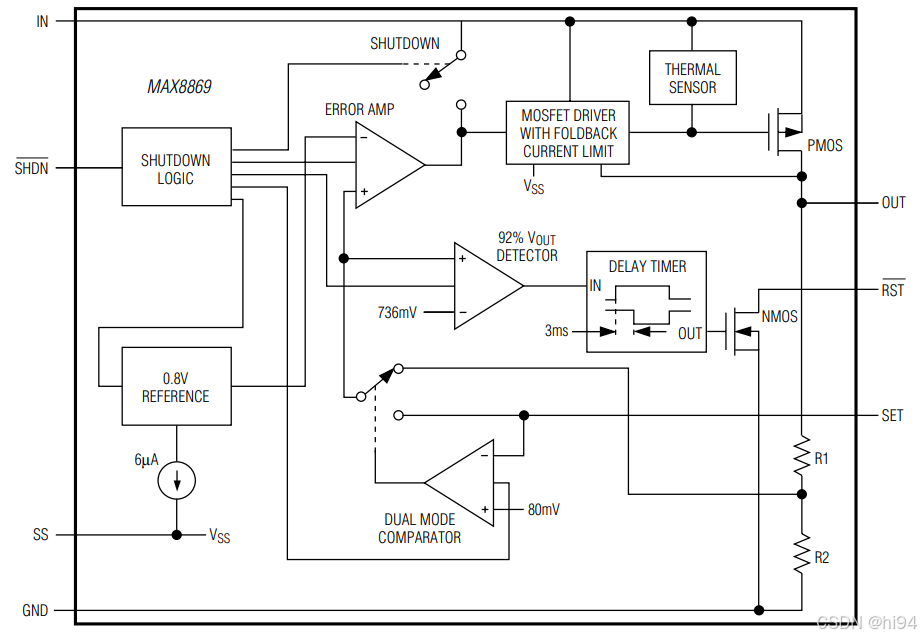

VOUT = Vset × (1 + R1 / R2) ,其中 Vset = 0.8V

2)原理图

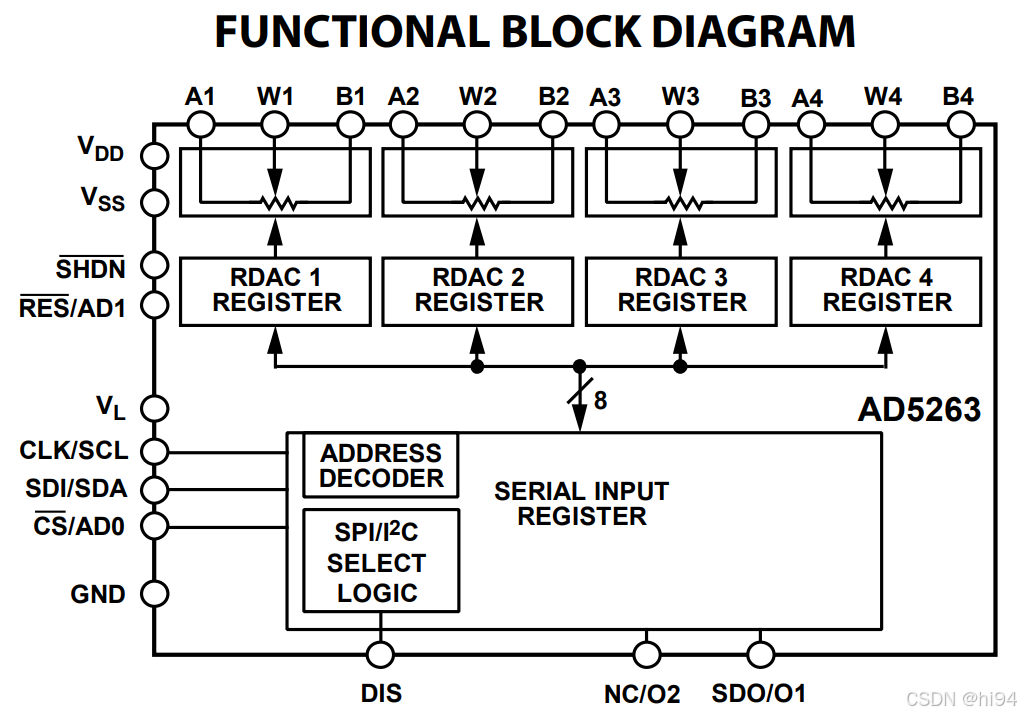

2.3.3 AD5263

一个四通道、15 V、256 位数字电位计,提供引脚可选的 SPI/I2C,它可实现与机械电位计或可变电阻相同的电子调整功能,具备低温度系数。

- 温度系数(变阻器模式):30 ppm/°C

- 温度系数(分压器模式):5 ppm/°C

- 供电:可采用 +4.5V 至 +15V 或 ±5V 电源供电

系统上电后,游标位默认为中量程。游标位可通过口进行编程设置。

I2C 模式下,用户可以利用附加可编程逻辑输出,驱动其系统中的数字负载、逻辑门和模拟开关。

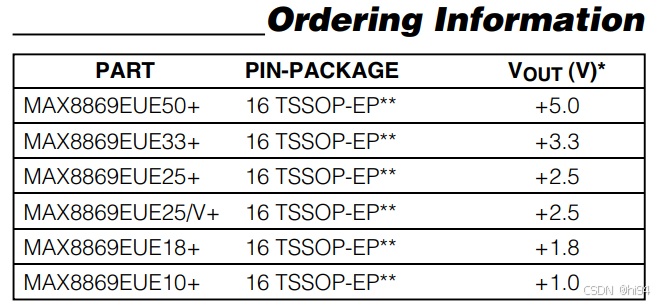

2.3.4 MAX8869

低压差线性稳压器

输出电压精度 ±1%,预设为 +5V、+3.3V、+2.5V、+1.8V、+1.0V,也可通过外部电阻分压器在+0.8V 至 +5V 范围内调节。

2.4 供电

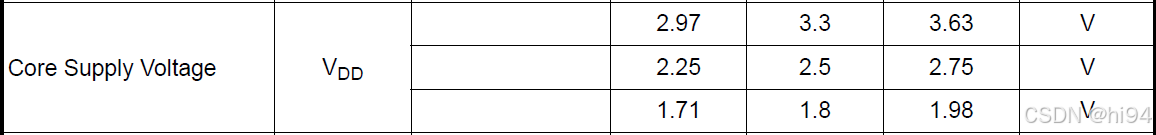

2.4.1 VDD

1)VDD:内核供电电压,支持 1.8V、2.5V、3.3V 输入。

VDD 不影响时钟的性能指标(Performance Characteristics)

参见:Table 5. Performance Characteristics

(VDD = 1.8 V –5% to +10%, 2.5 V ±10%, or 3.3 V ±10%, TA = –40 to 85 °C)

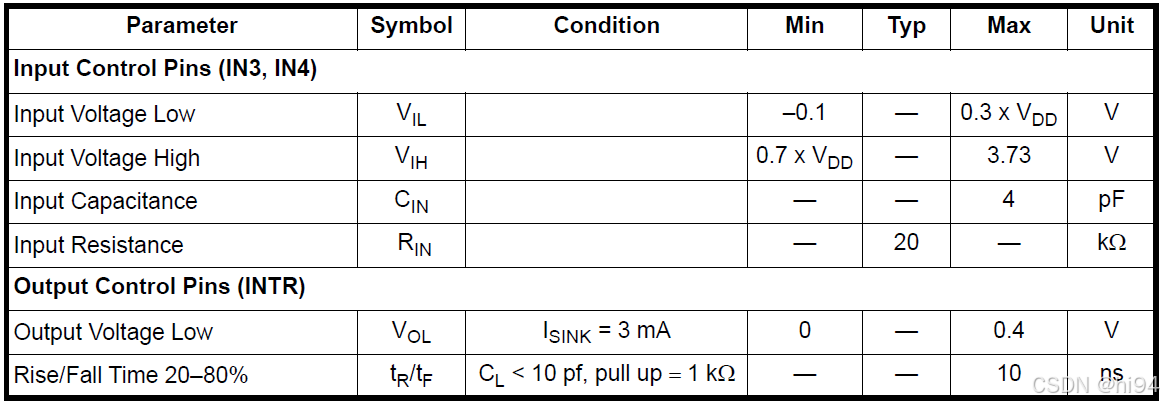

2)VDD 影响 Control Pins

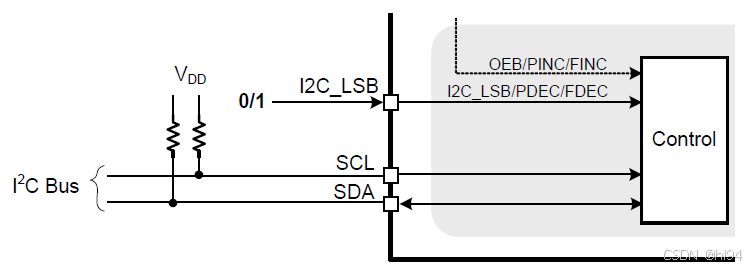

3)VDD 影响 IIC Pins

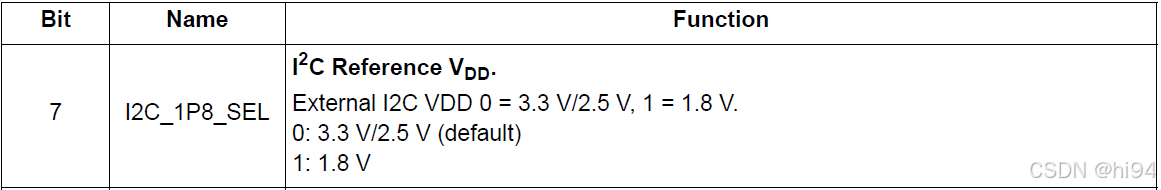

- IIC 总线可在 1.71V 至 3.63V 的电压范围内工作。

- 当 IIC 总线电压低于 2.5V 时,必须将寄存器 27[7] 置为 1 以确保符合 IIC 总线标准。

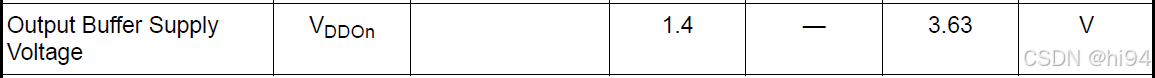

2.4.2 VDDOn

VDDOn:Output Clock Supply Voltage,支持 1.5V、1.8V、2.5V、3.3V 输入。

3. Si5338

3.1 Input Stage

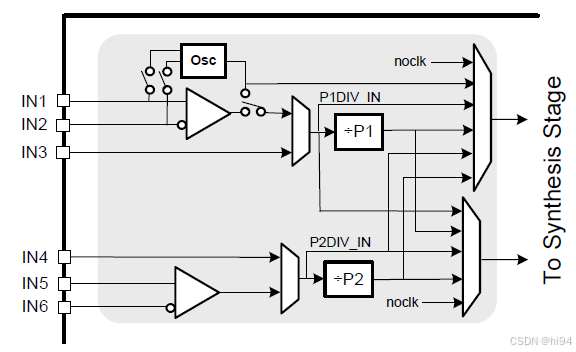

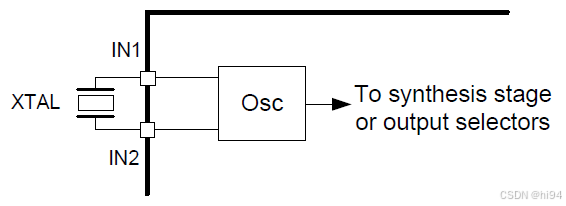

3.1.1 Diagram

3.1.2 时钟输入

时钟输入可以连接差分、单端信号

3.1.3 自由晶振

可以连接晶振

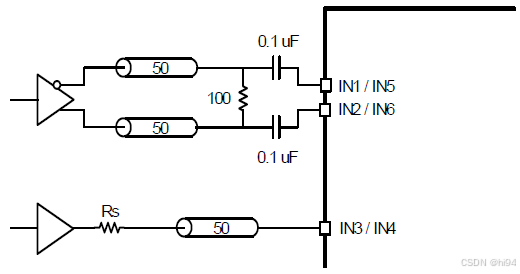

3.1.4 单端至差分

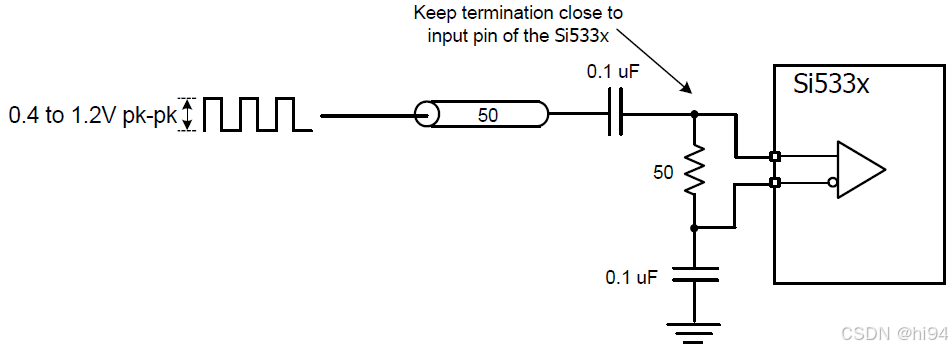

可以将任何单端信号连接到差分输入引脚(IN1/IN2 或 IN5/IN6)。

对于需要 50 Ω 负载的信号,推荐的接口如图所示。

示例中,输入电平小于 1.2 VPP SE(峰峰值单端)且大于 0.4 VPP SE。此时,建议的最大输入频率为 350 MHz。

3.2 Output Stage

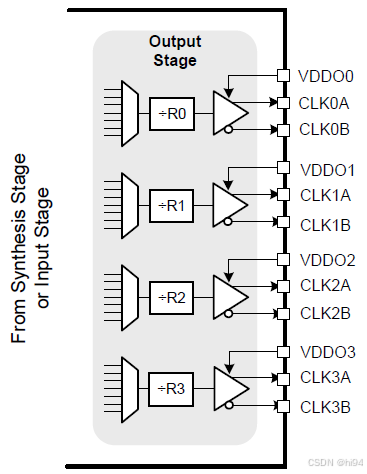

3.2.1 Diagram

如下图阴影部分所示:

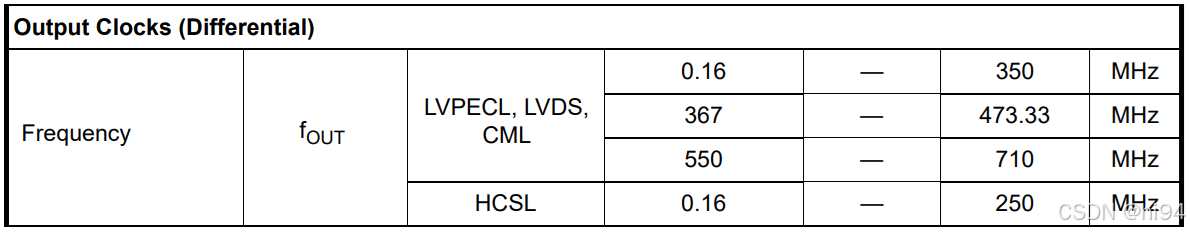

每个通道可独立配置输出格式:

- LVPECL/LVDS:0.16 至 710 MHz

- HCSL:0.16 至 250 MHz

- CMOS:0.16 至 200 MHz

- SSTL/HSTL:0.16 至 350 MHz

每个通道可独立配置电压:

- 1.5, 1.8, 2.5, 3.3 V

3.2.2 Output CLK Info

- VDD = 1.8 V –5% to +10%

- VDD = 2.5 V ±10%

- VDD = 3.3 V ±10%

- TA = –40 to 85 °C

3.2.3 Output Volt Info

- VDD = 1.8 V –5% to +10%

- VDD = 2.5 V ±10%

- VDD = 3.3 V ±10%

- TA = –40 to 85 °C

3.3 LVDS

3.4 ECL

3.4.1 ECL 系列

ECL(Emitter-Coupled Logic,发射极耦合逻辑),是一种高速数字逻辑。它的核心特点在于使用晶体管(通常是双极性结型晶体管 BJT)以一种特殊的方式连接,使得晶体管在开关过程中不会进入饱和区,避免了从饱和状态中退出的时间延迟,因此开关速度非常快。

常见的变种有:NECL, PECL, LVPECL

命名规则如下:

[Low voltage] [Negative/Positive(Pseudo)] Emitter-coupled logic

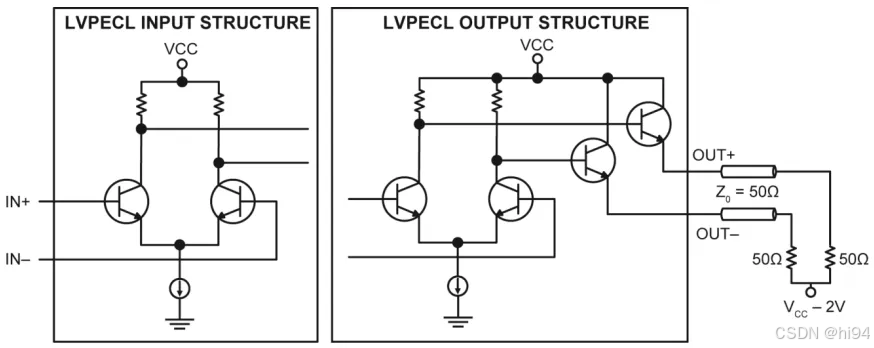

3.4.2 输入输出级

输入输出级示意图:

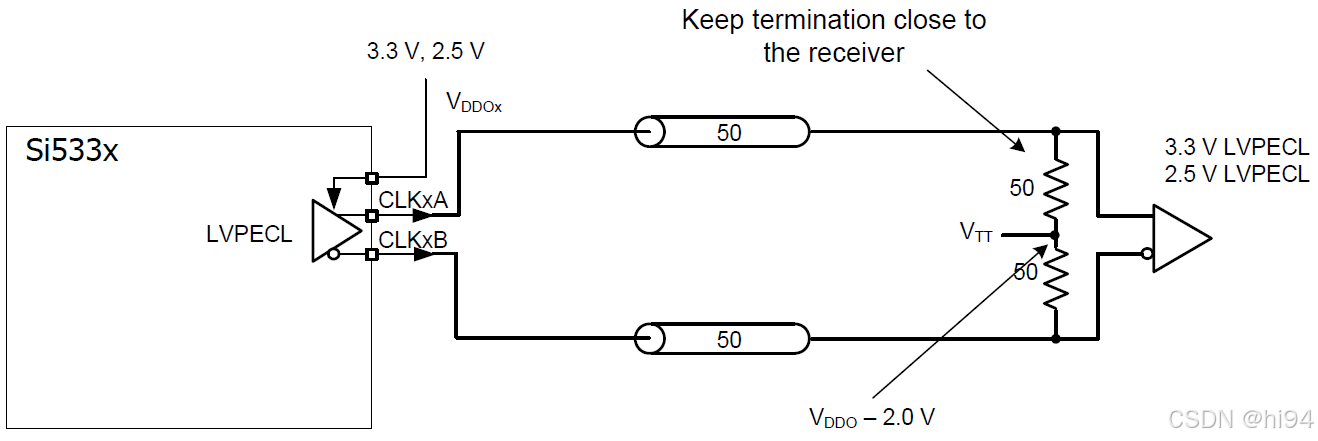

3.4.3 DC 耦合

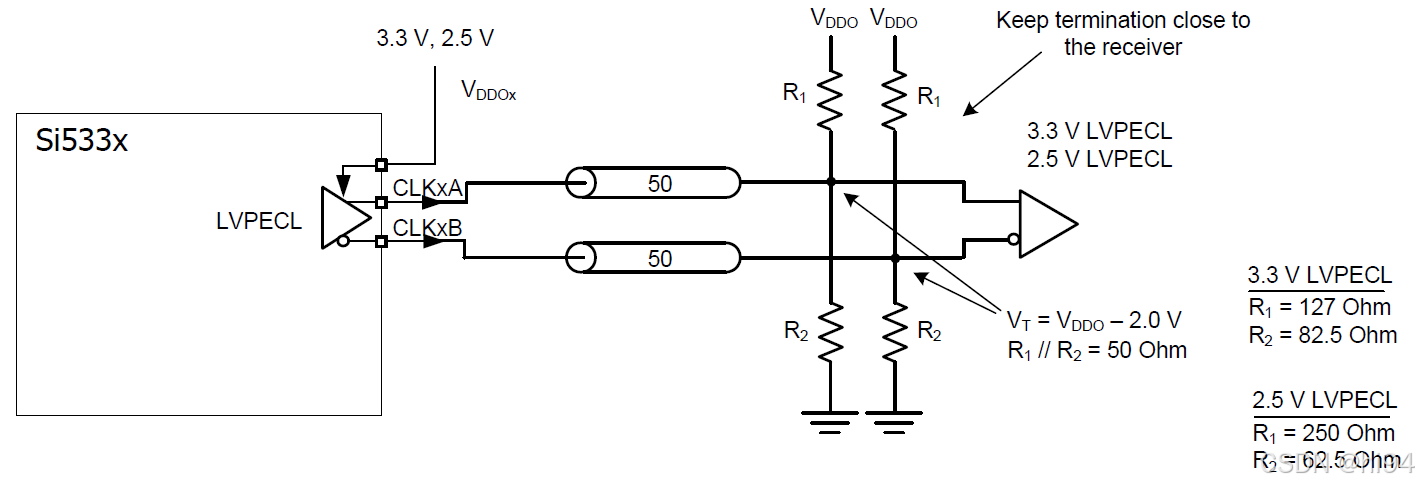

1)DC Coupled Termination of 50 Ohms to VDD – 2.0 V

- 标准的 LVPECL 驱动器支持两种常用的直流耦合配置。

- LVPECL 驱动器最初设计为端接 50 Ω 到 VDD–2 V。

- VTT 可以通过如图所示的简单分压电路提供。

2)DC Coupled with Thevenin Termination

- 戴维南等效电路提供了一个端接至 VDD–2.0 V 的 50 Ω 负载。

- 对于 3.3 V LVPECL,使用 R1 = 127 Ω 和 R2 = 82.5 Ω。

- 对于 2.5 V LVPECL,使用 R1 = 250 Ω 和 R2 = 62.5 Ω。

- 缺点:戴维南等效电路会从 VDDO 电源消耗额外的功率。

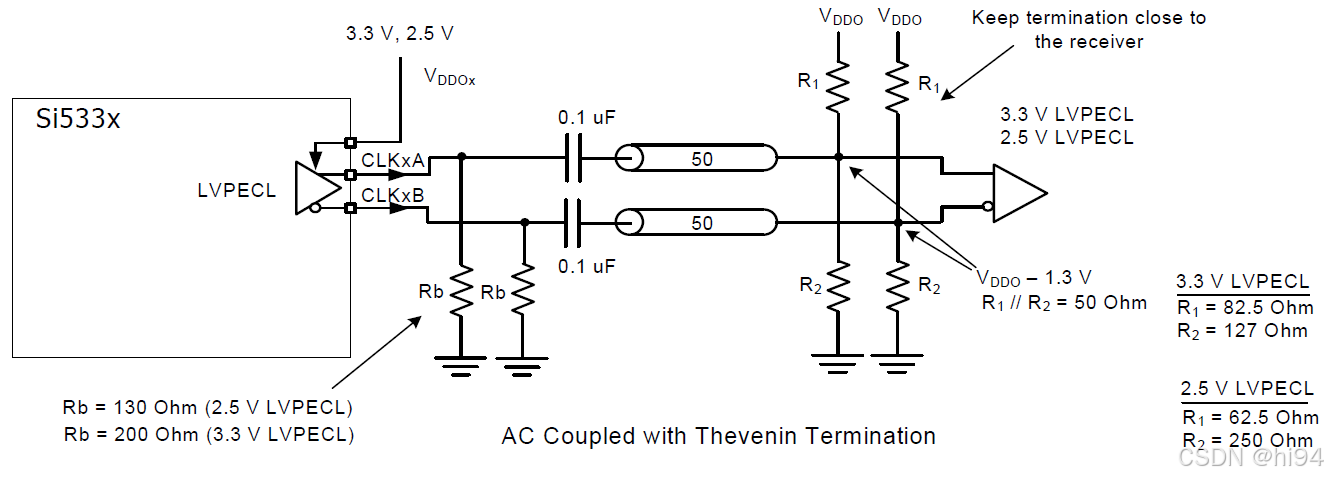

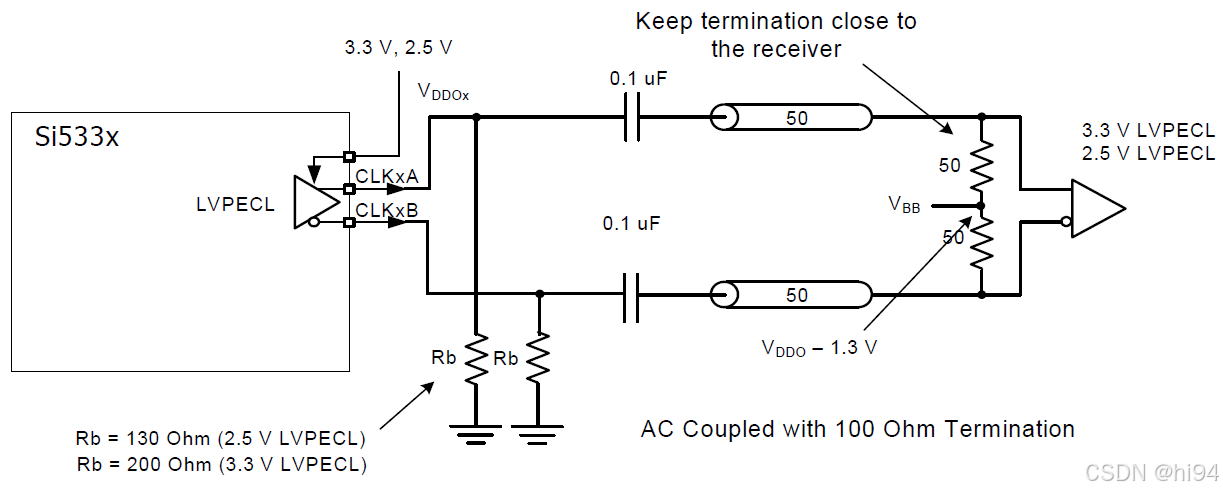

3.4.4 AC 耦合

当接收器和驱动器具有兼容的电压摆幅但共模电压不同时,必须使用交流耦合。

交流耦合对于直流平衡信号(例如 50% 占空比的时钟信号)非常有效。

1)AC Coupled with Thevenin Termination

- 戴维南等效终端是一种方便且常用的方法。

- 尤其是在没有 VBB (即 VDD – 1.3 V) 电源的情况下。

- 它会消耗额外的功率。

(PS:VBB 的全称是 Bipolar Base Voltage)

2)AC Coupled with 100 Ohm Termination

- 消耗的功率较少

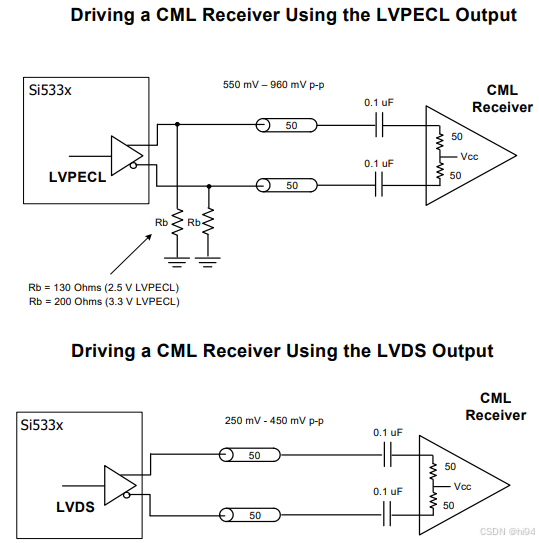

3.5 CML

Current Mode Logic,电流模式逻辑。

采用差分传输,并在接收端端接至 Vcc,阻值为 50 Ω。

CML 接收器可以由 LVPECL 或 LVDS 输出驱动,具体取决于接收器所需的信号摆幅。

当使用 LVPECL 输出驱动 CML 接收器时,可以实现 550 mV 至 960 mV 的单端输出摆幅。

为了获得更小的输出摆幅,建议使用 LVDS 模式,其单端摆幅在 250 mV 至 450 mV 之间。

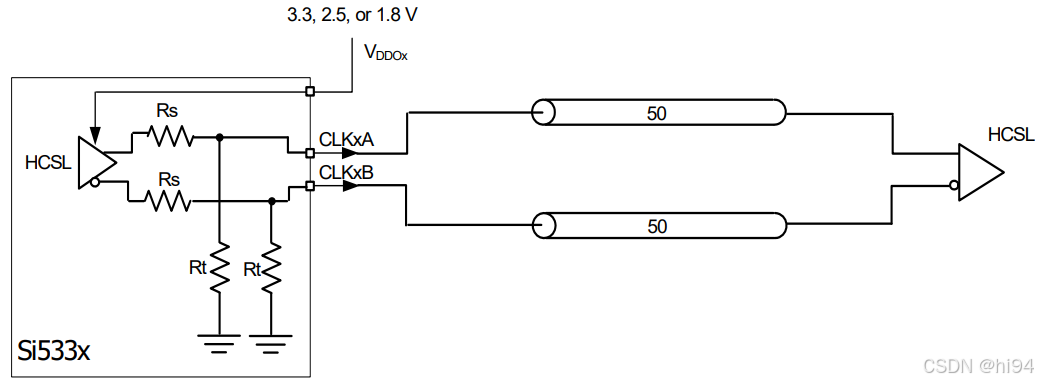

3.6 HCSL

Host Clock Signal Level,主机时钟信号电平。

输出常用于 PCI Express 应用中。

典型的 HCSL 驱动器具有一个开路源极输出,需要一个外部串联电阻和一个对地电阻。

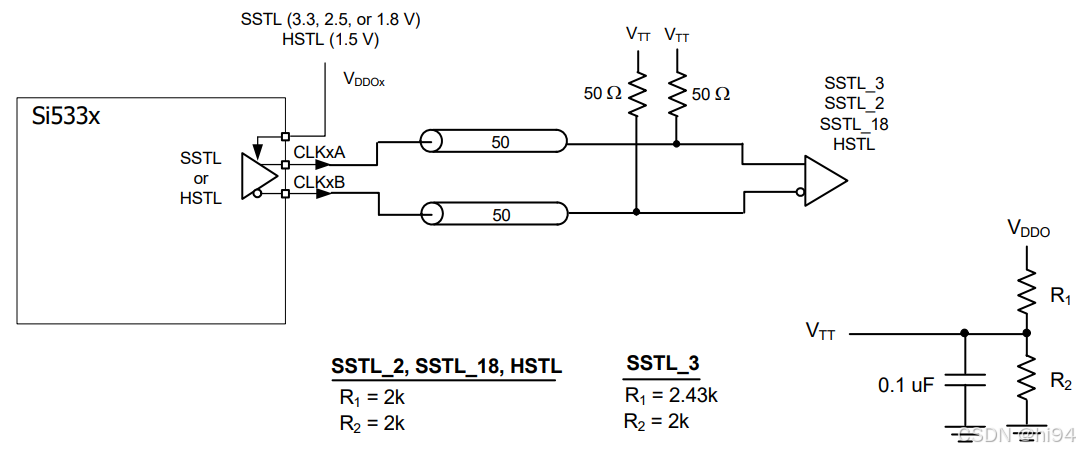

3.7 SSTL

Stub Series Termination Logic,短线串联终端逻辑。

常用于基于 DRAM 的 DDR 内存芯片和内存模组。

SSTL 可以是单端,也可以是差分。

3.8 HSTL

同 3.6。

4. 总结

本文介绍了 Si5338 EVB 的功能和配置,以及 Si5338 芯片的特性。文档深入解析了 EVB 的可编程电压功能,包括 GUI 配置和基于 AD5263 数字电位计及 MAX8869 稳压器的原理。供电部分阐述了 VDD 和 VDDOn 对芯片和接口的影响。

针对 Si5338 芯片,文档介绍了其输入和输出级,包括多种时钟输入方式(差分、单端、晶振)和单端转差分电路。输出级支持 LVPECL、LVDS、HCSL、CMOS 和 SSTL/HSTL 等多种格式,并可独立配置电压。文档还详细解释了LVDS、ECL(包括 LVPECL 及其直流、交流耦合)、CML、HCSL 和 SSTL/HSTL 等不同输出接口的特性和应用。