FPGA前瞻篇-数字电路基础-逻辑门电路设计

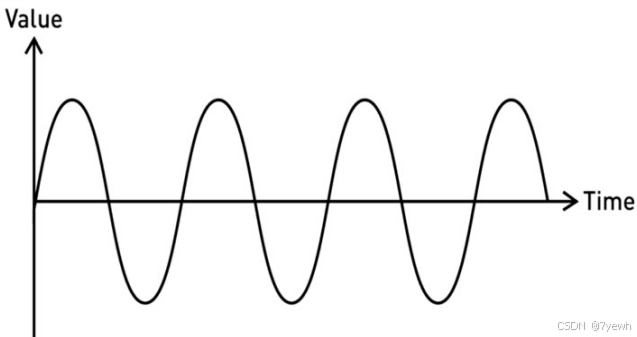

模拟信号:

一条随时间连续变化、平滑波动的曲线,比如正弦波。

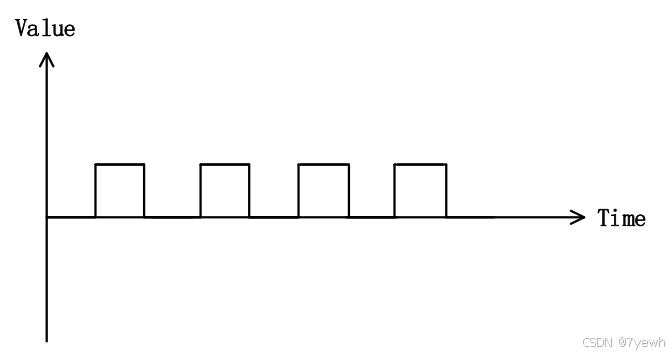

数字信号:

一条只有高低两个状态(0和1),跳变清晰的方波曲线。

在 IC 或 FPGA 的逻辑设计中,我们通常只能处理数字信号,因为它们只识别高电平和低电平两个状态。而模拟信号是连续变化的,无法直接被数字电路识别。不过,随着技术的发展,一些高端的 FPGA 已经集成了模数转换器(ADC),可以采集外部的模拟信号并转换成数字信号进行处理,使得 FPGA 能在一定程度上参与模拟信号的处理。

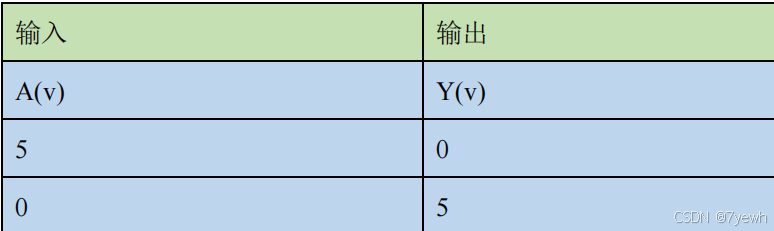

| 表达形式 | 说明 | 示例 | 等价二进制 |

|---|---|---|---|

b | 二进制 | 4'b0101 | 0101 |

d | 十进制 | 4'd2 | 0010 |

h | 十六进制 | 4'hA | 1010 |

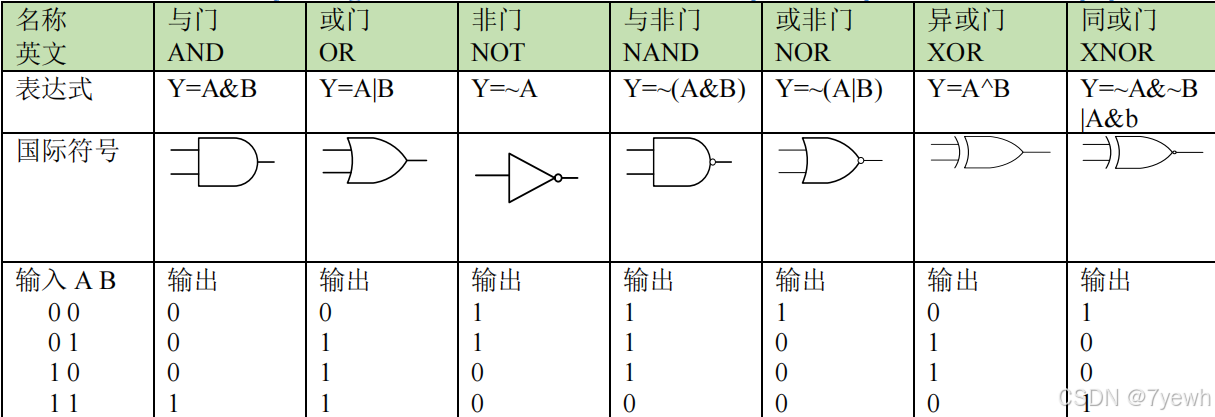

数字电路里面一般包括与门、或门、非门等门电路。另外为了简化逻辑,实际电路里面还扩展了几个其他的运算电路,他们是与非门、或非门、异或门和同或门。这些门电路是构成数字电路的基础。

数字电路的基本构成单元是各种逻辑门电路,最常见的有以下几类:

| 名称 | 逻辑符号 | 功能说明 |

|---|---|---|

| 与门(AND) | A·B | 两个输入都为 1 时输出为 1 |

| 或门(OR) | A+B | 只要有一个输入为 1 就输出为 1 |

| 非门(NOT) | ¬A 或 ~A | 对输入信号取反(0变1,1变0) |

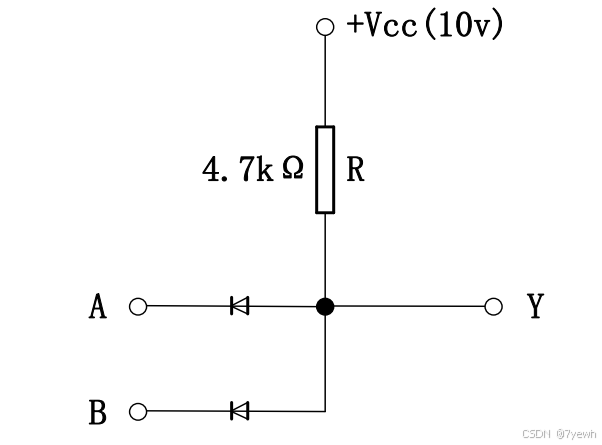

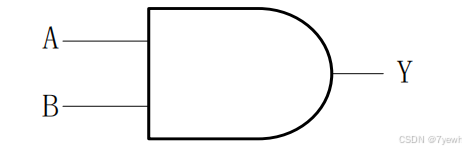

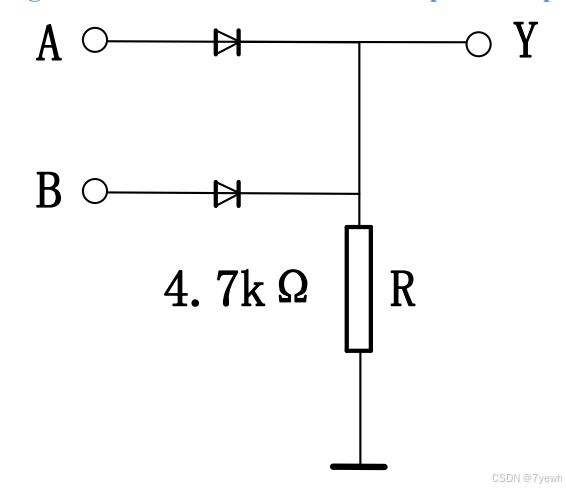

与门是一种逻辑乘法门电路。

只有当所有输入都是“1”时,输出才是“1”;否则输出为“0”。

常用于控制逻辑中“必须同时满足多个条件”的场景。

与门是执行“与”运算的基本门电路。与门有多个输入端, 1 个输出端。当多个输入端同时为“逻辑

1 ”高电平时,输出才为“逻辑 1 ”电平,否则输出为“逻辑 0 ”低电平。

与门的表达式是 F = A & B ,“ & ”代表与的意思,这个符号也是 Verilog 语法定义的与逻辑符。

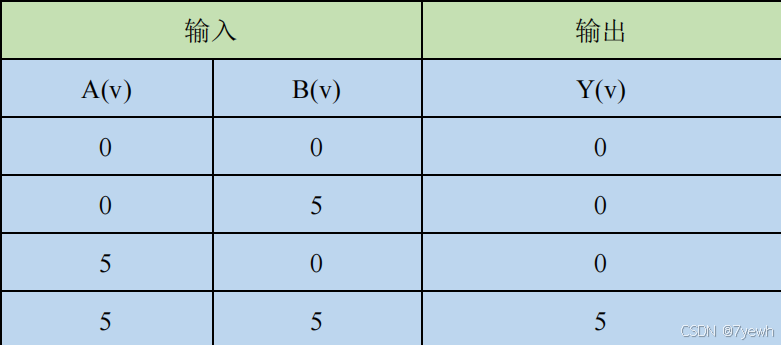

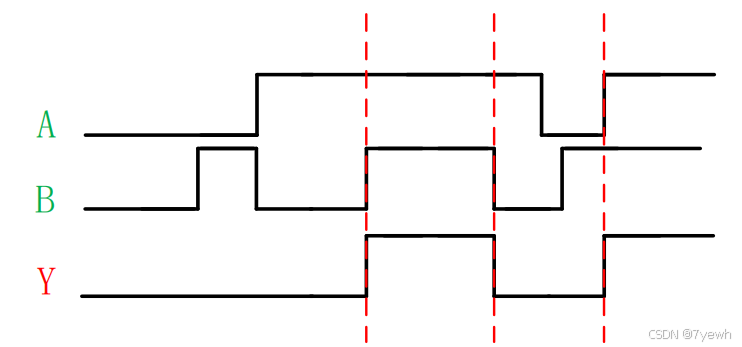

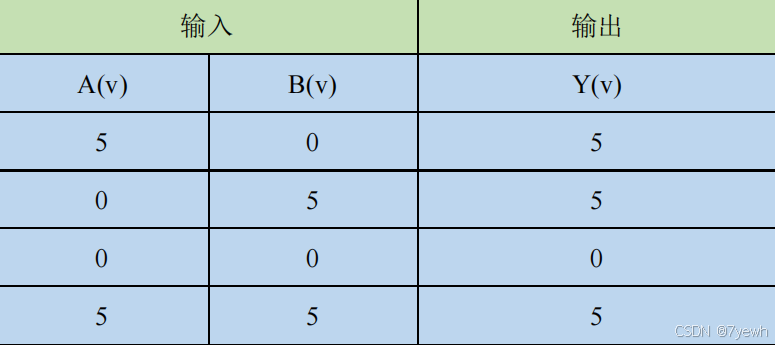

由真值表可以看出,当信号 A 和信号 B 全为 1 时,输出信号 Y 才为 1 ;当输入信号任意为 0 时,输出信号 Y 的值为 0。

module and_gate(input A, //输入 Ainput B, //输入 Boutput Y //输出 Y

);

//assign 相当于一条连线,输入 A 和输入 B 相与后连接输出 Y。

assign Y = A & B;endmodule非常的简单的代码,就不多说了。。

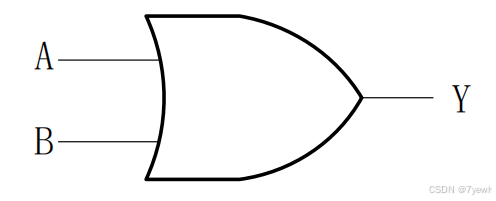

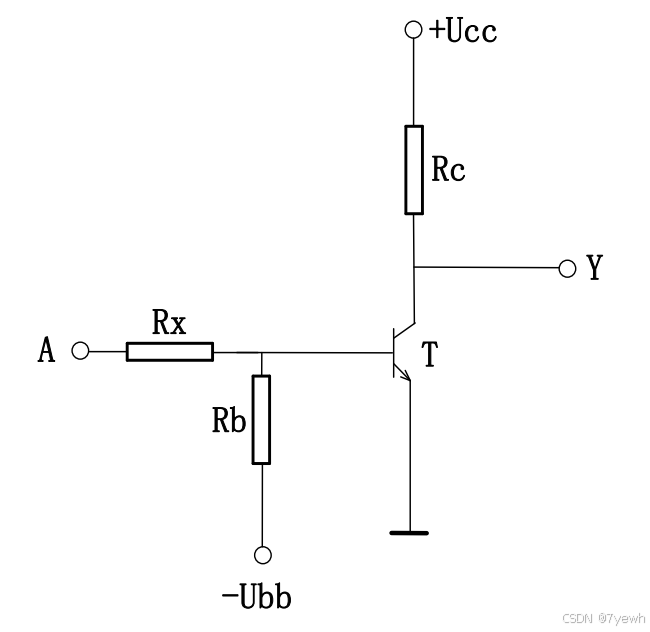

或门,英文名称是 OR Gate ,又称“或电路”、逻辑“或”电路。或门也是门电路里面比较重要的一个

逻辑门。

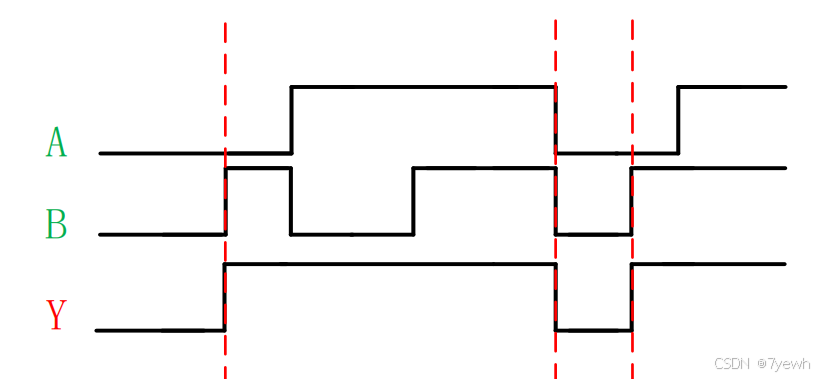

或的含义是只有当决定一件事情的任意一个条件具备时,这个事件就会发生。 门是执行“或”运算的基本门电路。或门有多个输入端,1 个输出端。当多个输入端任意一个端口为“逻辑 1”高电平时,输出就为“逻辑 1”电平,只有全部输入条件都不满足时,或门输出为“逻辑 0” 低电平。或门的表达式是 F = A | B,“|”代表或的意思,这个符号也是 Verilog 语法定义的或逻辑符。

module or_gate(input A, //输入 Ainput B, //输入 B output Y //输出 Y

);

//输入 A 或输入 B

assign Y = A | B;

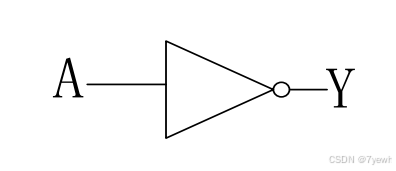

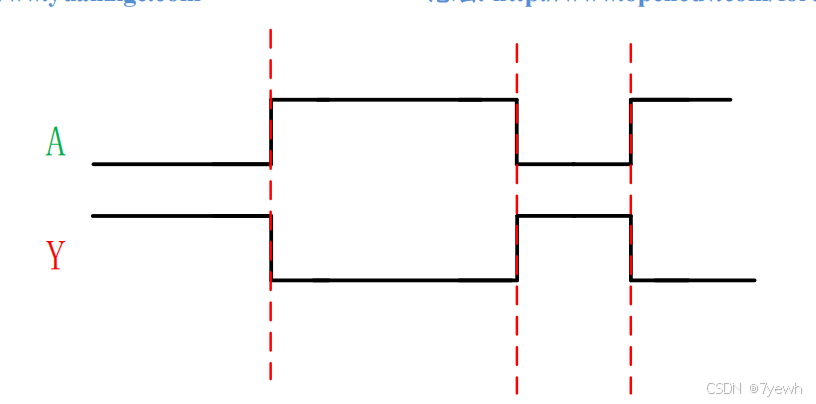

endmodule 非的含义是取反的意思,比如一个事情要发生,那么取反,就是这个事件不会发生。

非门是执行“非”运算的基本门电路。非门有 1 个输入端, 1 个输出端。当 1 个输入端端口为“逻辑

1 ”高电平时,输出就为“逻辑 0 ”低电平;当 1 个输入端端口为“逻辑 0 ”高电平时,输出就为“逻辑

1 ”高电平。

module not_gate(input [3:0] A, //4 位数据的输入信号 A output [3:0] Y //4 位数据的输出信号 Y

);

//assign Y[3:0] = ~A[3:0];

assign Y = ~A;

endmodule