【EMC设计基础--信号环路分析、PCB设计规则】

四、电源环路分析

1、高频脉冲电流的来源:

在电源与芯片组成的电源环路中,高频脉冲电流的主要来源是芯片(负载),而非电源本身。

芯片是高频脉冲电流的 “源头”

芯片(尤其是数字芯片,如 CPU、MCU、FPGA 等)的工作过程本质是内部晶体管的高速开关动作(如 CMOS 电路的导通与截止),这种开关会直接导致其对电流的需求发生瞬时、剧烈的变化,从而产生高频脉冲电流。

电源的角色:“抑制者” 而非 “产生者”

电源(如线性电源、开关电源、LDO 等)的核心功能是提供稳定的直流电压,其设计目标是尽可能抑制输出电流的高频波动。虽然电源自身可能存在一定的高频噪声(如开关电源的开关频率噪声,通常为几十 kHz 到几 MHz),但这属于电源的 “固有噪声”,而非驱动环路的 “高频脉冲电流”:

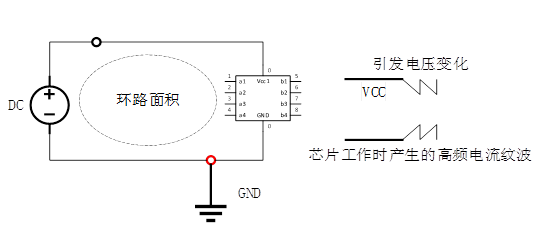

2、问题分析

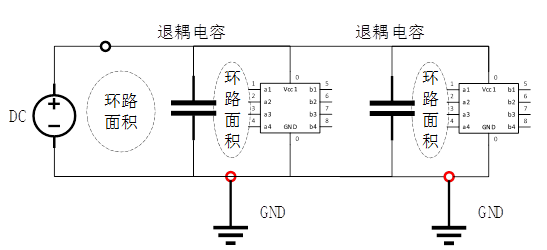

上图所示电路,环路面积大,环路感抗大,当电源环路有高频的纹波电流时,会造成电源电压产生高频电源纹波。

对于高频纹波电流,电源环路阻抗以感抗为主,环路面积越大,感抗越大,加粗导线无用。

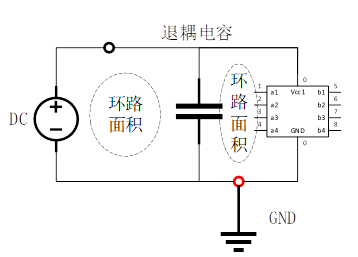

3、解决思路

a、增加退耦电容,退耦电容和芯片间的环路面积减小,感抗小,芯片产生的高频脉冲电流产生的压降会大幅减小。

b、退耦电容和电源间的环路面积也减小了,且电源至退耦电容间无高频脉冲电流,对感抗不敏感,可通过加粗导线降低环路电阻。

导线电阻R=ρ L/S,

ρ是导线材料的电阻率(固定值,如铜、铝等);

L是导线长度;

S是导线的横截面积(加粗导线即增大S)。

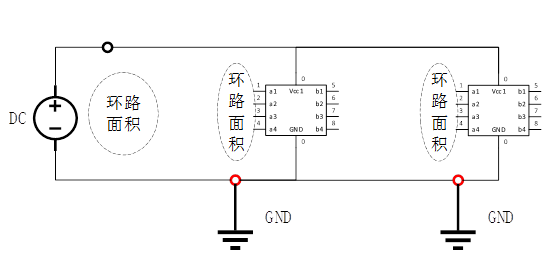

4、多个芯片,退耦电容如何布局

a、针对每个芯片增加去耦电容,去耦电容要就近放置,尽可能减小芯片和去耦电容间的环路面积。

b、干线只剩下低频直流分量,对环路感抗不敏感,加粗导线降低电阻即可。

5、一个芯片需要多个退耦电容,如何布局。

在芯片的退耦电容布局中,核心目标是最小化电容与芯片电源 / 地引脚之间的寄生电感和电阻,确保电容能快速响应芯片的高频脉冲电流需求(即 “就近提供电荷”)。

多个退耦电容(通常包含不同容值,如 0.1μF、1μF、10μF 等)的布局需遵循 “分层靠近、缩短路径、减小环路” 的原则

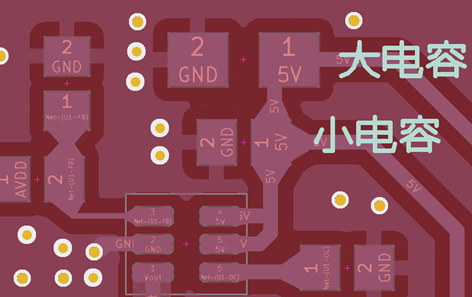

A、按容值分层布局:小容值靠近,大容值稍远

小容值电容(如 0.1μF、1nF):高频响应好(自谐振频率高),主要滤除 10MHz 以上的高频噪声,依赖极小的寄生电感,因此必须最靠近芯片(紧贴芯片边缘或焊盘旁)。

中容值电容(如 1μF、10μF):负责滤除 1-10MHz 的中频噪声,可放在小电容外侧(距离芯片 3-5mm)。

大容值电容(如 100μF、1000μF):储能能力强,主要应对低频纹波(1MHz 以下),响应速度较慢,可放在中容值电容外侧(距离芯片 5-10mm),或沿电源输入路径摆放。

B、缩短环路面积,减小寄生电感

退耦电容与芯片形成的 “电源 - 电容 - 地” 环路面积越小,寄生电感越低,抗 EMI 能力越强。具体措施:

走线最短化:电容的电源引脚(接 VCC)到芯片电源引脚的走线、电容的地引脚(GND)到芯片地引脚的走线,均需短而粗(优先用铜皮而非细导线),避免 “绕弯” 或 “长线”。

接地优化:电容的地引脚应通过最短路径连接到地平面(例如,直接在电容焊盘旁打地过孔,避免绕到远处接地)。若为多层板,地平面应紧邻电源层,形成 “平面电容” 辅助退耦。

避免 “菊花链” 布线:多个电容不应串联或串接在同一走线上(会增加总寄生电感),而应各自独立连接到芯片的电源和地引脚,形成并行的退耦路径。

C、焊盘与封装:匹配电容尺寸,减少寄生参数

电容封装选择:优先用小封装电容(如 0402、0201),其自身寄生电感更小(比 0603、0805 封装低 50% 以上),更适合靠近芯片摆放。

焊盘设计:电容的焊盘尺寸应与封装匹配,避免过大或过小;焊盘到芯片引脚的铜皮宽度应足够(至少与引脚等宽),减少走线电阻和电感。

过孔数量:若电容需要通过过孔连接到内层电源 / 地平面,应增加过孔数量(如2个地过孔并联),降低过孔的寄生电感(过孔的电感约为 1-2nH / 个,并联可减半)。避免多个电容共用过孔。

D、分散布局:覆盖芯片所有电源引脚

若芯片有多个电源引脚(如四边都有 VCC/GND 引脚),退耦电容应分散布局在芯片四周,而非集中在某一侧。

例如,芯片的每个边都放置 1-2 个小电容(0.1μF)和 1 个中电容(1μF),确保每个电源引脚都能就近获取退耦电荷,避免 “远处引脚因路径过长导致退耦失效”。

总结:退耦电容布局的核心原则

近:所有电容尽可能靠近芯片电源 / 地引脚(小容值更近);

短:缩短电容到芯片的走线和接地路径,减小环路面积;

分:不同容值分层布局(小近大远),分散覆盖芯片各电源引脚;

低寄生:优化焊盘、过孔和平面设计,最小化电感和电阻。

案例:1个芯片2个退耦电容

遵守规则:

1近(环路面积小);

2短(缩短电容到芯片的走线和接地路径);

3低寄生:两个电容分别通过多个并联地过孔形成环路,即降低了降低过孔的寄生电感又避免了电容共用过孔引入的公共环路感抗。

五、电容去耦半径

A电容自谐振频率

自谐振频率(Self-Resonant Frequency,简称 SRF)是指实际电容(非理想电容)中,容抗与寄生电感的感抗相互抵消时的特定频率。在这一频率下,电容的整体阻抗达到最小值,是其滤波或退耦效果最佳的临界点。

理想电容仅由电容值(C)决定,但实际电容因封装、引脚、内部结构等因素,必然存在寄生电感(ESL,Equivalent Series Inductance) 和寄生电阻(ESR,Equivalent Series Resistance)。三者构成串联电路:

容抗(电容的阻碍作用):XC=1/2πfC,随频率升高而减小。

感抗(寄生电感的阻碍作用):XL=2πf⋅ESL,随频率升高而增大。

当频率升高到某一值时,XC=XL,两者大小相等、方向相反,相互抵消,此时电路总阻抗仅由ESR决定(达到最小值),这个频率就是自谐振频率。

B去耦半径对高频噪声的影响

电容去耦的一个重要问题是电容的去耦半径。前文是从减小回路电感的角度提及电容摆放要尽量靠近芯片、摆放距离问题。

减小电感是一个重要原因,但是还有一个重要的原因就是电容去耦半径问题。如果电容摆放离芯片过远,超出了它的去耦半径,电容将失去它的去耦的作用。

理解去耦半径最好的办法就是考察噪声源和电容补偿电流之间的相位关系。当芯片对电流的需求发生变化时,会在电源平面的一个很小的局部区域内产生电压扰动,电容要补偿这一电流(或电压),就必须先感知到这个电压扰动。信号在介质中传播需要一定的时间,因此从发生局部电压扰动到电容感知到这一扰动之间有一个时间延迟。同样,电容的补偿电流到达扰动区也需要一个延迟。因此必然造成噪声源和电容补偿电流之间的相位上的不一致。

当扰动区到电容的距离达到时,补偿电流的相位为,和噪声源相位刚好差180度,即完全反相。此时补偿电流不再起作用,去耦作用失效,补偿的能量无法及时送达。为了能有效传递补偿能量,应使噪声源和补偿电流的相位差尽可能的小,最好是同相位的。距离越近,相位差越小,补偿能量传递越多,如果距离为0,则补偿能量百分之百传递到扰动区。

特定的电容,对与它自谐振频率相同的噪声补偿效果最好,我们以这个频率来衡量这种相位关系。

补偿电流的传播本质上是电磁波(交变电流)在电路板介质中的传播,其表达式需结合自谐振频率f、波长λ及传播延迟的相位关系。设补偿电流的幅值为I0,传播距离为d(即电容到芯片噪声源的距离),则补偿电流的表达式可写为:

I补偿(d,t)=I0 sin(2πft-2πd/λ)

参数含义:

I0:补偿电流的最大幅值(由电容容量、ESR 等决定);

f:自谐振频率(与电容的C和ESL相关,f=2πC⋅ESL1);

λ:自谐振频率对应的波长(λ=v/f,其中v为电磁波在电路板介质中的传播速度,约为c/√(ε_r ),c为光速,ε_r为介质相对介电常数);

d:电容到芯片的距离(即传播路径长度);

第二项2πd/λ:补偿电流传播距离d后的相位延迟(波传播单位距离的相位变化为2π/λ)。

物理意义:

补偿电流是随时间变化的交变电流,其相位不仅与时间相关(2πft),还与传播距离d相关(相位延迟2πd/λ)。当d过大时,相位延迟会导致补偿电流与芯片的噪声电流(扰动电流)相位差增大:

若d≪λ/50:相位延迟极小(≪π/25),补偿电流与噪声电流近似同相,能量补偿效率最高(符合退耦半径要求);

若d≈λ/4:相位延迟接近π/2,补偿电流与噪声电流相位差显著,补偿效果大幅下降;

若d≥λ/4:相位延迟超过π/2,补偿电流甚至可能与噪声电流反相,反而加剧噪声(此时电容失效)。

因此,该表达式直观体现了 “距离越近(d越小),相位延迟越小,补偿效果越好” 的核心原则,也解释了为何退耦电容必须控制在 “退耦半径”(通常λ/40∼λ/50)内。

电容退耦半径=谐振频率对应波长/(40–50)=λ/(40–50)

例如:0.001uF陶瓷电容,如果安装到电路板上后总的寄生电感为1.6nH,那么其安装后的谐振频率为125.8MHz,谐振周期为7.95ps。假设信号在电路板上的传播速度为166ps/inch,则波长为47.9英寸。电容去耦半径为47.9/50=0.958英寸,大约等于2.4厘米。

本例中的电容只能对它周围2.4厘米范围内的电源噪声进行补偿,即它的去耦半径2.4厘米。

光速=频率*波长

不同的电容,谐振频率不同,去耦半径也不同。对于大电容,因为其谐振频率很低,对应的波长非常长,因而去耦半径很大,这也是为什么我们不太关注大电容在电路板上放置位置的原因。为了避免充放电电流流过整板,通常把大电容放在电源入口处。

对于小电容,因去耦半径很小,应尽可能的靠近需要去耦的芯片。

六、接地

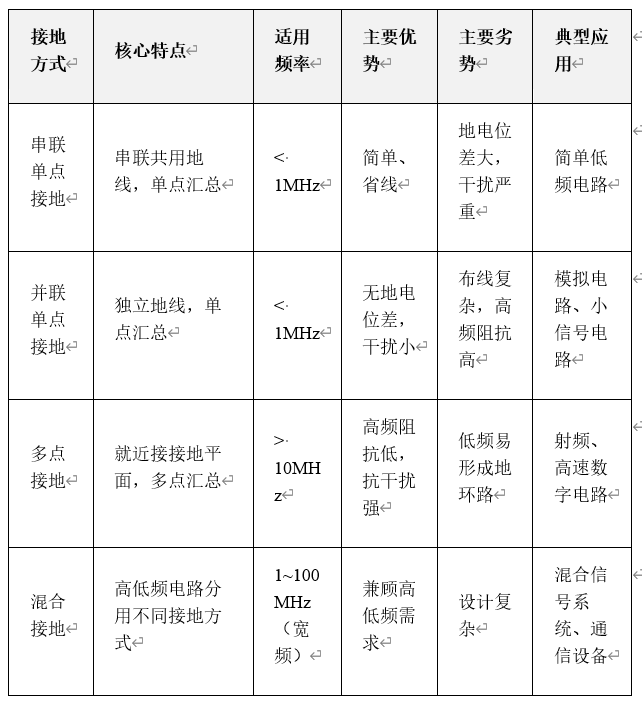

在电子系统设计中,接地方式直接影响系统的抗干扰能力和稳定性。常见的接地方式包括串联单点接地、并联单点接地、多点接地、混合接地,它们各有适用场景和优缺点,具体如下:

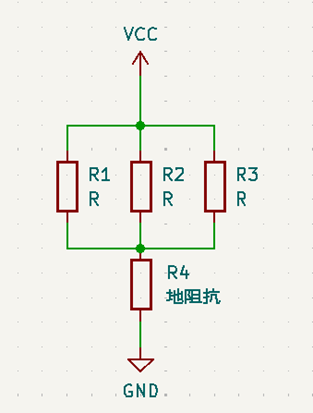

1、串联单点接地(Series Single-Point Grounding)

所有电路模块的接地端通过一条公共接地线串联连接,最终汇总到一个单点接地参考点(如电源地或机壳地)。

**优点:**结构简单,布线方便,节省导线和空间。

**缺点:**接地线存在电阻,各模块的接地电流会在公共线上产生电压降(U=I⋅R),导致不同模块的 “地电位” 不一致(地环路干扰)。

某一模块的噪声电流会通过公共地线耦合到其他模块(如大功率模块干扰小信号模块)。

适用场景

低频电路(通常 < 1MHz),且各模块功率差异小、对噪声敏感程度低的简单系统(如玩具、低端消费电子)。

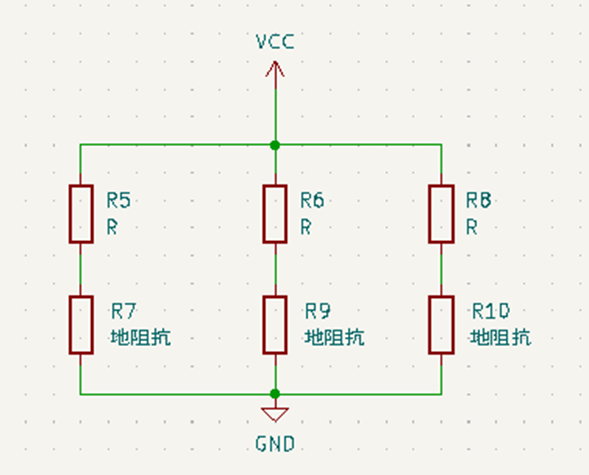

2、并联单点接地(Parallel Single-Point Grounding)

每个电路模块的接地端通过独立的接地线,直接连接到同一个公共接地参考点,各模块接地线互不串联。

优点:各模块接地线独立,避免了串联接地的 “地电位差” 问题,减少模块间的噪声耦合。小信号模块和大功率模块可分开布线,降低干扰风险。

*缺点:*接地线数量多,布线复杂,尤其在高密度电路中可能增加布局难度。高频时,长接地线会引入寄生电感,导致接地阻抗增大,干扰信号易通过地线辐射。

适用场景

低频电路(通常 < 1MHz),且模块间干扰敏感(如模拟电路、小信号电路),需避免地电位差的场景。

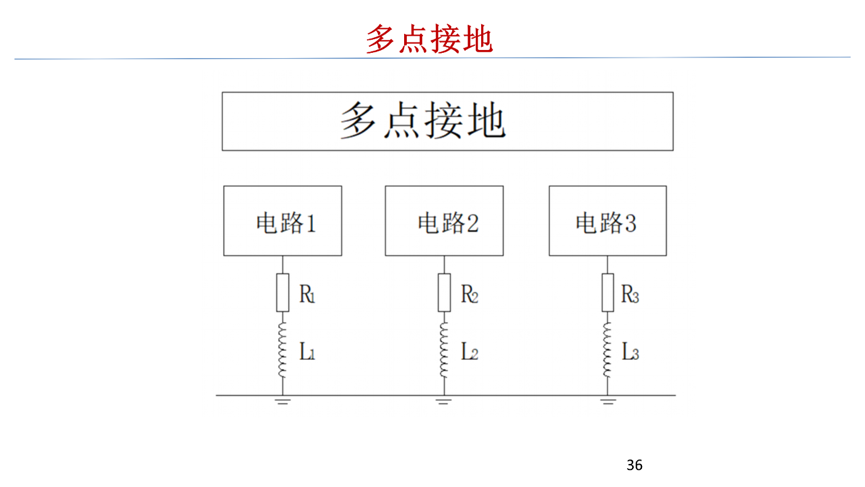

3、多点接地(Multi-Point Grounding)

每个电路模块(或设备)的接地端通过最短路径直接连接到就近的接地平面(如金属机壳、接地层),形成多个接地参考点,最终通过接地平面汇总。

***优点:***接地线短,寄生电感小,高频下接地阻抗低(接地平面的阻抗接近理想地)。能有效抑制高频噪声(> 10MHz)的辐射和传导干扰,适合高速信号电路。

***缺点:***低频时,多个接地点可能形成 “地环路”(不同接地点间的电位差通过环路产生干扰电流)。需设计专门的接地平面(如 PCB 的接地层),增加设计和制造成本。

适用场景

高频电路(通常 > 10MHz),如射频电路、高速数字电路(CPU、DDR)、大功率设备等。

4、混合接地(Hybrid Grounding)

定义

结合单点接地和多点接地的优势,针对系统中不同频率的电路采用不同接地方式:

低频电路(< 1MHz)采用单点接地(避免地环路);

高频电路(> 10MHz)采用多点接地(降低高频阻抗);

中间频段(1~10MHz)通过电感、电容等元件实现 “选择性接地”(如高频时电容导通就近接地,低频时电感断开避免环路)。

***优点:***兼顾高低频电路的需求,最大限度减少干扰,是复杂系统(如通信设备、医疗仪器)的常用方案。

***缺点:***设计复杂,需精确分析电路频率特性,合理选择接地元件(如穿心电容、高频电感)。

适用场景

混合信号系统(同时包含模拟电路和数字电路)、宽频带设备(如示波器、通信基站)等。

5、四种接地方式对比表

6、接地方法的选择

1.模拟电路由于信号波动很小,同时为了减小布线难度可以选择串联单点接地。但对于高精度应用场合,或者回流信号有较大波动的模拟电路,:也可以考虑采用并联单点接地。

2.数字电路虽然信号波动幅度较大,但数字电路本身对干扰有定的容忍度,所以各个数字电路之间也可以采用串联单点接地但要注意各个数字电路本身要采用多点接地,也就是就近接地,这样可以减小信号环路面积,从而减小电磁干扰。

3.数字电路与模拟电路之间采用并联单点接地,以减小数字电路对模拟电路的干扰。

七、PCB设计原则:

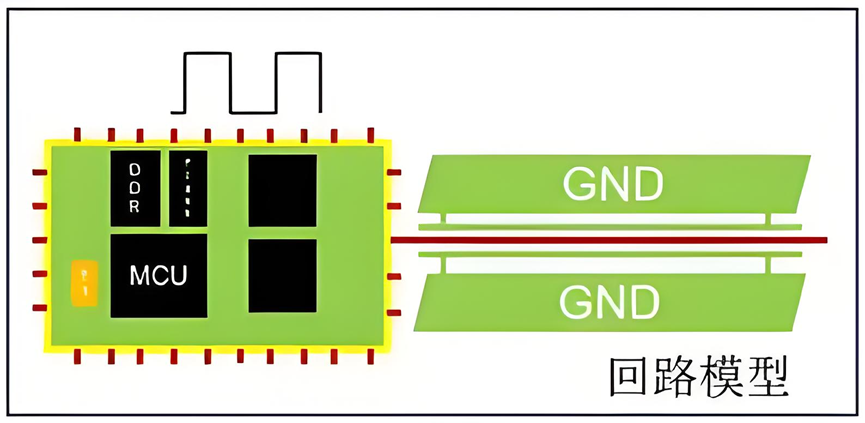

1、尽可能保留完整地平面:

在布线区域保留一个完整的导电平面(低阻抗平面)在其上方任意走线,电流都能自动得找到最小环路回流路径(在信号线正下方)!

完整地平面是高频、高速电路的 “基石”,其核心价值在于通过低阻抗、短路径、强屏蔽三大特性,解决接地噪声、信号完整性(SI)和电磁兼容性(EMC)问题。设计时需优先保证地平面的连续性,仅在低频、强干扰隔离等特殊场景下考虑分割地平面,并通过合理的连接方式(如单点连接)减少分割带来的负面影响。

提供低阻抗接地参考

完整地平面的电阻和寄生电感极低(大面积铜箔的电阻趋近于 0,且平面结构分散了电感),能确保电路中各点的 “地电位” 基本一致,避免因接地阻抗导致的信号失真或模块间干扰(如地电位差引起的共模噪声)。

优化信号回流路径

根据电磁理论,高频信号的回流会优先选择 “与信号线平行且最近的导体”。完整地平面与信号线紧密耦合,使回流路径最短(几乎与信号线重叠),显著降低信号回路的电感和电磁辐射(EMI),同时减少信号间的串扰(Crosstalk)。

电磁屏蔽作用

对下方电路:地平面可阻挡上方信号线产生的电磁辐射向下泄露。

对上方电路:地平面可隔离下方电源平面或噪声源产生的电磁干扰(EMI),起到 “屏蔽层” 作用。(若配合电源平面,形成 “地 - 电源” 平面对,可进一步增强屏蔽效果)。

散热功能

大面积铜箔的导热性优良,可作为散热路径,帮助功率器件(如芯片、电源模块)散发热量,降低温度对电路性能的影响。

2、时钟信号线必须包地

单层板或双层板上的时钟建议尽可能在时钟线的两侧包地线,条件不允许,也应该使时钟线和地线紧邻走线,即时钟线的一侧起码有地线,以减小时钟线的回流面积,减小差模辐射。

3、3W原则和10W原则

3W原则:导线中心间距为线宽3倍以上时,可以避开70%的电场耦合;

10W原则:导线中心间距为线宽10倍以上时,可以避开98%的电场耦合;

4、20H原则

在设计高速PCB板时,由于电源层与地层之间的电场是变化的,在板的边缘会向外辐射电磁干扰。称为边沿效应。解决的办法是将电源层内缩,使得电场只在接地层的范围内传导。以一个H(电源和地之间的介质厚度)为单位,若内缩20H则可以将70%的电场限制在接地层边沿内;内缩100H则可以将98%的电场限制在内。

5、走线宽度保持一致

直角、锐角走线是PCB设计中需尽量避免的结构,其核心问题源于“几何形状导致的信号路径异常”和“寄生参数突变”,具体影响如下:

1.阻抗不连续与信号反射

高频信号的传输依赖阻抗连续(如 50Ω 微带线),而直角走线的物理结构会破坏这种连续性:

直角拐角处的导线等效宽度增加(拐角内侧的 “突出部分” 相当于线宽变宽),导致该区域的特性阻抗突然下降(通常下降 10%-20%)。

阻抗突变会引发信号反射(反射系数增大),导致波形失真(如过冲、振荡),尤其在 1GHz 以上高频场景中,反射可能使信号眼图闭合,影响通信可靠性。

示例:10Gbps 高速信号通过直角拐角时,阻抗从 50Ω 骤降至 40Ω,反射系数约为 0.11,反射信号会与原信号叠加,导致上升沿 / 下降沿出现震荡。

2.寄生电容增大与信号延迟

直角拐角处的“突出铜皮”会增加与参考平面(地 / 电源层)之间的寄生电容(C):

电容计算公式为C=εS/d(S为面积,d为线到参考平面距离),直角拐角的额外面积会使电容比直走线增加5%-15%(典型值0.05-0.2pF)。

高频下,电容会表现为“容性负载”,延缓信号的跳变速度(上升沿/下降沿变缓),增加信号延迟,对时序敏感的信号(如DDR的DQS信号)可能导致时序违例。

3.电磁辐射(EMI)增强

直角拐角是EMI的潜在源头:

信号在拐角处的电流路径发生90°转折,形成“尖角”,根据电磁理论,尖角处的电场/磁场强度会集中(类似天线的尖端效应),导致额外的电磁波辐射。

辐射强度与信号频率的平方成正比,在GHz级高频场景中,直角拐角的辐射可能超过EMC标准(如FCC、CE),干扰周边敏感电路(如射频模块、模拟传感器)。

4.低频信号的影响可忽略

对低频信号(如≤10MHz的模拟信号、直流电源),直角走线的影响几乎可以忽略:此时信号波长较长(如10MHz波长为30m),拐角的物理尺寸远小于波长,阻抗突变和辐射的影响微乎其微。

6、高频信号和敏感信号走线过孔不宜过多

过孔具有对地电容和串连电感,对于高频信号和敏感信号有显著影响。

1.阻抗不连续与信号反射

高频信号的阻抗(如微带线阻抗通常设计为 50Ω 或 75Ω)需要全程连续才能避免反射。而过孔的结构(包括孔壁、焊盘、反焊盘)会引入额外的寄生参数:

寄生电感:过孔的孔长(板厚)和直径决定了电感量(典型值 0.5-2nH),高频信号(如 1GHz)的波长较短,电感会导致阻抗突变(过孔处阻抗可能偏离设计值 20% 以上),引发信号反射,导致波形失真(如上升沿变缓、振荡)。

寄生电容:过孔焊盘与参考平面(地或电源层)之间会形成电容(典型值 0.2-0.5pF),在高频下会表现为容性负载,进一步破坏阻抗匹配,甚至导致信号衰减。

示例:1GHz 信号通过一个 1nH 电感的过孔时,其感抗(Xₗ=2πfL≈6.28Ω)会使50Ω 传输线的阻抗突变至 56Ω 以上,反射系数增大,信号完整性下降。

2.增加信号路径长度与延迟

过孔本身的物理长度(从顶层到底层的孔长)会增加信号的传播路径。对高频信号(尤其是时序敏感的高速数字信号,如 DDR4、PCIe),额外的延迟可能导致时序违例(Setup/Hold 时间不满足)。

经验值:PCB 中信号传播速度约为 150ps/mm,一个 0.5mm 长的过孔会引入约 75ps 的额外延迟,对 10Gbps 以上的信号(单位间隔 UI≈100ps)而言,这一延迟可能占 UI 的 75%,严重影响时序。

3.电磁辐射与EMI风险

高频信号流经过孔时,由于阻抗不连续和寄生参数,会产生较强的电磁辐射:

过孔的“天线效应”:孔壁相当于一个短天线,高频电流(尤其是突变的开关电流)会通过过孔向空间辐射电磁波,成为EMI干扰源;

参考平面破坏:过孔的反焊盘(Anti-pad,为避免过孔与参考平面短路而预留的无铜区域)会在参考平面上形成 “孔洞”,若多个过孔密集排列,会导致参考平面 “开槽”(如前文所述),破坏信号的回流路径,回流电流被迫绕远,形成大环路,进一步加剧辐射。

4.对敏感信号的噪声耦合

敏感信号(如模拟传感器的小信号、音频信号、低电压差分信号 LVDS)本身抗干扰能力弱,而过孔是噪声耦合的“薄弱环节”:

过孔周围的电场/磁场变化(来自其他高频信号)易通过空间耦合干扰敏感信号;

若过孔穿过电源层或接地层的分割区域,会破坏参考平面的连续性,导致敏感信号的回流路径受阻,引入电源噪声或地噪声。

7、避免信号过孔密集排列产生的“开槽”

在PCB设计中,当信号过孔(Via)密集排列在参考平面(地平面或电源平面)上时,确实会产生类似“开槽(Slot)”的效果。这种现象本质是过孔对参考平面的连续性造成破坏,形成物理上的不连续区域,进而影响信号回流路径和电磁兼容性(EMC)。

“过孔密集排列产生开槽效果” 的原理

参考平面(如地平面)的核心作用是为信号提供低阻抗回流路径。而过孔要实现层间连接,必须在参考平面上“打孔”——通过反焊盘(Antipad)与参考平面绝缘(避免短路)。反焊盘是参考平面上围绕过孔的圆形非导电区域(去除铜箔)。

当多个过孔密集排列时:

相邻过孔的反焊盘之间的铜箔会被“挤压”,若间距过小(小于反焊盘直径的1.5-2倍),相邻反焊盘的非导电区域会相互 “连通”,在参考平面上形成一条连续的、长条状的非导电区域(类似人工开槽)。

这种由密集过孔反焊盘连成的 “虚拟开槽”,会切断参考平面在该区域的连续性,导致信号回流路径被迫绕行。

“开槽效果” 的主要影响

***破坏信号回流路径:***高频信号的回流依赖参考平面的连续铜箔(遵循“最小路径原则”)。若参考平面被密集过孔“开槽”,回流电流无法直接通过开槽区域,只能从开槽边缘绕行,导致回路电感急剧增加(路径变长),进而引发信号完整性问题:

***增强电磁辐射(EMI)***回流路径绕行会使信号回路面积增大(回路面积是 EMI 辐射的关键因素),相当于一个“发射天线”,向外辐射电磁能量,导致 EMC 测试失败(如辐射骚扰超标)。

参考平面阻抗升高开槽区域的铜箔被去除,参考平面的导电面积减小,阻抗(尤其是高频下的感抗)上升,可能导致地/电源平面的噪声抑制能力下降,影响芯片供电稳定性。

相邻信号串扰增加开槽区域的电磁场分布紊乱,相邻信号线的耦合增强,易产生串扰(Crosstalk),尤其在高速并行总线(如LVDS、HDMI)中更明显。

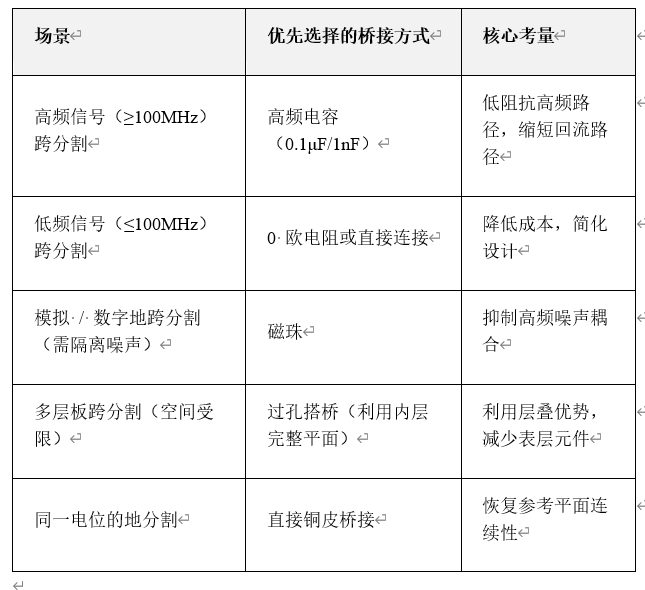

8、信号走线跨分割后的桥接方法

在 PCB 设计中,信号跨分割(Signal Crossing Split)指信号线从参考平面(电源或地平面)的一个分割区域(如 GND1)跨越到另一个分割区域(如 GND2 或 VCC)的现象。跨分割会切断信号的回流路径(回流电流无法通过分割处的参考平面),导致信号完整性(SI)恶化(如阻抗突变、反射)和电磁兼容性(EMC)问题(如辐射增强)。

**桥接(Bridging)**是解决跨分割的核心手段,其本质是为信号回流提供一条低阻抗的跨分割路径,弥补参考平面的不连续性。以下是常见的桥接方法,按适用场景和原理分类说明:

一、电容桥接(最常用的高频桥接方式)

利用电容的“隔直通交” 特性:在参考平面的分割处(如GND1与GND2之间、GND与VCC之间)并联高频电容(通常为0.1μF、1nF或10nF的陶瓷电容,如X7R材质),为高频信号的回流提供低阻抗路径(电容在高频下容抗极低,XC=1/(2πfC))。

适用场景

高频信号跨分割(如时钟、高速接口 DDR/PCIe/USB3.0等);

电源平面与地平面之间的跨分割(如信号从VCC1域跨到VCC2域);

不同地平面(如模拟地AGND与数字地DGND)之间的跨分割(需避免直流共地干扰时)。

关键设计要点

1. 电容选型:

容值:根据信号频率选择,确保电容自谐振频率(SRF)覆盖信号的主要频率成分(如100MHz信号可选1nF电容,其SRF约100MHz);

封装:优先选用0402、0201等小封装(寄生电感小),避免大封装(如0805)的引线电感削弱高频性能。

2. 摆放位置:

电容必须紧邻信号跨分割点(距离≤50mil,越近越好),确保回流路径最短(回流电流从跨分割点出发,通过电容跨到另一平面,再返回源端,总路径长度需远小于信号波长的 1/20);

电容的两个焊盘分别连接两个分割区域(如一端接 GND1,另一端接GND2),且焊盘与参考平面的连接需用短粗走线或直接铺铜(减少寄生电感)。

**3. 数量:**单条高速信号跨分割可放1-2个电容(避免多电容并联导致的谐振问题);并行总线(如 DDR)跨分割时,每2-4条信号线可共用一个电容(但需确保电容覆盖所有信号的跨分割点)。

二、0欧电阻/磁珠桥接(低频或需抑制噪声的场景)

0欧电阻:本质是“导线替代物”,为信号回流提供直流和低频的低阻抗路径(直流电阻接近 0),但高频下因寄生电感(约 1-5nH)阻抗升高,适合低频信号(≤100MHz)。

磁珠(Ferrite Bead):在特定频率范围内(如 10MHz-1GHz)呈现高阻抗,可抑制高频噪声通过桥接路径传导,同时为低频回流提供通路,适合需要隔离噪声的场景(如模拟信号跨数字地)。

适用场景

0欧电阻:低频信号(如 GPIO、低速 UART)跨地分割;同一电源域内的地分割(如 GND1 与 GND2 同属数字地,仅因布局分割)。

磁珠:模拟信号跨数字地(如ADC输入信号从AGND跨到DGND,抑制数字噪声耦合到模拟域);敏感电路(如射频前端)与其他区域的地分割桥接。

关键设计要点

摆放位置:与电容桥接相同,必须紧邻跨分割点,缩短回流路径;

封装选择:优先0402或更小封装(减少寄生电感);

注意磁珠的阻抗-频率特性:需匹配信号的噪声频率(如抑制100MHz噪声,选择100MHz时阻抗≥100Ω 的磁珠)。

三、参考平面直接连接(无隔离需求时)

若分割的参考平面属于同一电位(如GND1和GND2均为数字地,仅因布局布线临时分割),可直接用铜皮或宽走线将分割区域连接,形成 “桥接带”,恢复参考平面的连续性。

适用场景

同一地平面的临时分割(如因电源平面占位导致地平面被分成两部分);

低频信号跨分割且无噪声隔离需求(如电源地线的分割)。

关键设计要点

桥接带宽度:需足够宽(≥20mil),确保低阻抗(宽铜皮电阻和电感更低);

位置:桥接带需位于信号跨分割点的正下方(或紧邻跨分割路径),让回流电流直接通过桥接带,避免绕行;

避免在桥接带附近放置过孔(防止破坏桥接带的连续性)。

四、过孔搭桥(多层板跨层桥接)

在多层板中,若表层信号跨分割,可通过过孔将参考平面的分割区域在相邻内层连接(如表层GND1与GND2分割,内层GND是完整的,通过过孔将表层GND1与内层GND连接,表层GND2也与内层GND连接),利用内层完整参考平面作为“隐形桥”,让回流通过内层平面跨分割。

适用场景

多层板(≥4层)中表层或次表层信号跨分割;

不适合放置电容/电阻(空间受限)的高密度区域(如BGA周边)。

在多层板和双层板中,时钟线换层时,要求时钟线换层过孔附近必须要地层过孔存在。

关键设计要点

**过孔数量:**在跨分割点两侧各放置至少2-3个接地过孔(增加连接可靠性,降低阻抗);

**过孔位置:**紧邻信号跨分割点,确保从信号跨分割点到过孔的距离≤30mil(缩短表层到内层的回流路径);

**内层参考平面:**必须是完整的(无分割),且与跨分割的两个区域电位一致(如均为地平面)。

五、专用桥接走线(低频短距离跨分割)

当信号跨分割距离较短(≤500mil)且频率较低(≤50MHz)时,可在信号跨分割路径的旁边并行铺设一条宽走线(桥接走线),一端连接分割区A,另一端连接分割区B,作为回流路径的补充。

适用场景

低频低速信号(如按键、LED驱动信号);

空间极度受限,无法放置电容或过孔的场景。

关键设计要点

桥接走线需与信号走线平行且紧邻(间距≤信号走线宽度的 2 倍),形成 “信号 - 回流” 的紧密耦合,减少回路面积;

桥接走线宽度≥信号走线宽度的 2 倍(降低阻抗);

长度越短越好(避免高频下走线电感过大)。

六、桥接方法的选择原则