基于32nm CMOS工艺的传输门D触发器设计及HSPICE仿真分析

大家好,本文带来的是,根据半导体集成电路、利用Hspice软件以及数字电路等课程的知识,使用集成电路CMOS工艺完成触发器的设计。一起来看看!!!

一、设计任务和要求

根据半导体集成电路、利用Hspice软件以及数字电路等课程的知识,使用集成电路CMOS工艺完成触发器的设计,熟悉和掌握集成电路芯片电路设计及模拟方法和技巧。

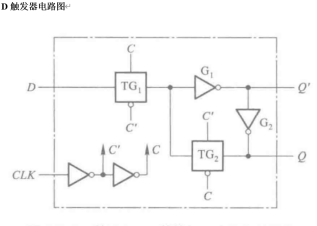

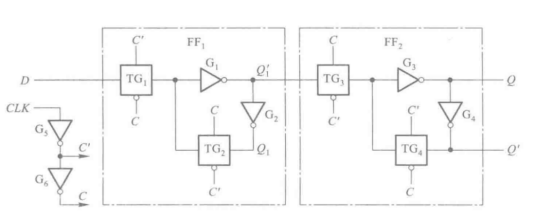

1、设计如图1所示用传输门构成的电平触发D触发器,和图2所示的边沿触发器

2、写出详细的电路原理分析;

3、编写Hspice网表文件,采用32nm的工艺;

4、进行电路瞬态波形仿真分析,进行功能验证;

5、改变负载,进行瞬态波形模拟,进行性能分析;

6、测量电路的功耗和延时,进行性能分析;

7、改变管子的尺寸,W或者L,再次进行瞬态波形,负载能力和功耗延时的测量和分析;

二、设计思路和方案

2.1传输门构成的D触发器

传输门(TG)就是一种传输模拟信号的模拟开关。CMOS传输门由一个P沟道和一个N沟道增强型MOSFET并联而成。TG的左边是输入端,右边是输出端。上边是控制信号C’输入端,下边是控制信号C输入端。

当C’=0、C=1时,TG导通,输出端的信号等于输入端信号。

当C=0、C’=1时,俩个MOS管栅极与衬底之间的压差为0V压降,因而没有导电沟道产生,NMOS管和PMOS管此时都处于截止状态。

传输门构成的D触发器,当CLK = 1 时, 传输门TG1,导通、TG2 截止, Q= D 。而且,在CLK= 1 的全部时间里Q 端的状态始终跟随D 端的状态而改变。

在CLK 回到0 以后, TG2 导通、TG1 截止。由于反相器G1输人电容的存储效应, 短时间内G1输入端仍然保持为TG1截止以前瞬间的状态、而且这时反相器G1 、G2 和传输门TG2 形成了状态自锁的闭合回路, 所以Q和Q ’ 的状态被保存下来。

2.2边沿触发器

当CLK=0时,TG1导通、TG3截止,此时FF1正常工作,FF2处于锁存状态若输入D=0,则Q1’=1,Q=0;当CLK跳变到1时,FF1锁存,FF2正常工作,此时Q跳变为0;因为FF1处于状态,所以Q1’的值保持不变,即Q的值也不变;当下降沿到来时,FF1工作、FF2锁存Q依旧不变,所以呈现出了边沿触发的特性,而且是上升沿触发。

三、网表文件和说明

(分模块介绍)

3.1传输门构成的D触发器

title inv4

.lib 'D:\PTM 32nm.lib' 32nmcmos_models

V1 1 0 dc=1//非门模块

.SUBCKT feimen 1 0 in out

Mp0 out in 1 1 pmos W=0.2u L=32n

Mn0 out in 0 0 nmos W=0.4u L=32n

.ENDS //传输们模块

.SUBCKT chuanshumen 1 0 in out clk clk1

mn1 in clk out 0 nmos w=0.2u l=32nm

mp1 in clk1 out 1 pmos w=0.2u l =32n

.ENDS//互连电路

X1 1 0 D A C C1 chuanshumen

X2 1 0 A Q1 feimen

X3 1 0 Q1 Q feimen

X4 1 0 A Q C1 C chuanshumen

X5 1 0 CLK C1 feimen

X6 1 0 C1 C feimenV2 CLK 0 pulse(0 1 0.1u 0.1n 0.1n 1.3u 2.6u)

V3 D 0 pulse(0 1 0.1u 0.1n 0.1n 0.4u 0.8u)//负载驱动

.probe v(CLK) v(D) v(Q) v(QF)

C1 Q 0 cc

.param cc=0.005p

.data ccdata

cc 0.005p 0.05p 0.5p 5p

.enddata//功耗

.measure tran average_vdd_power

+AVG P(v1) from=0ns to=5u //延时

.measure D_Q_delay

+trig v(D) val=500mv fall=1

+targ v(Q) val=500mv fall=1

.tran 0.1n 5u sweep data=ccdata.

end

分析:该代码是一个基本的D触发器电路,其中包含四个反相器(fei)和两个个传输门(tg)构成的D触发器。V1定义了一个高电平的输入信号。V2和V3分别定义了时钟信号和D输入信号的脉冲信号。在.tran语句中,定义了仿真的时间范围和时间步长。在.probe语句中,定义了需要监测的信号,包括时钟信号、D输入信号、输出信号和反相输出信号。

3.2边沿触发器

.title inv4

.lib'D:\PTM 32nm.lib'32nmcmos_models

.global VDD GND//负载驱动

.data cv

cload

0.0005p

0.005p

0.05p

0.5p

5p

.enddata//非门模块

.subckt feimen in out GND VDD

mn1 out in GND GND nmos w=0.2u l=32nm

mp1 out in VDD VDD pmos w=0.4u l=32nm

.ends//传输门模块

.subckt chuanshumen in out C1 C2 GND VDD

mn1 in C2 out GND nmos w=0.2u l=32nm

mp1 in C1 out VDD pmos w=0.4u l=32nm

.endsVDD VDD 0 1//互连电路

x1 clk e1 GND VDD feimen

x2 e1 e2 GND VDD feimen

x3 D b e2 e1 GND VDD chuanshumen

x4 b g1 GND VDD feimen

x5 g1 g GND VDD feimen

x6 b g e1 e2 GND VDD chuanshumen

x7 g1 f e1 e2 GND VDD chuanshumen

x8 f q1 e2 e1 GND VDD chuanshumen

x9 f q GND VDD feimen

x10 q q1 GND VDD feimenC q GND cload

VIN1 D 0 PULSE(0 1 2n 0.0001n 0.0001n 8n 16n)

VIN2 CLK 0 PULSE(0 1 1n 0.0001n 0.0001n 4n 8n)//延时

.measure T_delay

+trig v(CLK) val=0.5 rise=1

+targ v(q) val=0.5 rise=1//功耗

.measure tran average_VDD_power AVG P(X1) from=0ns to=32ns.tran 1ns 32ns sweep data=cv

.END

分析:第一个传输门(tg)和第一个反相器(fei)构成一个D触发器,其中D输入通过传输门(tg)输入,输出通过反相器(fei)输出。第二个传输门(tg)和第二个反相器(fei)构成另一个D触发器,其中D输入通过反相器(fei)输入,输出通过传输门(tg)输出。两个D触发器的时钟信号共用,但是D输入信号分别通过不同的反相器(fei)输入。这种电路结构实现了两个D触发器的级联,并且能够实现更复杂的电路功能。

四、仿真与结果分析

4.1 功能仿真结果与分析

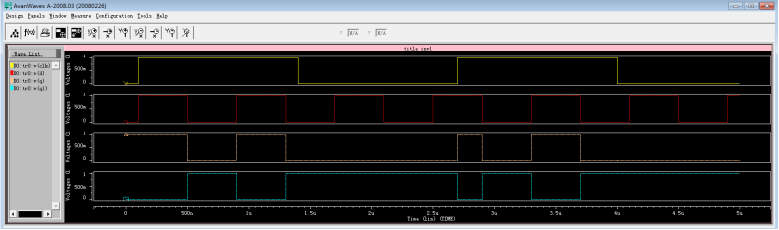

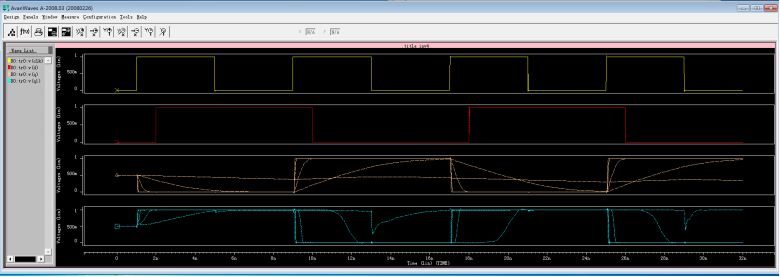

4.1.1 传输门构成的D触发器波形图

如图所示,在CLK=1时,D=Q,当CLK=0时,Q保持不变,满足电平D触发器的特性。

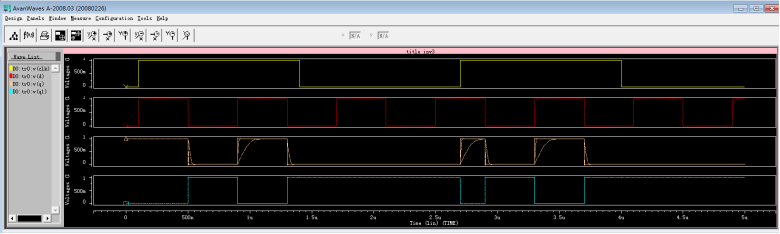

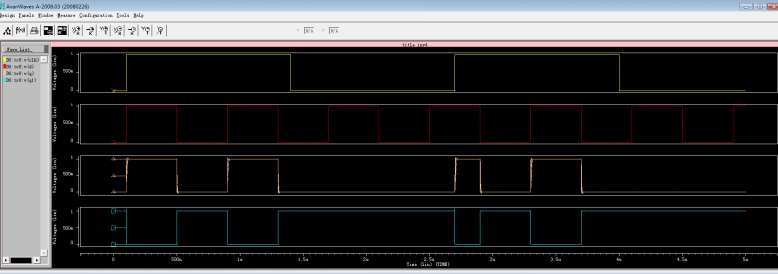

4.1.2 边沿触发器波形图

波形为上升沿触发,而且呈现D触发器特性,所以是一个上升沿触发的边沿D触发器。

4.2 负载驱动能力的仿真与分析

4.2.1 传输门构成的D触发器负载驱动能力波形图

随着加入负载的增加,功耗和延时不断加大,同时继续加大负载波形会产生失真。

4.2.2 边沿触发器负载驱动能力波形图

随着加入负载的增加,功耗和延时不断加大,同时继续加大负载波形会产生失真

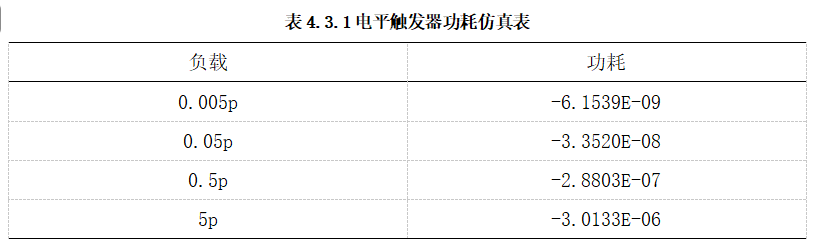

4.3 功耗的仿真与分析

4.3.1

基本符合随着负载电容的容值不断增大,电路的总功耗不断增大的规律。电路的响应时间受到负载电容的影响。当电路驱动较大的负载电容时,需要更多的电荷来使电容充电或放电到目标电平,从而导致输出信号的变化速度和稳定性下降。

4.3.2

随着负载电容的容值不断增大,电路的总功耗先减小后增大再减小。在逐步增加负载电容时,产生了显著的结果。这可能表明负载电容已经达到了某个关键点,继续增加负载电容可能导致电路响应时间显著延长、输出信号失真或出现稳定性问题。

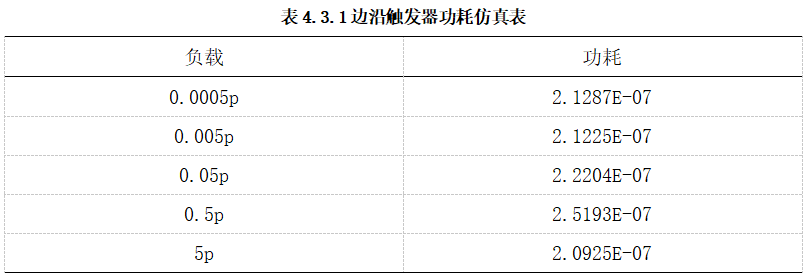

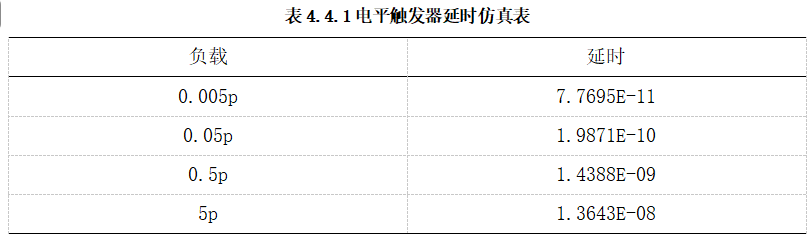

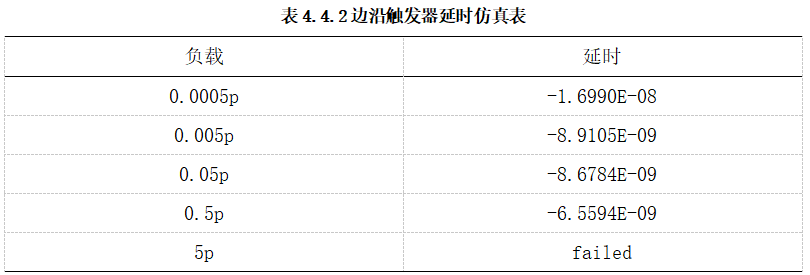

4.4 延时的仿真与分析

4.4.1

基本符合随着负载电容的容值不断增大,延时不断减小的规律。在仿真过程中,负载电容的增加意味着更多的电荷需要在电路中传输。根据电荷传输的基本原理,电荷通过电路的速度与电容成反比关系。因此,当电容增大时,电荷传输所需的时间会减少,从而导致延时减小。

4.4.2

从0.0005p到0.005p,不难发现,延时差距过大,说明负载不能过小。

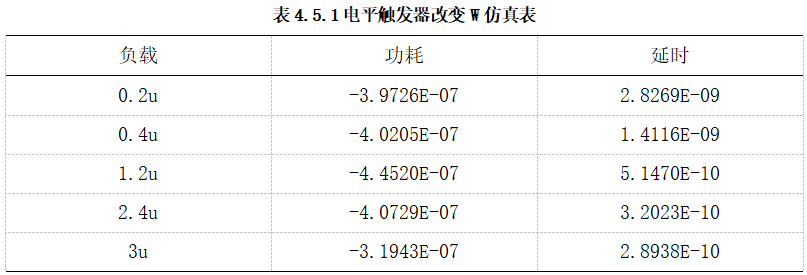

4.5 改变沟道W时的仿真与分析

4.5.1 传输门构成的D触发器波形图

沟道发生改变后,波形未出现明显的失真。

随着沟道的增加,功耗先增加后减小,延时不断减小。

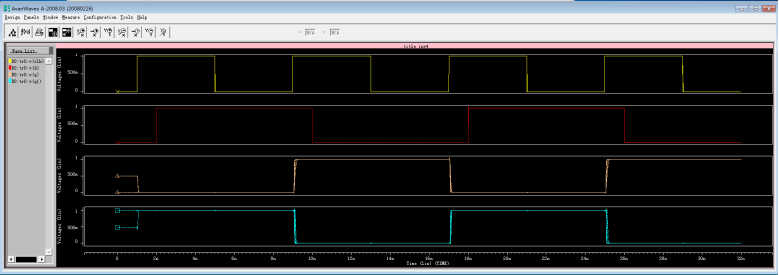

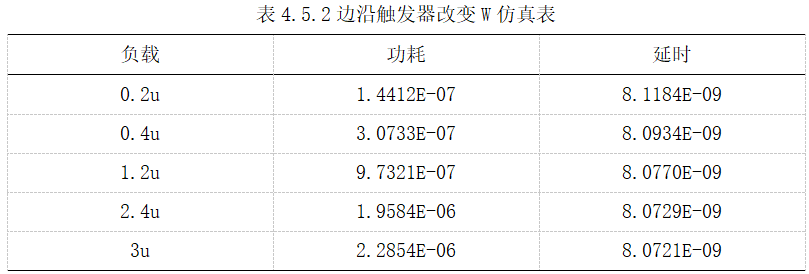

4.5.2 传输门构成的D触发器波形图

沟道发生改变后,波形未出现明显的失真。

随着沟道的增加,功耗不断变化,延时不断减小。

五、心得体会与总结

以上代码实现了一个基本的数字电路设计,其中包括传输门(Transmission Gate)、反相器(Inverter)。代码中使用了PTM 32nm的模型库,该模型库提供了对32纳米工艺的模拟支持。

在这个课程设计中遇到的问题,对我个人而言最困难的地方是熟练掌握HSPICE的用法,这个软件里是英文的,里面包含了许多功能,但是对初步接触的我来说显得很陌生。我在这里卡住了很久。当然起初琢磨虚拟机时也费了一些心思,因为没有系统的完整学习,所以只能边做边改,边做边学习。

先是环境配置中出了问题,我在网上查询资料,但是发现对这方面的介绍似乎不是很多,在此过程中也了解到市面上常用的几种EDA仿真软件。然后是代码撰写方面,开始并没意识到需要包含工艺库文件,以至于运行报错,不过后来想起来在虚拟机D盘中找到了32nm工艺库文件,并修正了代码路径。接着到了仿真阶段,查看波形,发现几个波形都挤在一张图标上,很不美观,试着在网上找到解决办法,未果,发现连关于HSPICE的使用方法介绍的都不是很多,或者说很直观。只能试着把软件中的每个窗口按钮功能试一遍,找到了window中的stack mode,成功把多个波形隔开查看。到此,发现背景中还有虚线,也是人海搜索,多次尝试后发现,右键后点击grid off即可消除背景虚线,到这里,我才终于把波形调整好,变得美观。

在心得体会方面,对HSPICE的用法有了大致的了解和学习,这是我收益最多的部分。经过这次实验仿真,我也从零基础变成了对该软件的用法有一定了解的学习者了。在整个学习过程中,了解到,随着现代科技的迅猛发展,对集成电路(IC)的需求日益增加,尤其是在人工智能、物联网、5G通讯等领域。全球范围内的技术竞争促使各国加大对半导体产业的投入,推动了集成电路设计的急需。在地缘政治紧张局势下,拥有独立的集成电路设计能力被视为国家安全的重要组成部分。

总而言之,在实践中学习了如何使用HSPICE进行建模和仿真。通过理解和掌握这样的设计方法和仿真工具,我们可以更好地理解和分析数字电路的工作原理和性能特点。同时也意识到集成电路设计的急迫性和重要性,同时,绿色设计在集成电路设计中愈发重要,不仅有助于保护环境,也符合未来科技发展的趋势。

六、附录:工程文档

6.1电平D触发器

title inv1

.lib 'D:\model\models\PTM 32nm.lib' 32nmcmos_models

V1 1 0 dc=1.SUBCKT feimen 1 0 in out

Mp0 out in 1 1 pmos W=0.2u L=32n

Mn0 out in 0 0 nmos W=0.4u L=32n

.ENDS .SUBCKT chuanshumen 1 0 in out clk clk1

mn1 in clk out 0 nmos w=0.2u l=32nm

mp1 in clk1 out 1 pmos w=0.2u l =32n

.ENDSX1 1 0 D A C C1 chuanshumen

X2 1 0 A Q1 feimen

X3 1 0 Q1 Q feimen

X4 1 0 A Q C1 C chuanshumen

X5 1 0 CLK C1 feimen

X6 1 0 C1 C feimenV2 CLK 0 pulse(0 1 0.1u 0.1n 0.1n 1.3u 2.6u)

V3 D 0 pulse(0 1 0.1u 0.1n 0.1n 0.4u 0.8u).tran 0.1n 5u

.probe v(CLK) v(D) v(Q) v(QF).end

6.2电平D触发器驱动能力检验

title inv3

.lib 'D:\model\models\PTM 32nm.lib' 32nmcmos_models

V1 1 0 dc=1.SUBCKT feimen 1 0 in out

Mp0 out in 1 1 pmos W=0.2u L=32n

Mn0 out in 0 0 nmos W=0.4u L=32n

.ENDS .SUBCKT chuanshumen 1 0 in out clk clk1

mn1 in clk out 0 nmos w=0.2u l=32nm

mp1 in clk1 out 1 pmos w=0.2u l =32n

.ENDSX1 1 0 D A C C1 chuanshumen

X2 1 0 A Q1 feimen

X3 1 0 Q1 Q feimen

X4 1 0 A Q C1 C chuanshumen

X5 1 0 CLK C1 feimen

X6 1 0 C1 C feimenV2 CLK 0 pulse(0 1 0.1u 0.1n 0.1n 1.3u 2.6u)

V3 D 0 pulse(0 1 0.1u 0.1n 0.1n 0.4u 0.8u).probe v(CLK) v(D) v(Q) v(QF)C1 Q 0 cc

.param cc=0.005p

.data ccdata

cc 0.005p 0.05p 0.5p 5p

.enddata.tran 0.1n 5u sweep data=ccdata

.end

6.3电平D触发器功耗仿真

title inv4

.lib 'D:\model\models\PTM 32nm.lib' 32nmcmos_models

V1 1 0 dc=1.SUBCKT feimen 1 0 in out

Mp0 out in 1 1 pmos W=0.2u L=32n

Mn0 out in 0 0 nmos W=0.4u L=32n

.ENDS .SUBCKT chuanshumen 1 0 in out clk clk1

mn1 in clk out 0 nmos w=0.2u l=32nm

mp1 in clk1 out 1 pmos w=0.2u l =32n

.ENDSX1 1 0 D A C C1 chuanshumen

X2 1 0 A Q1 feimen

X3 1 0 Q1 Q feimen

X4 1 0 A Q C1 C chuanshumen

X5 1 0 CLK C1 feimen

X6 1 0 C1 C feimenV2 CLK 0 pulse(0 1 0.1u 0.1n 0.1n 1.3u 2.6u)

V3 D 0 pulse(0 1 0.1u 0.1n 0.1n 0.4u 0.8u).probe v(CLK) v(D) v(Q) v(QF)C1 Q 0 cc

.param cc=0.005p

.data ccdata

cc 0.005p 0.05p 0.5p 5p

.enddata.measure tran average_vdd_power

+AVG P(v1) from=0ns to=5u .tran 0.1n 5u sweep data=ccdata

.end

6.4电平D触发器功耗延时仿真

title inv4

.lib 'D:\model\models\PTM 32nm.lib' 32nmcmos_models

V1 1 0 dc=1.SUBCKT feimen 1 0 in out

Mp0 out in 1 1 pmos W=0.2u L=32n

Mn0 out in 0 0 nmos W=0.4u L=32n

.ENDS .SUBCKT chuanshumen 1 0 in out clk clk1

mn1 in clk out 0 nmos w=0.2u l=32nm

mp1 in clk1 out 1 pmos w=0.2u l =32n

.ENDSX1 1 0 D A C C1 chuanshumen

X2 1 0 A Q1 feimen

X3 1 0 Q1 Q feimen

X4 1 0 A Q C1 C chuanshumen

X5 1 0 CLK C1 feimen

X6 1 0 C1 C feimenV2 CLK 0 pulse(0 1 0.1u 0.1n 0.1n 1.3u 2.6u)

V3 D 0 pulse(0 1 0.1u 0.1n 0.1n 0.4u 0.8u).probe v(CLK) v(D) v(Q) v(QF)C1 Q 0 cc

.param cc=0.005p

.data ccdata

cc 0.005p 0.05p 0.5p 5p

.enddata.measure tran average_vdd_power

+AVG P(v1) from=0ns to=5u

.measure D_Q_delay

+trig v(D) val=500mv fall=1

+targ v(Q) val=500mv fall=1

.tran 0.1n 5u sweep data=ccdata

.end

6.5电平D触发器改变沟道W时的仿真

title inv4

.lib 'D:\model\models\PTM 32nm.lib' 32nmcmos_models

V1 1 0 dc=1

.SUBCKT feimen 1 0 in out

Mp0 out in 1 1 pmos W=wu L=32n

Mn0 out in 0 0 nmos W=wu L=32n

.ENDS .SUBCKT chuanshumen 1 0 in out clk clk1

mn1 in clk out 0 nmos w=0.2u l=32nm

mp1 in clk1 out 1 pmos w=0.2u l =32n

.ENDSX1 1 0 D A C C1 chuanshumen

X2 1 0 A Q1 feimen

X3 1 0 Q1 Q feimen

X4 1 0 A Q C1 C chuanshumen

X5 1 0 CLK C1 feimen

X6 1 0 C1 C feimenV2 CLK 0 pulse(0 1 0.1u 0.1n 0.1n 1.3u 2.6u)

V3 D 0 pulse(0 1 0.1u 0.1n 0.1n 0.4u 0.8u).probe v(CLK) v(D) v(Q) v(QF)C1 Q 0 cc

.param cc=0.5p

.data cv

wu

0.2u 0.4u 1.2u 2.4u 3u

.enddata.measure tran average_vdd_power

+AVG P(v1) from=0ns to=5u

.measure D_Q_delay

+trig v(D) val=500mv fall=1

+targ v(Q) val=500mv fall=1

.tran 0.1n 5u sweep data=cv

.end

6.6边沿触发器

.title inv2

.lib 'D:\model\models\PTM 32nm.lib' 32nmcmos_models

.global VDD GND.subckt feimen IN OUT VDD GND

mn1 OUT IN GND GND nmos w=0.2u l=32n

mp1 OUT IN VDD VDD pmos w=0.4u l=32n

.ends.subckt chuanshumen IN OUT cl cl1 VDD GND

mn1 IN cl OUT GND nmos w=0.2u l=32n

mp1 IN cl1 OUT VDD pmos w=0.4u l=32n

.ends

X1 CLK C1 VDD GND feimen

X2 C1 C VDD GND feimen

X3 D B C1 C VDD GND chuanshumen

X4 B Q21 VDD GND feimen

X5 Q21 Q2 VDD GND feimen

X6 B Q2 C C1 VDD GND chuanshumen

X7 Q21 K C C1 VDD GND chuanshumen

X8 K Q VDD GND feimen

X9 Q Q1 VDD GND feimen

X10 K Q1 C1 C VDD GND chuanshumen

c1 Q 0 0.0001p

VDD VDD 0 1

VIN1 D 0 PULSE(0 1 2n 0.0001n 0.0001n 8n 16n)

VIN2 CLK 0 PULSE(0 1 1n 0.0001n 0.0001n 4n 8n)

.tran 1n 32n

.end

6.7边沿触发器驱动能力检验

.title inv4

.lib 'D:\model\models\PTM 32nm.lib' 32nmcmos_models

.global VDD GND

.data cv

cload

0.0005p

0.005p

0.05p

0.5p

5p

.enddata.subckt feimen in out GND VDD

mn1 out in GND GND nmos w=0.2u l=32nm

mp1 out in VDD VDD pmos w=0.4u l=32nm

.ends.subckt chuanshumen in out C1 C2 GND VDD

mn1 in C2 out GND nmos w=0.2u l=32nm

mp1 in C1 out VDD pmos w=0.4u l=32nm

.endsVDD VDD 0 1

x1 clk e1 GND VDD feimen

x2 e1 e2 GND VDD feimen

x3 D b e2 e1 GND VDD chuanshumen

x4 b g1 GND VDD feimen

x5 g1 g GND VDD feimen

x6 b g e1 e2 GND VDD chuanshumen

x7 g1 f e1 e2 GND VDD chuanshumen

x8 f q1 e2 e1 GND VDD chuanshumen

x9 f q GND VDD feimen

x10 q q1 GND VDD feimen

C q GND cload

VIN1 D 0 PULSE(0 1 2n 0.0001n 0.0001n 8n 16n)

VIN2 CLK 0 PULSE(0 1 1n 0.0001n 0.0001n 4n 8n)

.tran 1ns 32ns sweep data=cv

.END

6.8边沿触发器功耗和延时检验

.title inv4

.lib 'D:\model\models\PTM 32nm.lib' 32nmcmos_models

.global VDD GND

.data cv

cload

0.0005p

0.005p

0.05p

0.5p

5p

.enddata.subckt feimen in out GND VDD

mn1 out in GND GND nmos w=0.2u l=32nm

mp1 out in VDD VDD pmos w=0.4u l=32nm

.ends.subckt chuanshumen in out C1 C2 GND VDD

mn1 in C2 out GND nmos w=0.2u l=32nm

mp1 in C1 out VDD pmos w=0.4u l=32nm

.endsVDD VDD 0 1

x1 clk e1 GND VDD feimen

x2 e1 e2 GND VDD feimen

x3 D b e2 e1 GND VDD chuanshumen

x4 b g1 GND VDD feimen

x5 g1 g GND VDD feimen

x6 b g e1 e2 GND VDD chuanshumen

x7 g1 f e1 e2 GND VDD chuanshumen

x8 f q1 e2 e1 GND VDD chuanshumen

x9 f q GND VDD feimen

x10 q q1 GND VDD feimen

C q GND cload

VIN1 D 0 PULSE(0 1 2n 0.0001n 0.0001n 8n 16n)

VIN2 CLK 0 PULSE(0 1 1n 0.0001n 0.0001n 4n 8n).measure T_delay

+trig v(D) val=0.5 rise=1

+targ v(q) val=0.5 rise=1

.measure tran average_VDD_power AVG P(X1) from=0ns to=32ns.tran 1ns 32ns sweep data=cv

.END

6.9边沿触发器改变沟道

.title inv4

.lib 'D:\model\models\PTM 32nm.lib' 32nmcmos_models

.global VDD GND

.data cv

wu

0.2u

0.4u

1.2u

2.4u

3u

.enddata.subckt feimen in out GND VDD

mn1 out in GND GND nmos w=wu l=32nm

mp1 out in VDD VDD pmos w=wu l=32nm

.ends.subckt chuanshumen in out C1 C2 GND VDD

mn1 in C2 out GND nmos w=wu l=32nm

mp1 in C1 out VDD pmos w=wu l=32nm

.endsVDD VDD 0 1

x1 clk e1 GND VDD feimen

x2 e1 e2 GND VDD feimen

x3 D b e2 e1 GND VDD chuanshumen

x4 b g1 GND VDD feimen

x5 g1 g GND VDD feimen

x6 b g e1 e2 GND VDD chuanshumen

x7 g1 f e1 e2 GND VDD chuanshumen

x8 f q1 e2 e1 GND VDD chuanshumen

x9 f q GND VDD feimen

x10 q q1 GND VDD feimen

C q GND 0.005p

VIN1 D 0 PULSE(0 1 2n 0.0001n 0.0001n 8n 16n)

VIN2 CLK 0 PULSE(0 1 1n 0.0001n 0.0001n 4n 8n).measure T_delay

+trig v(D) val=0.5 rise=1

+targ v(q) val=0.5 rise=1

.measure tran average_VDD_power AVG P(X1) from=0ns to=32ns.tran 1ns 32ns sweep data=cv

.END