STM32的时钟系统与时钟树的配置

STM32的时钟系统是其微控制器(MCU)的核心组成部分,负责为CPU、外设和存储器等模块提供精确的时序信号。其设计灵活且复杂,通过多级时钟树(Clock Tree)实现时钟源的选择、分频和分配。以下是详细介绍:

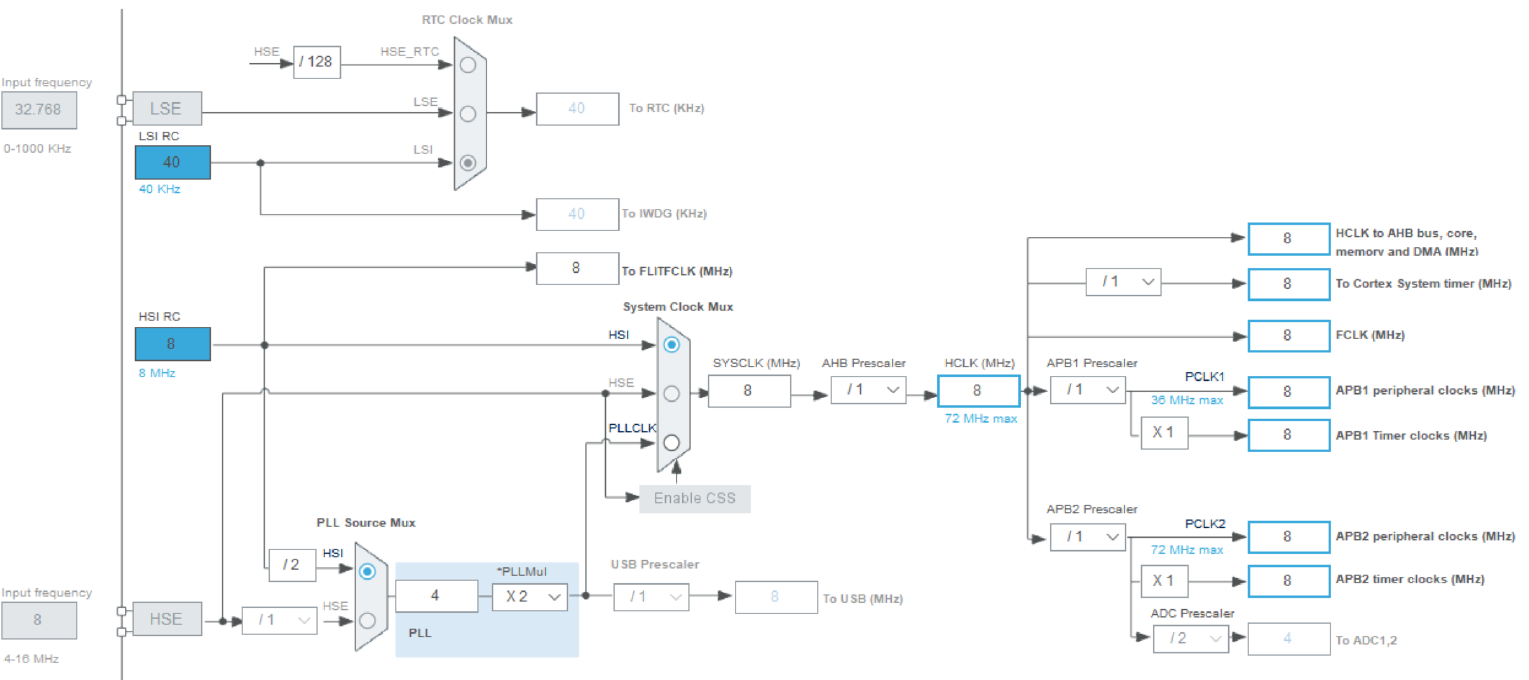

一、STM32时钟系统的核心概念

- 时钟源(Clock Source)

STM32提供多种时钟源,通常包括:- HSI(High-Speed Internal Oscillator):内部高速RC振荡器,频率通常为8MHz(部分型号为16MHz),启动快但精度低(±1%~2%)。

- HSE(High-Speed External Oscillator):外部高速晶振,频率范围广(4~26MHz,部分型号支持更高),精度高(±0.1%~0.01%)。

- LSI(Low-Speed Internal Oscillator):内部低速RC振荡器,频率约32kHz,用于独立看门狗(IWDG)或RTC备用时钟。

- LSE(Low-Speed External Oscillator):外部低速晶振,频率通常为32.768kHz,专为RTC(实时时钟)设计,精度高。

- PLL(Phase-Locked Loop):锁相环,可将输入时钟倍频(如将HSE的8MHz倍频至72MHz),提供更高频率的主时钟。

- 时钟树(Clock Tree)

STM32的时钟信号通过多级分频和选择器分配到不同模块,形成树状结构。时钟树的主要功能包括:- 时钟源选择:通过寄存器配置选择HSI、HSE或PLL作为系统时钟。

- 分频控制:对时钟信号进行预分频(Prescaler),以适应不同外设的频率需求。

- 时钟分配:将分频后的时钟分配到CPU、APB总线、外设等模块。

二、STM32时钟树的关键路径

以STM32F1系列为例,时钟树的主要路径如下:

- 系统时钟(SYSCLK)

- 来源:HSI、HSE或PLL。

- 作用:为CPU核心、AHB总线(高速总线)和内存提供时钟。

- 配置:通过RCC_CFGR寄存器的

SW位选择时钟源。

- AHB总线时钟(HCLK)

- 来源:SYSCLK经过AHB预分频器(AHB Prescaler)分频。

- 作用:驱动AHB总线上的外设(如DMA、GPIO)和APB预分频器。

- 分频系数:通过RCC_CFGR寄存器的

HPRE位配置(1~512分频)。

- APB总线时钟(PCLK1/PCLK2)

- 来源:HCLK经过APB预分频器分频。

- 作用:

- PCLK1:驱动低速外设(如USART2、TIM2~TIM7)。

- PCLK2:驱动高速外设(如USART1、TIM1、ADC)。

- 分频系数:通过RCC_CFGR寄存器的

PPRE1和PPRE2位配置(1~16分频)。

- 外设时钟

- 每个外设通过独立的时钟使能位(如

RCC_APB2ENR中的USART1EN)控制是否启用时钟。 - 外设实际工作频率可能经过二次分频(如USART的波特率分频)。

- 每个外设通过独立的时钟使能位(如

- PLL时钟

- 输入源:HSI/2或HSE(可配置是否经过分频)。

- 倍频系数:通过RCC_CFGR寄存器的

PLLMUL位配置(2~16倍频)。 - 输出:PLLCLK可作为SYSCLK或USB、RTC等专用时钟源。

三、先把“时钟”想象成“城市供水系统”

水源(振荡器) → 水库/水井

水管网(时钟树) → 主管→支管→入户

水表(预分频器) → 控制每户水压

用水设备(CPU、外设) → 厨房、浴室、花园……

STM32 的时钟树就是一套多级“供水系统”:

先选水源 → 经过开关/阀门(Mux) → 加压站(PLL) → 各级减压阀(Prescaler) → 最终送到每家每户。

四、图片里出现的“水源”逐个讲解

| 名字 | 频率 | 类型 | 作用 | 比喻 |

|---|---|---|---|---|

| HSI RC | 8 MHz | 内部 RC 振荡器 | 上电默认水源,省晶振 | 自家院子里的手压井 |

| HSE | 4-16 MHz(常用 8 MHz) | 外部晶振/时钟 | 精度高,可倍频到 72 MHz | 城市自来水厂 |

| LSI RC | 40 kHz | 低速内部 RC | 独立看门狗 IWDG、RTC 低功耗计时 | 备用小水桶 |

| LSE | 32.768 kHz | 32.768 kHz 外部晶振 | RTC 精准日历时钟 | 标准石英钟 |

| PLLCLK | ≤72 MHz | PLL 倍频输出 | 把 HSI/HSE 放大,给 CPU 和高速外设 | 加压泵站 |

五、时钟树的流向(对照图片箭头)

SYSCLK(总水源)

由 HSI / HSE / PLLCLK 三选一决定,最大 72 MHz。

图中“SYSCLK (MHz)”就是最终给 CPU 喝的“主水管”。HCLK(主管道)

SYSCLK → AHB Prescaler(1、2、4…512 分频)→ HCLK

给 AHB 总线、CPU 核心、内存、DMA 使用。

图中“HCLK (MHz)”就是这条主管的水压。PCLK1 / PCLK2(两条支管)

HCLK → APB1 Prescaler → PCLK1(≤36 MHz)

挂在 APB1 的外设:USART2/3、I²C1/2、SPI2、TIM2~4…HCLK → APB2 Prescaler → PCLK2(≤72 MHz)

挂在 APB2 的外设:GPIO、USART1、SPI1、TIM1、ADC1/2…

图中 APB1、APB2 后面分别标注了“8 MHz、72 MHz max”。

专用小水管

ADC 时钟:PCLK2 → ADC Prescaler(2/4/6/8)→ 4~18 MHz

USB 时钟:PLL 直接 48 MHz 分支(图上 USB (MHz) 48)

RTC 时钟:LSE(32.768 kHz) / LSI(40 kHz) / HSE/128 三选一,图上“RTC Clock Mux”

独立看门狗 IWDG:固定 LSI 40 kHz

SysTick:可以走 HCLK 或 HCLK/8,给操作系统节拍用。

六、把数字换成“水压值”(一个常见配置举例)

| 节点 | 实际计算 | 结果 |

|---|---|---|

| HSE | 8 MHz 晶振 | 8 MHz |

| PLL | 8 MHz × 9 | 72 MHz |

| SYSCLK | 选 PLL | 72 MHz |

| HCLK | AHB 不分频 | 72 MHz |

| PCLK1 | 72 / 2 | 36 MHz(APB1 最大) |

| PCLK2 | 72 / 1 | 72 MHz(APB2 最大) |

| ADC | 72 / 6 | 12 MHz |

| USB | PLL / 1.5 | 48 MHz(固定) |

| RTC | 选 LSE | 32.768 kHz |